## Rochester Institute of Technology

# **RIT Digital Institutional Repository**

Theses

2004

# Embedded charge for microswitch applications

Joanna Kiljan

Follow this and additional works at: https://repository.rit.edu/theses

#### **Recommended Citation**

Kiljan, Joanna, "Embedded charge for microswitch applications" (2004). Thesis. Rochester Institute of Technology. Accessed from

This Thesis is brought to you for free and open access by the RIT Libraries. For more information, please contact repository@rit.edu.

# **Embedded Charge for Microswitch Applications**

By

Joanna Kiljan

A Thesis Submitted

#### in Partial Fulfillment

#### of the Requirements for the Degree of

Master of Science

In

Microelectronics Engineering

Approved by:

Dr. Karl D. Hirschman \_\_\_\_\_\_ (Thesis Advisor)

Dr. Alan Raisanen (Committee Member)

Dr. Santosh K. Kurinec \_\_\_\_\_\_(Department Head)

DEPARTMENT OF MICROELECTRONICS ENGINEERING COLLEGE OF ENGINEERING ROCHESTER INSTITUTE OF TECHNOLOGY ROCHESTER, NEW YORK

DECEMBER, 2004

# **Embedded Charge for Microswitch Applications**

By

Joanna Kiljan

I, Joanna Kiljan, hereby grant permission to the Wallace Library, of the Rochester Institute of Technology, to reproduce this document in whole or in part, with the knowledge that any reproduction will not be for commercial use or profit.

Joanna Kiljan Signature of the author

<u>Dec 18, 2004</u> Date

# Acknowledgments

I would like to express my gratitude to all individuals who assisted me in completing this work, especially Dr. A. Raisanen and my advisor Dr. Karl D. Hirschman with whom I had many valuable technical discussions, and who provided support and guidance throughout my research work. I would also like to thank Dr. Santosh Kurinec for her technical input and participation as a member of my thesis committee.

In addition, I would like to acknowledge Dr. J. Jack for his invaluable help with DRIE at Kodak, Dr. L. Fuller for providing AZ 9260 photoresist, David Springer for carrying out the XeF2 etch, Dr. W. Grande for arranging nitride deposition at Cornell, Dr. V. Genova for performing nitride deposition at Cornell and Mr. Michael D. Potter for his role in defining the initial device.

Completion of this project would not have been possible without a generous support from the Semiconductor and Microsystems Fabrication Laboratory (SMFL) whose staff included: Bruce Tolleson, Sean O'Brien, David Yackoff, John Nash, Richard Battaglia, Charles Gruener, Scott Blondell, and Thomas Grimsley. Finally, I would like to express my appreciation for some of my friends for their support and encouragement throughout this work, including: Daniel Kucharski, Michael Yakimov, and Eric Wheeler.

#### Abstract

In this work a micro-electro-mechanical system (MEMS) is proposed for radio frequency (RF) switching applications. MEMS devices outperform the traditionally used solid-state devices in areas such as isolation, insertion loss, and linearity. However, micro switches suffer from high actuation voltage, lifetime limitations, and high packaging cost. A novel micro switch design that incorporates embedded charge in a cantilever structure can, in principle, enable low-voltage operation. This was the primary motivation for this study.

The experiments in this investigation explored charge injection and retention in a tri-layer oxide/nitride/oxide (ONO) stack capacitor. High-field injection was used to place charge within the dielectric stack. Capacitance-voltage (C-V) measurements were performed to quantify the effective amount of charge stored. The stability of the trapped charge was studied using elevated temperatures, indicating a room-temperature storage lifetime of several years.

A fabrication process for a free-standing film stack membrane was also developed. The process was designed to be post-charge-injection, and therefore was required to adhere to low thermal budget constrains. A masking process for deep reactiveion etching (DRIE) was established using a thick photoresist process (AZ 9260,  $t_{PR}=10\mu m$ ). The fully released ONO stack proved to be mechanically robust: no damage to diaphragms was observed during subsequent processing and handling.

| Title Page                                               | I    |

|----------------------------------------------------------|------|

| Acknowledgement                                          | III  |

| Abstract                                                 | IV   |

| Table of Content                                         | V    |

| List of Tables                                           | VIII |

| List of Figures                                          | IX   |

| 1. Introduction                                          | 1    |

| 1.1 Introduction                                         | 1    |

| 1.2 RF MEMS in Telecommunication                         | 1    |

| 1.3 Performance Comparison of FET, PIN Diode and RF MEMS | 4    |

| 1.4 MEMS Technology Background                           | 5    |

| 1.4.1 Electromagnetic Actuation                          | 6    |

| 1.4.2 Thermal Actuation                                  | 7    |

| 1.4.3 Piezoelectric Actuation                            | 9    |

| 1.4.4 Electrostatic Actuation                            | 11   |

| 1.4.5 Summary of the Actuation Mechanisms                | 13   |

| 1.5 Electrostatic Microswitches                          | 14   |

| 1.6 Challenges of MEMS                                   | 16   |

| 1.7 Motivation                                           | 17   |

| 1.8 Thesis Overview                                      | 19   |

| References                                               | 20   |

| 2. Background in Charging                                | 22   |

| 2.1 Introduction                                         |      |

| 2.2 Electrets                                            | 22   |

| 2.3 Nonvolatile Memory                                   | 25   |

| 2.4 Charge Transport Mechanisms                          |      |

| 2.5 Charges within the Dielectrics                       |      |

| 2.5.1 Charge in Silicon Nitride                          | 34   |

| 2.5.2 Charge in Silicon Dioxide                          | 35   |

| 2.6 C-V Measurements                                     |      |

# Table of Contents

| 2.7 Charge Distribution within Multi-Layer Insulators | 44  |

|-------------------------------------------------------|-----|

| References                                            | 46  |

| 3. High Field Charge Injection                        | 49  |

| 3.1 Introduction                                      | 49  |

| 3.2 Tool Setup                                        | 49  |

| 3.3 Quality of Films                                  | 51  |

| 3.4 Analysis of C-V Curve                             | 54  |

| 3.5 Mobile Ion Charge Density                         |     |

| 3.6 High Electric Field Charge Injection              | 60  |

| 3.7 Charging of Thick Oxide                           | 67  |

| 3.8 Retention of Charge                               | 70  |

| 3.9 Thermal Detrapping                                | 72  |

| 3.10 Summary                                          | 76  |

| References                                            | 77  |

| 4. Design and Modeling of Embedded Charge Microswitch | 79  |

| 4.1 Theory of Operation                               | 79  |

| 4.2 One-Dimensional Model                             | 80  |

| 4.3 Summary                                           |     |

| Reference                                             |     |

| 5. Fabrication of the Electret Membrane               |     |

| 5.1 Introduction                                      |     |

| 5.2 Membrane Fabrication                              | 90  |

| 5.2.2 Processing Development                          | 90  |

| (A) Masking Layer                                     | 90  |

| (B)Thin Film Stress Investigation                     |     |

| (C) Etching of Silicon                                | 97  |

| (D) Deep Reactive Ion Etch                            | 103 |

| (E) The Effect of Etching on Charge Retention         | 106 |

| 5.2.3 Fabrication and Release of a Charged Membrane   | 110 |

| 5.3 Summary                                           | 116 |

| References                                                                   | 117 |

|------------------------------------------------------------------------------|-----|

| 6. Conclusion                                                                | 118 |

| 6.1 Summary1                                                                 | 118 |

| 6.2 Suggestions for Future Experiments                                       | 120 |

| 6.3 Concluding Remarks                                                       | 121 |

| References                                                                   | 122 |

| Appendix A: Processing Recipes1                                              | 23  |

| Appendix B: Tool Specifications                                              | 26  |

| Appendix C: Approximate contact potential of materials to intrinsic silicon1 | 28  |

# List of Tables

| Table | Description Pa                                                                                                                                                                                                                                                                                                                                             | age |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1:  | Comparison between properties of FET, PIN diode and MEMS RF switches [1.9]                                                                                                                                                                                                                                                                                 | 4   |

| 1.2:  | Performance summary of different actuation mechanisms [1.9]                                                                                                                                                                                                                                                                                                | .13 |

| 3.1:  | Summary of the charge injection results for n and p type wafers                                                                                                                                                                                                                                                                                            | .63 |

| 3.2:  | Charge density at possible locations within tri-layer film stack                                                                                                                                                                                                                                                                                           | .66 |

| 3.3:  | Data points collected through thermal relaxation of a charged tri-layer capacitor experiment. VFB obtained from C-V curves during incremental increase in temperature.                                                                                                                                                                                     | .74 |

| 4.1:  | Values used in equations 4.9 and 4.10                                                                                                                                                                                                                                                                                                                      | .84 |

| 5.1:  | Design matrix for different film stack                                                                                                                                                                                                                                                                                                                     | .94 |

| 5.2:  | Summary of the thicknesses of oxide, nitride and LTO films                                                                                                                                                                                                                                                                                                 | .96 |

| 5.3:  | Summary of stress measurements, where oxides are compressive and silicon<br>nitride is highly tensile. Oxide, SixNy, LTO columns represent stress<br>measured on the device wafers after deposition of each film. M-SixNy and<br>M-LTO columns show stress of SixNy and LTO film which were deposited<br>on the plane silicon wafer with the device wafers | .96 |

| 5.4:  | Summary of Results for different silicon etch systems                                                                                                                                                                                                                                                                                                      | 02  |

| 5.5:  | Parameters used for XeF2 etch at Xactix of a partially etched wafer1                                                                                                                                                                                                                                                                                       | 08  |

| 5.6:  | Summary of stress measurements of the final device1                                                                                                                                                                                                                                                                                                        | 14  |

# List of Figures

| Table | Description                                                                                                                                               | Page |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1:  | Signal transmission diagram: (a) system level view of phased-array antennas (b) switched–line implementation [1.2]                                        |      |

| 1.2:  | A cross section of electromagnetic actuator demonstrating the effect of magnetic flux                                                                     | 6    |

| 1.3:  | Electromagnetic microswitch [1.3]                                                                                                                         | 7    |

| 1.4:  | The martensite and austenite phases [1.15]                                                                                                                | 8    |

| 1.5:  | Cross section view of a bimorph valve at close and open position [1.16]                                                                                   | 9    |

| 1.6:  | Piezoelectric Crystal Relaxed and under Compression [1.17]                                                                                                | 10   |

| 1.7:  | An example of piezoelectric microswitch [1.18]                                                                                                            | 10   |

| 1.8:  | Parallel-plate capacitor                                                                                                                                  | 11   |

| 1.9:  | A top view and cross section view of an electrostatic Switch [1.19]                                                                                       | 12   |

| 1.10: | Resistive RF Micro Switch [1.27]                                                                                                                          | 14   |

| 1.11: | Cross section and top view of a capacitive RF Micro Switch [1.28]                                                                                         | 15   |

| 1.12: | Two possible configurations of a microswitch with a circuit                                                                                               | 16   |

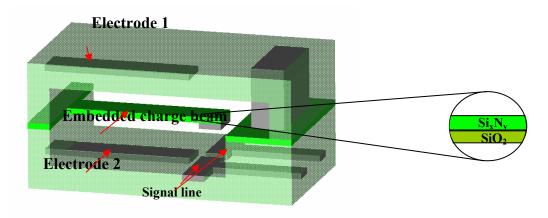

| 1.13: | MEMS switch based on embedded charge concept using a bi-layer film stack for the cantilever.                                                              | 18   |

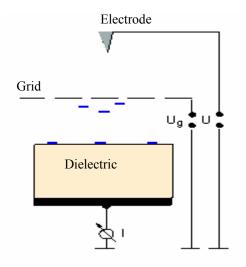

| 2.14: | Schematic representing corona charging system                                                                                                             | 24   |

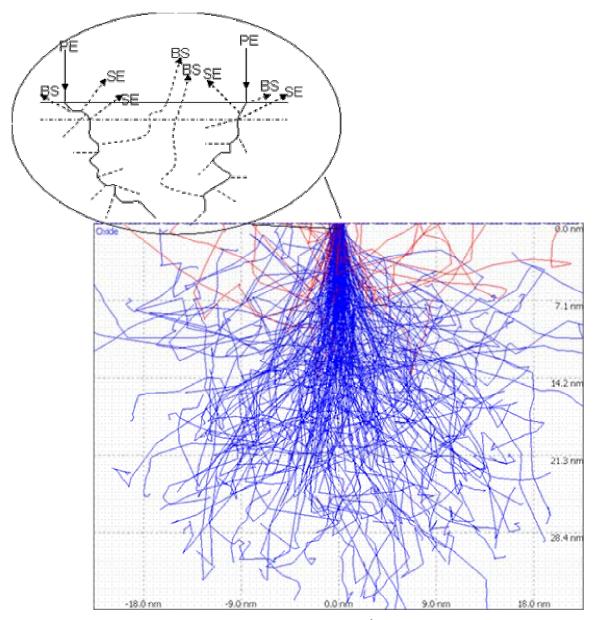

| 2.2:  | Illustration of electron penetration within 1000Å of oxide film using Casino v 2.42 program. The e-beam potential was 1kV, and the beam diameter was 1nm. | 25   |

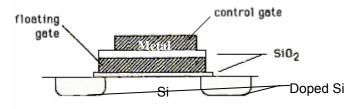

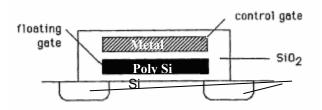

| 2.3:  | MIMS device                                                                                                                                               | 26   |

| 2.4:  | Floating gate nonvolatile memory device [2.10]                                                                                                            | 26   |

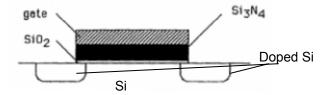

| 2.5:  | Cross section of a MNOS device [2.10]                                                                                                                     | 27   |

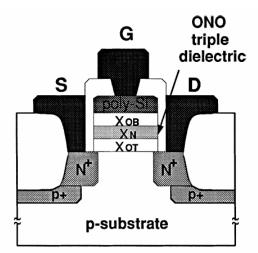

| 2.6:                                  | Cross section of a SONOS device. Tunneling oxide thickness (XOT) 2 nm, storage nitride (XN) 4.5nm and blocking oxide (XOB) 5.5nm. Injection voltage of 10V and erasing voltage –9V [2.11]                                                                                                                                                        | 27 |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.7:                                  | Current vs. temperature relationship for various dielectrics<br>(SiO2, Al2O3, Si3N4) [2.9]                                                                                                                                                                                                                                                       | 29 |

| 2.8:                                  | Illustration of Frankel-Pool emission where field-induced barrier lowering allows thermally energized charger to escape                                                                                                                                                                                                                          | 30 |

| 2.9:                                  | Illustration of charge hopping conduction where trap sites are close to the conduction band.                                                                                                                                                                                                                                                     | 31 |

| 2.10:                                 | (a) equilibrium state (b) Fowler- Nordheim tunneling                                                                                                                                                                                                                                                                                             | 32 |

| 2.11:                                 | Direct Tunneling through thin SiO2                                                                                                                                                                                                                                                                                                               | 33 |

| 2.12:                                 | Diagram illustrating principles of avalanche injection: (a) voltage applied<br>onto the gate at different stages of avalanch injeciton (b) band diagram at<br>the initial state T=0, (c) band bending due to electric field at T1,<br>(d) creation of a electron-hole pair and charge injection at T2. Reprint of<br>Nicollian and Brews [2.15]. | 34 |

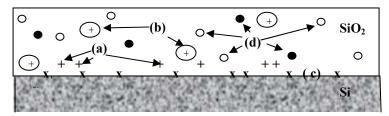

| 2.13:                                 | Charge and their location for silicon dioxide film. (a) fixed charge,<br>(b) mobile charge, (c) interface trapped charge, (d) oxide trapped charge,<br>Reprint after Deal[2.20].                                                                                                                                                                 | 36 |

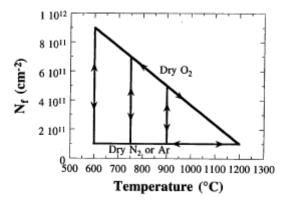

| 2.14:                                 | "Deal triangle", plot of heat treatment and its effect on reducing Qf [2.21]                                                                                                                                                                                                                                                                     | 36 |

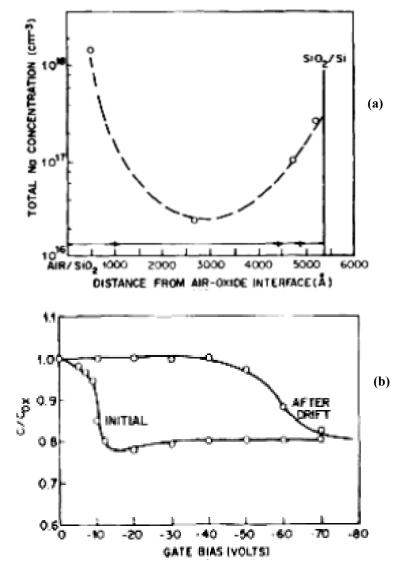

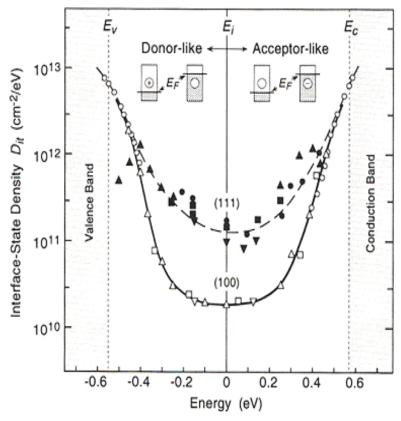

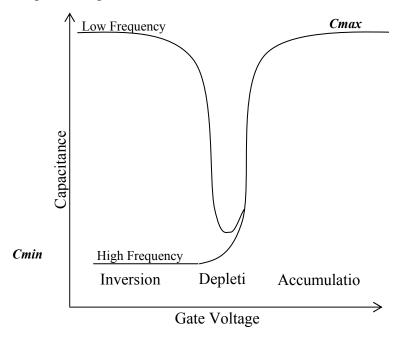

| <ul><li>2.15:</li><li>2.16:</li></ul> | <ul> <li>(a) Sodium profile within oxide, (b) C-V curve illustrating the before and after bias-temperature drift [2.22]</li> <li>Distribution of interface trapped charge density over the energy spectrum of thermally grown SiO2 on (111) and (100) Si substrate[2.23]</li> </ul>                                                              |    |

| 2.17:                                 | C-V curve example for n-type MOS-C                                                                                                                                                                                                                                                                                                               |    |

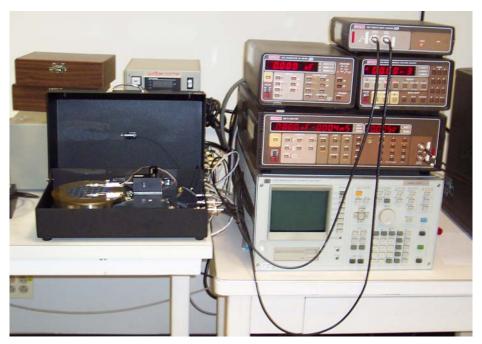

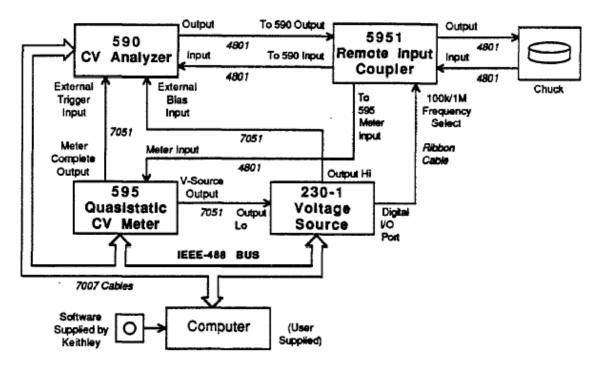

| 3.1:                                  | CV test setup located at RIT                                                                                                                                                                                                                                                                                                                     | 50 |

| 3.2:                                  | High-field charge injection setup located at RIT                                                                                                                                                                                                                                                                                                 | 50 |

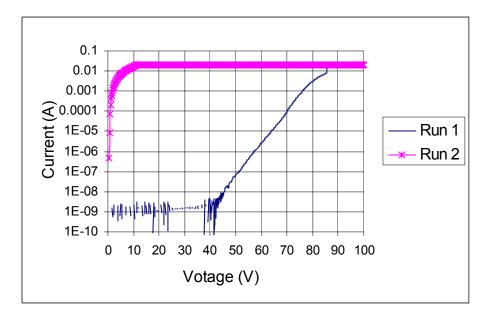

| 3.3:                                  | Breakdown plots of silicon nitride film of 770Å thick deposited using<br>a 50sccm of NH3 and 4sccm of SiH2Cl2. Run 1 illustrates partial<br>breakdown at ~85V. Run 2 illustrates a catastrophic breakdown at ~ 5 V<br>of the same capacitor.                                                                                                     | 52 |

| 3.4:  | .4: Breakdown plots of LTO film of 730Å deposited using the standard SMFL recipe. Run 1 illustrates partial breakdown at ~85V. I-V plot of Run 2 illustrates increased in leakage current resulting eventually in catastrophic breakdown at ~ 90 V.      |     |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

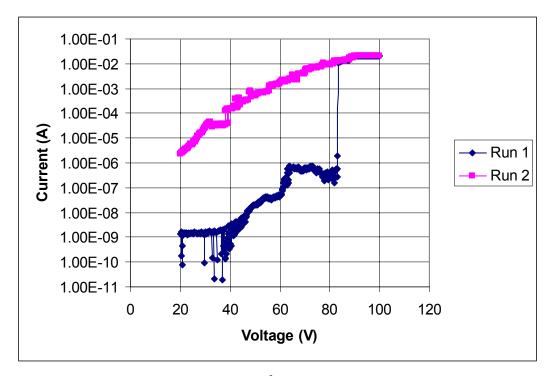

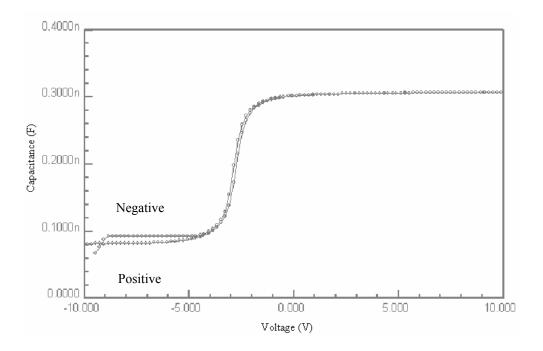

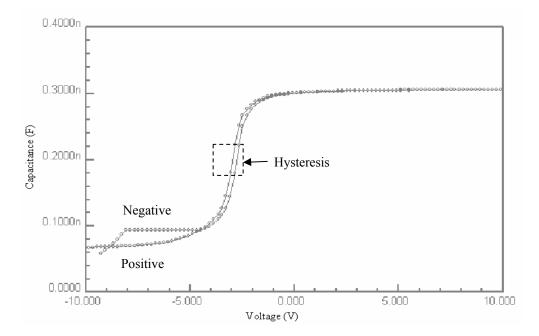

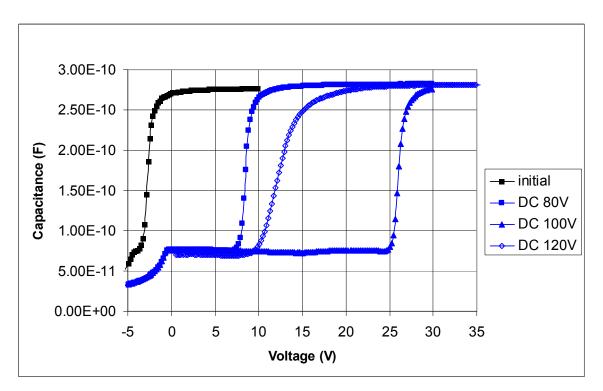

| 3.5:  | Positive and negative sweep with 200ms bias delay for C-V measurement using a tri-layer film stack of 520Å oxide, 508Å nitride and 450Å oxide.                                                                                                           | 56  |  |

| 3.6:  | Positive and negative sweep with 70ms bias delay for C-V measurement<br>using a tri-layer film stack of 520Å oxide, 508Å nitride and 450Å oxide.<br>The hysteresis is attributed to the presence of interface charge                                     | 56  |  |

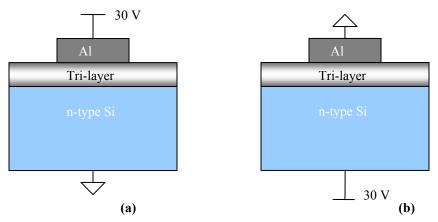

| 3.7:  | Polarity diagrams of the capacitor used in mobile ions experiment with (a) positive bias (accumulation mode), and (b) negative bias (inversion mode)                                                                                                     | 59  |  |

| 3.8:  | Plot of C-V curves representing voltage shift caused by presence of mobile ions within the tri-layer film stack.                                                                                                                                         | 60  |  |

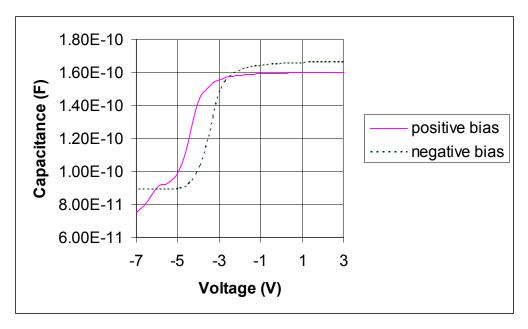

| 3.9:  | Plot of C-V curves showing flat band voltage shift due to charge inject with various negative DC biases                                                                                                                                                  | 62  |  |

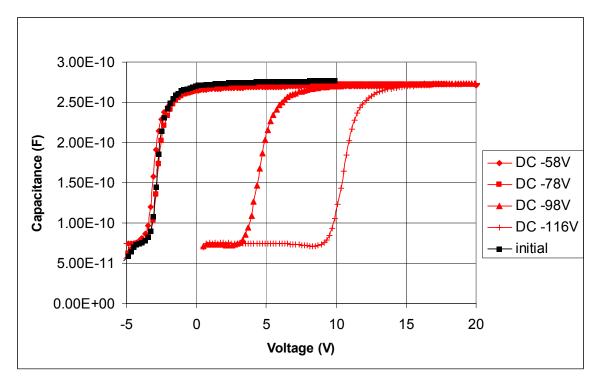

| 3.10: | Plot of C-V curves showing flat band voltage shift due to charge inject with various positive DC bias where DC 120V C-V curve illustrates stretching as well as a decrease in voltage shift.                                                             | 62  |  |

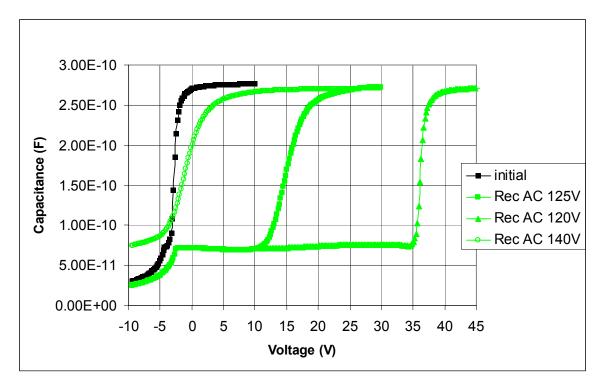

| 3.11: | Plot of C-V curves showing flat band voltage shift due to charge inject<br>using a positive rectified AC signal of various amplitudes, where Rec. AC<br>120V and Rec AC 140 V C-V curves illustrate stretching as well as<br>a decrease in voltage shift | 63  |  |

| 3.12: | Summary of the charge injection results for n and p type wafers                                                                                                                                                                                          | 64  |  |

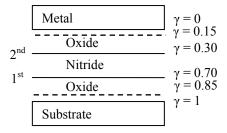

| 3.13: | $\gamma$ represents the centroid of charge for a film stack of 520Å oxide, 508Å nitride, 450Å oxide. In this case, four possible locations are indicated                                                                                                 | 65  |  |

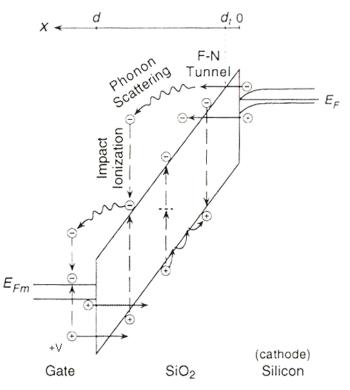

| 3.14: | Band diagram of a possible process taking place during charge injection [3.9].                                                                                                                                                                           | 67  |  |

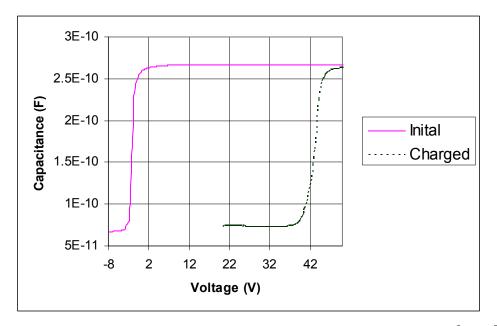

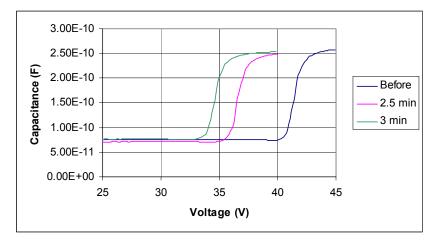

| 3.15: | C-V plot showing maximum voltage shift for ONO tri-layer stack of ~500Å/500 Å/500Å. Charged using a rectified AC signal of 114 V which measured voltage shift of 45.5 V                                                                                  | 68  |  |

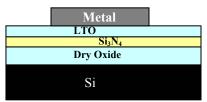

| 3.16: | Capacitor made film stack consisting of 1039Å of dry oxide, 560Å of Si3N4, and 480Å of LTO                                                                                                                                                               | .68 |  |

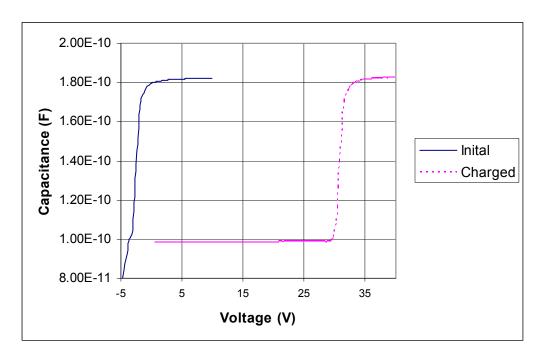

| 3.17: | C-V plot showing maximum voltage shift for ONO tri-layer stack of 1039Å/560Å/480Å. Charged using a rectified AC signal of 180 V which measured voltage shift of 33 V.                                                                                                                                                                                                                                                                                                                                                                | 69 |

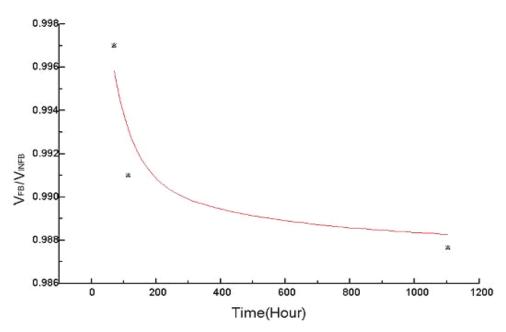

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.18: | Charge retention within the ONO stack, shown by plotting the normalized voltage shift vs. time                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71 |

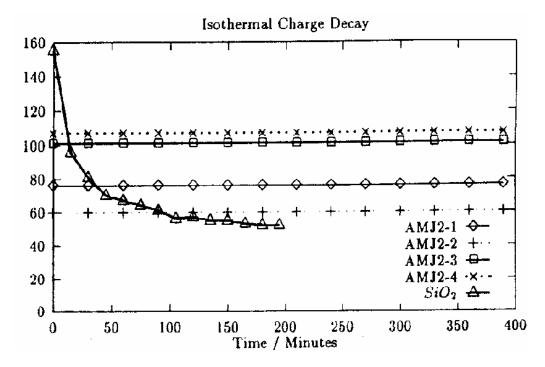

| 3.19: | Normalized charge decay of oxide and oxide-nitride film. The nitride film thickness was 150nm for all four samples. Dry oxide thickness for AMJ2-1 was 150nm and AMJ2-2 was 250nm. Wet oxide thinness for AMJ2-3 was 250nm and for AMJ2-4 was 500nm. The surface potential was measured every 30 min at 300°C. None of the oxide-nitride film stacks showed any charge decay, effectively demonstrating high charge retention even at elevated temperatures. The decay curve observed corresponds to a single layer of oxide [3.16]. | 72 |

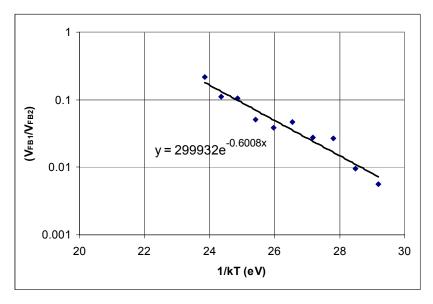

| 3.20: | Plot of the rate constant vs 1/kT used to determine the activation energy.<br>Data points plotted for 130°C to 230°C                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

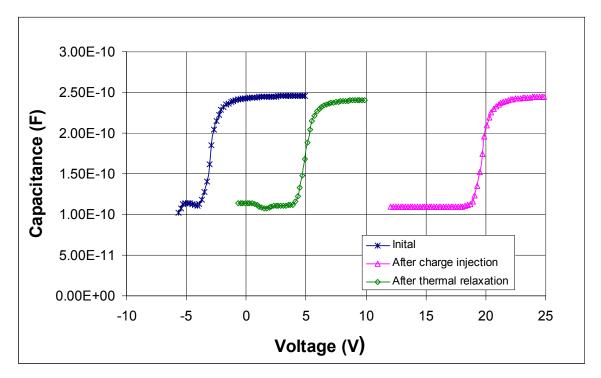

| 3.21: | C-V measurement of tri-layer at the beginning of the experiment, after<br>high field charge injection, and after cooling down to room temperature<br>from 320°C. All the C-V curves were performed at room temperature                                                                                                                                                                                                                                                                                                               | 75 |

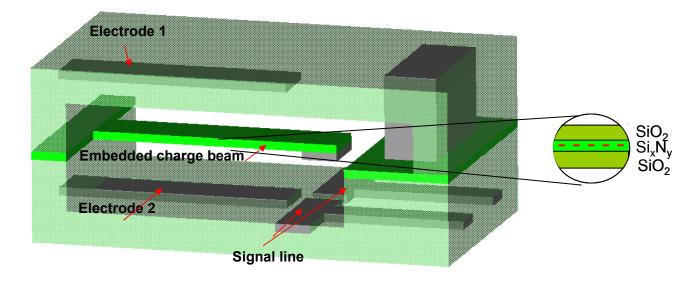

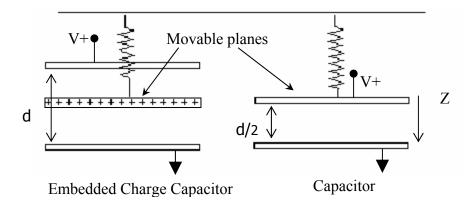

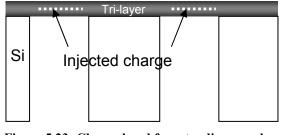

| 4.1:  | MEMS switch based on embedded charge concept using a tri-layer film stack for the cantilever                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80 |

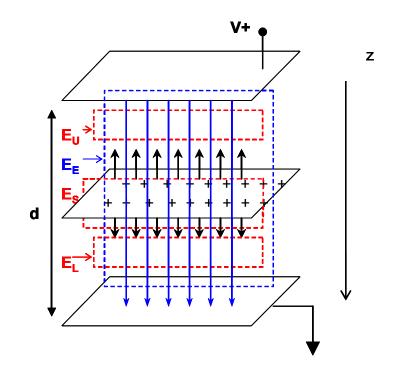

| 4.2:  | Parallel plate capacitor with embedded charge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81 |

| 4.3:  | Physical representation of the two parallel plate capacitors with and without embedded charge.                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84 |

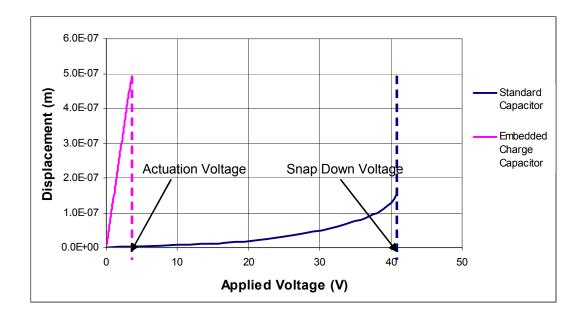

| 4.4:  | Comparison of embedded charge and conventional parallel plate capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85 |

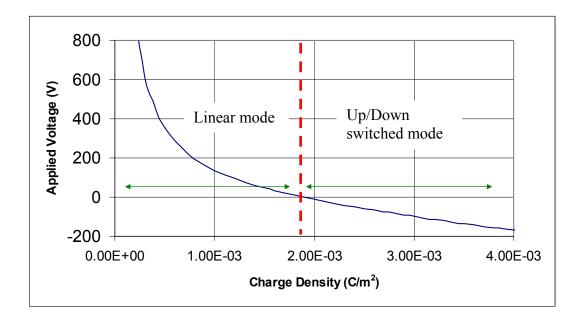

| 4.5:  | Relationship between injected charge density and the actuation voltage for device parameters noted in Table 4.1                                                                                                                                                                                                                                                                                                                                                                                                                      | 86 |

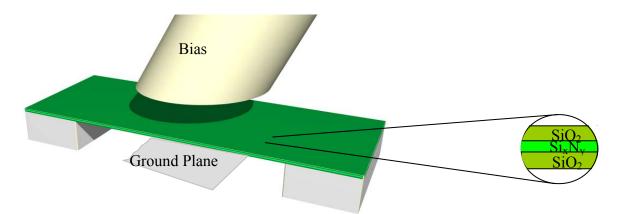

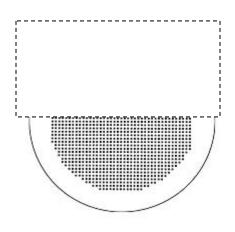

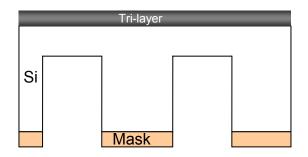

| 5.1:  | Membrane Design where the membrane is composed of oxide-nitride-oxide film stack.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 90 |

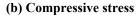

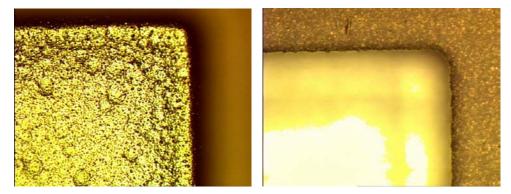

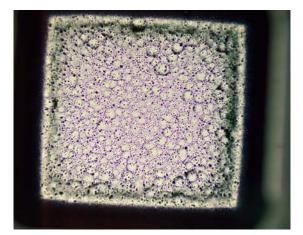

| 5.2:  | Burned resist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91 |

| 5.3:  | Successful pattern transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91 |

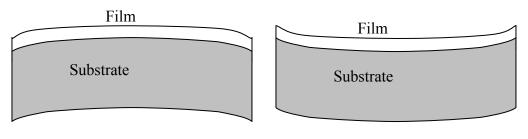

| 5.4:  | (a) Tensile stress, (b) Compressive stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92 |

| 5.5:  | Backside of a wafer after deep silicon etch (a) partially released structure<br>(b) not yet released structure                         | 94  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.6:  | Pattern 3 layout for ellipsometry                                                                                                      | 95  |

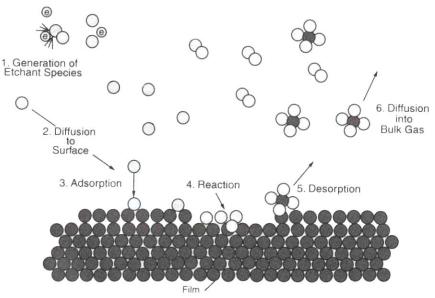

| 5.7:  | Complete reaction mechanism of RIE process [5.9]                                                                                       | 98  |

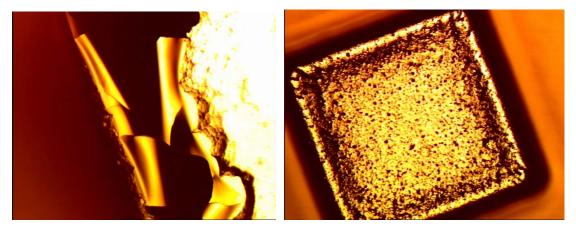

| 5.8:  | Mask design used for RIE, DRIE, XeF2 etch characterization                                                                             | 100 |

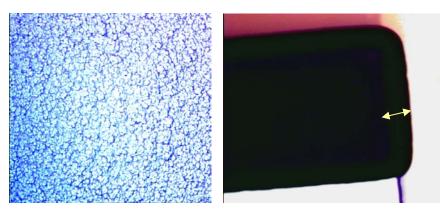

| 5.9:  | Wafer etched using XeF2 at Xactix where the arrow indicates the sidewall etch. Image taken with 10x objective                          | 101 |

| 5.10: | Wafer etched on STS DRIE system at RIT. Image taken with 20x objective                                                                 | 101 |

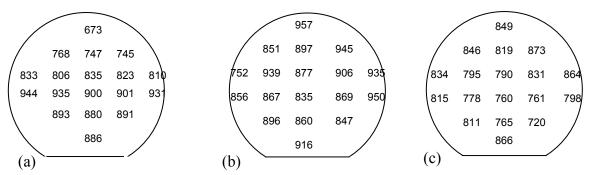

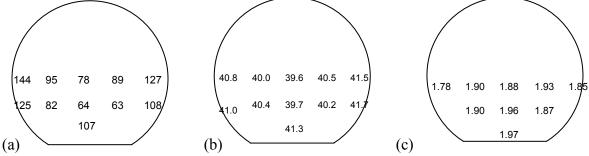

| 5.11: | Amount of oxide removed in angstroms for (a)XeF2 etch, (b) DRI E process, and (c) RIE process.                                         | 102 |

| 5.12: | Amount of silicon removed (um) for (a)XeF2 etch, (b) DRIE porcess,<br>and (c) RIE process.                                             | 102 |

| 5.13: | Pre-existing dome shape of an etch window created by the RIT etch process.                                                             | 104 |

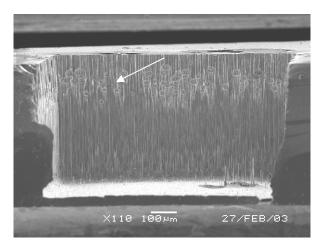

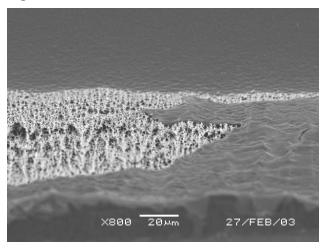

| 5.14: | Cross sectioned etch window after DRIE                                                                                                 | 105 |

| 5.15: | Magnified view of the marked region from Figure 5.14                                                                                   | 105 |

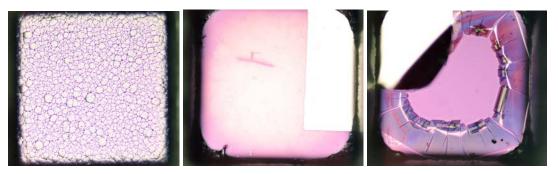

| 5.16: | ONO stack after DRIE etched at Eastman Kodak. Image taken (a) at the center of the wafer, (b) midway, and (c) at the edge of the wafer | 106 |

| 5.17: | Charge retention during silicon etch in Lam 490 system                                                                                 | 107 |

| 5.18: | Silicon wafer after tri-layer deposition and etch of the backside                                                                      | 110 |

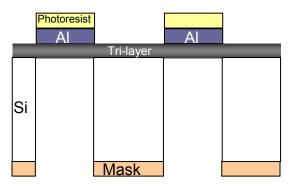

| 5.19: | Partial etch of the silicon substrate using DRIE                                                                                       | 111 |

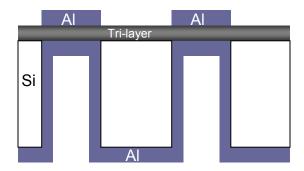

| 5.20: | Fully etch substrate with metal gate                                                                                                   | 111 |

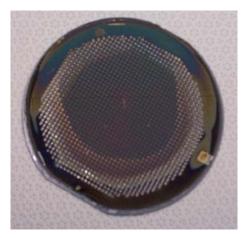

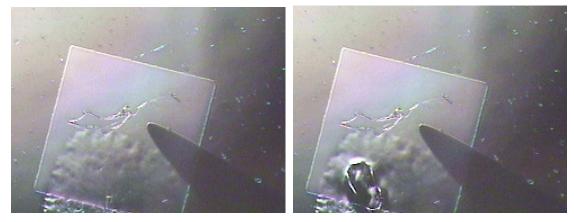

| 5.21: | Image of the actual wafer with released membranes                                                                                      | 112 |

| 5.22: | Cross section view of the released membrane ready for charge injection                                                                 | 112 |

| 5.23: | Charged and free standing membranes                                                                                                    | 113 |

| 5.24: | Test set up for the final examination of the charged in a freestanding<br>tri-layer film stack                                                                   |

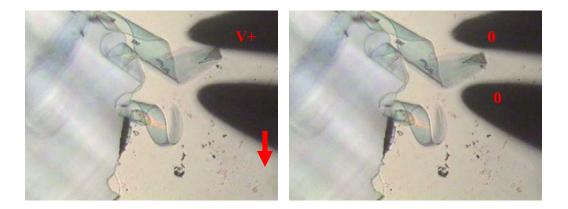

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.25: | Catastrophic breakdown of the released tri-layer of the ONO stack at ~180V (a) before charging (b) after charge injection115                                     |

| 5.26: | (a) Subsection of a membrane placed within the electric field moved<br>towards positive bias, (b) With electric field off it retract to its original<br>position |

# **CHAPTER ONE: INTRODUCTION**

#### 1.1 Introduction

This work introduces a concept, which can address the needs of the telecommunication industry and has a potential to advance other fields such as alternative energy sources. The concept is based on the nonvolatile memory technology where charge is embedded into a dielectric film stack using a high electric field. An electret film is created as a result of this charge injection. The electret film is then released to form a freestanding beam, whose position is controlled with integrated metal electrodes. Such a structure is a member of a group of devices known as microelectromechanical system (MEMS). The primary focus of this work is on radio frequency (RF) switching applications. The proposed design may outperform existing technologies in areas such as actuation voltage and packaging cost. This work provides background information on the subject of RF switches, MEMS, the nonvolatile memory technology and electrets. This is followed by a discussion of design and fabrication of microstructure and is accompanied by experimental results.

## 1.2 RF MEMS in Telecommunication

The financial news journal "Microwaves & RF" reports on a study conducted by a German-based firm Wicht Technologies Consulting [1]. The study predicts a large market growth for radio frequency microelectromechanical systems (RF MEMS) that will reach more than \$1 billion by 2007. Some of the applications of RF MEMS include third

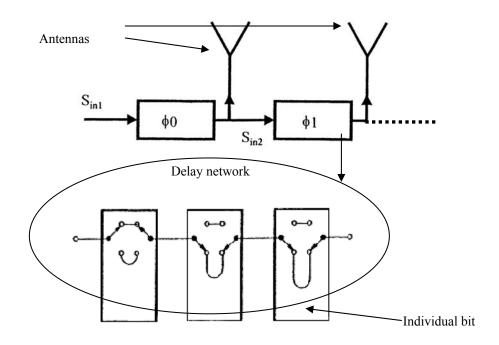

generation mobile phones, global positioning systems, and wireless local area networks. One specific application example for RF MEMS is in satellites and radar systems, where they are used in directional antennas. RF switches in conjunction with delay line banks allow steering of the radiated beam of electro-magnetic energy with no need to physically move the antenna. This is accomplished by introducing phase shifts in the signal path to individual radiating elements in an antenna array. The phase shifts provide constructive interference in the desired direction and destructive interference in all other directions. In such systems, RF switches are used to select delay lines corresponding to various degrees of phase shift at the carrier frequency. For example, Figure1.1 shows a three-bit phase shifter, based on 45°/90°/180° set of delay networks, which allow phase shifts of 0°, 45°, 90°, 135°, 225°, 270° and 315°, depending on the combination of the bits used [2].

Figure 1.1: Signal transmission diagram: (a) system level view of phased-array antennas (b) switched–line implementation [2].

This approach is more reliable and more cost effective compared to a mechanical antenna. More importantly, it allows for rapid time division multiplexing, which is essential in many multi-user systems including cellular networks.

Other types of phase shifters are constructed using solid-state devices such as PIN diodes and FETs. They offer good performance at frequencies up to around 5-20 GHz and switching time as low as 1 ns depending on the size of the device and the required RF power handling. However, at higher frequencies around 30-100 GHz their performance degrades due to signal losses in the solid-state devices [3]. Also, the fabrication cost of PIN and FET designs is high due to the need for compound semiconductors such as GaAs and InP. The use of compound semiconductors also complicates integration with other system components, driving the cost higher.

Compared to conventional solid-state solutions, RF MEMS structures offer performance benefits such as lower insertion loss, higher isolation, lower power consumption and higher linearity. In addition, they have a potential for integration and miniaturization into microsystems, and monolithic processing of MEMS and electronics on silicon substrate could lead to further cost reduction. Therefore, RF MEMS technology has been investigated as a viable replacement for solid-state components.

The insertion loss represents the amount of signal lost when the switch is turned on. Usually, the insertion loss increases with frequency due to the skin effect. The degree to which skin effect affects signal transmission depends on the frequency, permeability, and conductivity of a medium. At low frequencies the entire cross-sectional area of a conductor is used and no skin effect is present. As frequency increases, the center of the medium results in higher impedance causing greater flow of carries through the perimeter

3

of the medium [4]. Isolation is a measure of RF signal leakage for an open switch. Higher magnitude of the isolation parameter is desirable. Linearity is also an issue for solid-state devices, and it can be approximately two times lower compared to RF microswitches. Microswitches are intrinsically more linear than solid states devices due to their passive nature combined with 'on' and 'off' operation. Linearity is simply a measure of how well the frequency content of the output signal resembles that of the input signal, and it is represented by the third order intercept point (IP3) [5]. Higher values of IP3 signify better linearity.

## 1.3 Performance Comparison of FET, PIN Diode and RF MEMS

PIN diodes [6-7], have a relatively low insertion loss compared to FETs [8], but they consume more power and cannot be readily integrated with other electronics. MESFETs use less power but they are expensive to fabricate. Furthermore, their performance declines at high frequencies as a result of high insertion loss and very low isolation. Table 1.1 provides a general overview of the performance parameters related to RF MEMS, PIN diode, and FET switches.

|                                     | RF MEMS   | PIN      | FET      |

|-------------------------------------|-----------|----------|----------|

| Voltage (V)                         | 20-80     | ±3-5     | 3-5      |

| Current (mA)                        | 0         | 3-20     | 0        |

| Power Consumption (mW) <sup>a</sup> | 0.05-0.1  | 5-100    | 0.05-0.1 |

| Switch time                         | 1-300 μs  | 1-100 ns | 1-100 ns |

| Cutoff frequency (THz)              | 20-80     | 1-4      | 0.5-2    |

| Isolation (1-10)GHz                 | Very High | High     | Medium   |

| Isolation (10-40)GHz                | Very High | Medium   | Low      |

| Isolation (60-100)GHz               | High      | Medium   | None     |

| Insertion loss (1-100Ghz) (dB)      | .052      | 0.3-1.2  | 0.4-2.5  |

| IP3(dBm)                            | +66-80    | +27-45   | +27-45   |

Table 1.1: Comparison between properties of FET, PIN diode and MEMS RF switches [9].

Table 1.1 points out the high actuation potential, in the range of 20 to 80 V DC, for electrostatically actuated MEMS devices. This is a major obstacle, since additional high-voltage circuitry and a power source are required to operate these devices. However, from Table 1.1 it is also apparent that MEMS switches offer superior performance compared to solid-state devices in the areas of loss, isolation, IP3, and bandwidth. Therefore, fabricating MEMS switches with lower actuation potentials is an area of intensive research.

### 1.4 MEMS Technology Background

In 1959 Feynman introduced a new field of study known as system miniaturization. He concluded that the laws of physics do not limit miniaturization; rather, it was our ability to create miniature systems that was the limiting factor [10]. That decade Smith's discovery of the piezoresistance effect in germanium and silicon resulted in the fabrication of piezoresistive sensors for stress, strain, and pressure analysis [11]. In 1966 H.C. Nathanson and his colleagues were the first to monolithically integrate micromechanical structures with electronics using a silicon-based process [12].

Currently, a variety of sensors and actuators are available employing a number of actuation mechanisms. The most common mechanisms are piezoelectric, electrostatic, thermal, and electromagnetic. These methods are found in applications related to the automotive, medical, biotechnological, ink jet printing, magnetic data storage, digital image projection, and telecommunication industries. Each method has certain advantages and disadvantages, which determine its suitability for specific applications. The following section offers an overview of each actuation technique. The primary focus is on the electrostatic method, and it will become apparent that it is best suited for switching of RF signals.

#### 1.4.1 Electromagnetic Actuation

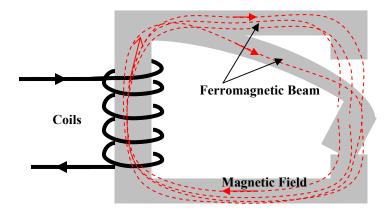

Electromagnetic actuation is based on the Lorentz force. By applying current through a long wire, which has been wound many times into a tightly packed coil, a magnetic field is established that is perpendicular to the plane of the wire loop as shown in Figure 1.2. Due to the magnetic field, the ferromagnetic cantilever and the rest of the structure become magnetized and the air gap between them is reduced. This provides a closed path for the magnetic flux to travel and lowers the beam. Once the current is turned off, the spring constant of the beam restores it to its original position.

Figure 1.2: A cross section of electromagnetic actuator demonstrating the effect of magnetic flux.

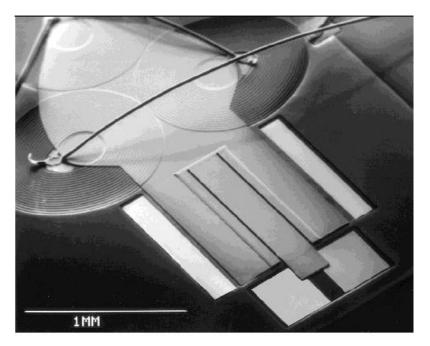

Figure 1.3 shows a top view of a micro-electromagnetic switch. The three circular structures are pancake electromagnetic coils. The long and wide rectangular structure is a ferromagnetic cantilever beam, and the two squares are contact pads. The electromagnetic actuators offer large force and displacement. These electromagnetic actuators can produce forces into the milli Newton range, depending on the coil current.

Figure 1. 3: Electromagnetic microswitch [13].

## 1.4.2 Thermal Actuation

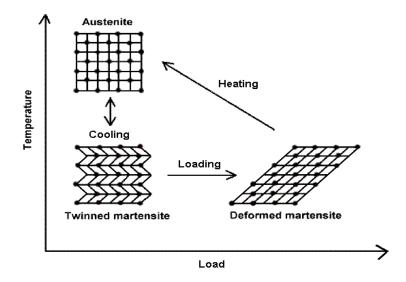

There are various types of thermal actuators the most common of which are shape memory alloys (SMA) and bimorphs. The shape memory alloys are materials that have the ability to return to a predetermined shape when heated. They can be deformed when cooled. SMA materials like NiTi, CuZnAl, and CuAlNi experience two phases known as martensite and austenite in their solid state (see Figure 1.4). The martensite phase occurs at lower temperature. In that phase, the material becomes twinned and can be easily deformed. When the material is heated up, it transitions to the austenite phase. The atoms rearrange themselves to reach the minimum energy state and eventually lead to a shape change on a macroscopic scale. For most shape memory alloys a temperature change of only about 10°C to 20°C initiates the atomic rearrangement [14].

Figure 1.4: The martensite and austenite phases [15].

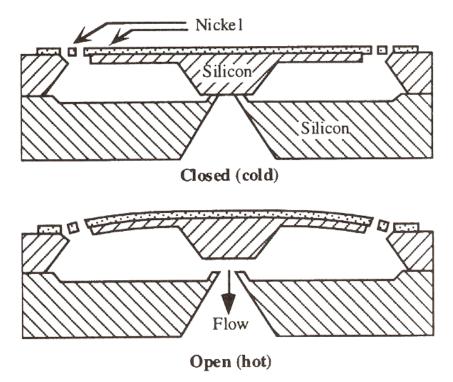

The bimorph effect is caused by thermal expansion of two materials. When the two materials are heated they expand laterally and unevenly due the mismatch in their linear coefficients of expansion. Since they are fused at their interface, elongation will induce a gradient stress across the bi-layer. As a result of the stress in the bi-layer the structure will bend. Once the temperature returns to its initial value, the beam returns to the equilibrium position. Bimorph actuators typically produce high actuation forces and appreciable deflection. Figure 1.5 shows an example of the bimorph valve made of nickel and silicon.

Figure 1.5: Cross section view of a bimorph valve at close and open position [16].

# 1.4.3 Piezoelectric Actuation

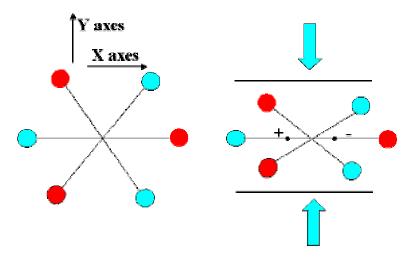

Piezoelectric devices convert mechanical force into induced voltage and vice versus. The piezoelectric effect occurs in certain dielectric crystals such as quartz. Quartz in its equilibrium state has no potential difference. Once pressure is applied to the crystal, its unit cell gets distorted as shown in the Figure 1.6. The distortion induces an electric polarization, and as a result all unit cells become electric dipoles creating a potential difference across a particular face of the crystal. The advantage of piezoelectric materials is that they directly convert mechanical forces such as pressure or vibration into electrical signals. Also, their response time is measured on the order of microseconds.

Figure 1.6: Piezoelectric Crystal Relaxed and under Compression [17].

There are typically used in situation involving dynamic strains of an oscillatory nature like micromotors, pumps and acoustic sensors. Piezoelectric devices usually made of exotic material like lead zirconate titanate (PZT) or lead magnesium niobate (PMN).

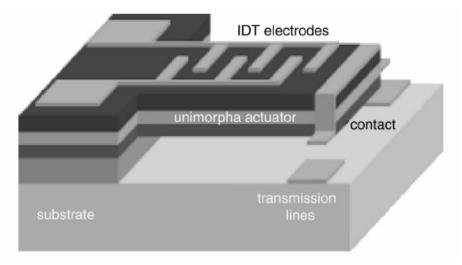

Figure 1. 7: An example of piezoelectric microswitch [18].

#### 1.4.4 Electrostatic Actuation

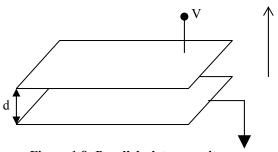

Electrostatic actuation is based on Coulomb's law of attraction between positive and negative charges. Consider a parallel plate capacitor with two constrained metal plates.

Figure 1.8: Parallel-plate capacitor.

Based on these assumptions, the capacitance in Figure 1.8 is defined as

$$C = \frac{Q}{V} = \frac{\varepsilon A}{d} \tag{1.1}$$

where Q represents the charge magnitude on each plate, V is the potential difference,  $\varepsilon$  is the permittivity of the dielectric in the space between the plates, d is the distance separating the plates, and A is the area of each plate. The electrostatic energy U stored in the capacitor is defined as

$$U = \frac{1}{2}CV^2 \tag{1.2}$$

The force between the two plates is governed by Eq.1.3.

$$F = -\frac{\partial U}{\partial z} \tag{1.3}$$

where F denotes the electrostatic force between the two parallel plates, and the potential energy is differentiated with respect to the motion in the z direction. Substituting Eq. 1.1

and Eq.1.2 into Eq.1.3, an expression for the force can be derived for this system, as shown in Eq. 1.4.

$$F = \frac{\varepsilon A V^2}{2z^2} \tag{1.4}$$

This equation applies only if the gap between the two plates is much smaller than the area of the two plates, such that the fringing fields can be ignored. Also, it is assumed that the electric field is constant.

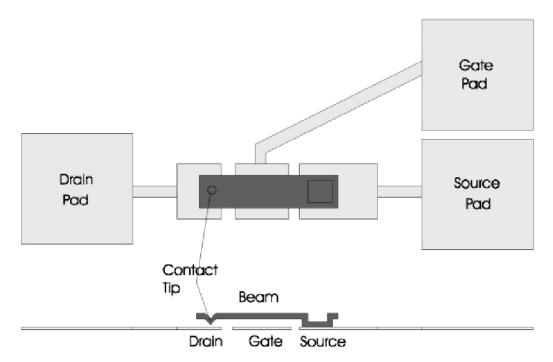

Various design geometries of electrostatic actuators are possible, such as cantilevers [19], motors [20], and comb drives [21]. Their popularity stems from their low power consumption, fast response, and ability to be integrated with solid-state devices. One example of an electrostatic actuator is a three terminal microswitch shown in Figure 1.9. The cantilever is made of metal and is connected to the source pad. Signal is passed from source to drain once the switch is lowered, and the contact tip touches the drain. The gate pad controls the motion of the beam [19].

Figure 1.9: A top view and cross section view of an electrostatic Switch [19].

## 1.4.5 Summary of the Actuation Mechanisms

Currently, microswitch designs implement electrostatic [19], thermal [22], electromagnetic [13] and piezoelectric [23] actuation mechanisms. However, electrostatic actuation is the most prevalent technique at present time. This is due to its low power consumption, which is approximately zero at steady state conditions, as well as small electrode size and short switching time. Table 1.2 summarizes some of the important performance aspects of these different actuation mechanisms.

|               | Voltage | Current | Switching | Power      | Size   |

|---------------|---------|---------|-----------|------------|--------|

|               | (V)     | (mA)    | time (µs) | (mW)       |        |

| Electrostatic | 20-80   | 0       | 0         | 1-200      | Small  |

| Thermal       | 3-5     | 5-100   | 0-200     | 300-10,000 | Large  |

| Magnetostatic | 3-5     | 20-150  | 0-100     | 300-1,000  | Medium |

| Piezoelectric | 3-20    | 0       | 0         | 50-500     | Medium |

Table 1.2: Performance summary of different actuation mechanisms [9].

For example, thermal actuators are capable of large deflections. Their performance is based on how quickly they can heat up and cool down. Therefore, heat dissipation limits their response time. Typical speeds range between 1 kHz and 10 kHz. They are also power inefficient due to Joule heating [24].

Piezoelectric actuators are capable of response time in the range of low MHz, which is comparable to electrostatic devices [25]. Unfortunately, they offer very small displacement. For example, a high stress of 35 MPa generates a strain of only about 0.1% [18]. Also, in most cases they require deposition of exotic ceramics such as lead-zirconate-titanate, which raises manufacturing costs.

Electromagnetic actuators are capable of generating large forces, but they cannot be easily miniaturized. Also, they are power inefficient compared to electrostatic devices. Manufacturing of electromagnetic actuators is more complicated due to the structure of the magnetic windings and the metallic core. As in case of piezoelectric films, ferromagnetic materials are not commonly used in IC integrated circuits, which contributes to higher fabrication cost.

## 1.5 Electrostatic Microswitches

Electrostatic microswitches are categorized by the type of signal coupling and by their configuration in a circuit. There are two types of signal coupling: capacitive and resistive. A resistive switch, also referred to as DC-contact switch [3], operates via direct metal-to-metal contact. It consists of two discontinuous signal lines and a movable cantilever beam. The cantilever has a metal contact that closes the circuit when it is lowered (refer to Figure 1.10). The ohmic contact between the metals allows direct current (DC) as well as high frequency signals to pass. Broadband signal capability is a great advantage of this technology. The shortcomings include limited lifetime of metal contacts. Figure 1.10 shows an example of a resistive RF microswitch designed and manufactured by Motorola.

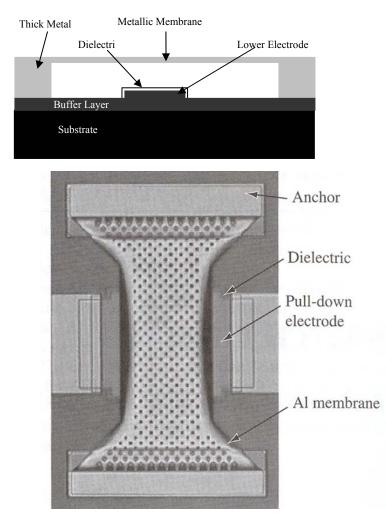

Figure 1.10: Resistive RF Micro Switch [27].

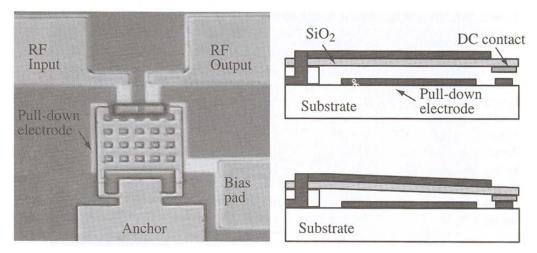

A capacitive switch has a dielectric material and an air gap separating the cantilever and the bottom electrode. The air gap varies as the beam is actuated, which leads to changes in the capacitance between the signal line and the bottom electrode. In a shunt configuration, a large capacitance shunts the signal to ground at high frequencies while a small capacitance allows most of the signal to pass. The advantage of the capacitive switch is longer device lifetime, since there is no contact surface degradation. Capacitive switches can last five to ten times longer then resistive switches [4,8], but they lack low frequency capability. Figure 1.11 shows an example of a capacitive switch eads the tent of the signal by Goldsmith et al [28].

Figure 1.11: Cross section and top view of a capacitive RF Micro Switch [28].

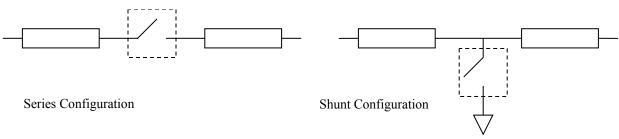

Either a resistive or a capacitive microswitch can be connected in a shunt or in a series configuration with the signal line. As illustrated in Figure 1.12, in the series configuration the switch needs to be 'on' for the signal to pass, and in the shunt configuration the switch needs to be 'off' for the signal to pass. Figure 1.10 shows an example of the series configuration and Figure 1.11 illustrates the shunt configuration.

Figure 1.12: Two possible configurations of a microswitch with a circuit

#### 1.6 Challenges of MEMS

MEMS devices such as the electrostatic microswitch offer many benefits including no static power consumption, low signal losses and small size (compared to the currently used solid-state devices). Their primary drawback is the need for high actuation voltage. Other challenges include life cycle, packaging, and final unit manufacturing cost. Lifetimes of MEMS switches are shorter compared to solid-state devices, which can withstand over 100 billions cycles. In case of resistive switches an abrupt failure occurs after about 10 million cycles for hot switching (assuming 40mA signal current) and nearly 100 millions cycles for cold switching [26]. Hot switching refers to opening and closing of a switch with a signal passing through the contact and often through a specified load. Cold switching refers to switching without any signal

applied to the electrodes. The major failure mechanism for resistive switches is the degradation of the contacts. The contacts become pitted and harden due to the impact force during switching. Also, environmental contamination of the contacts reduces their performance. Some capacitive switches have exceeded a 1 billion-cycle mark [4]. In case of a capacitive switch, stiction is the major failure mechanism. Stiction is the undesirable tendency of small parts to adhere to one another. There are several causes for this unwanted adhesion including contamination, friction, Coulombic attraction, capillary action, and van der Waals forces. Also, charge injection into the dielectric, which can occur during the operation of a capacitive switch, is a problem. Depending on the polarity of the injected charge, the beam can either stick or result in an increased actuation voltage. Packaging and unit price are the greatest challenges of today's MEMS technology. Even if the device processing cost is low, the packaging can account for 60%to 90% of the total cost of a MEMS product [6]. Currently, MEMS packaging is done using epoxy glass, glass-to-glass anodic bonding or gold-to-gold bonding. A drawback of the epoxy glass is the outgassing of the sealing material. Another problem is the high temperature of 300-400°C required for the sealing process, which can affect microswitch properties and cause a premature device failure [4].

#### 1.7 Motivation

The proposed electrostatic microswitch offers a possible solution to the issues of high actuation voltage and device packaging by utilizing embedded charge technology and self-packaging of the device. Using embedding charge to create electrets in MEMS is not a new idea, but creating electrets by applying the same technology used to fabricatenonvolatile memory is quite novel, and it offers endless possibilities for RF switches and other MEMS applications. As mentioned earlier, an electret is a device which can retain electric charge for some amount of time.

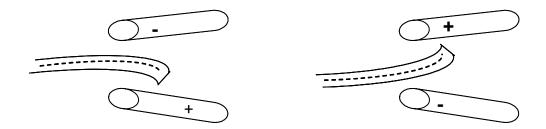

The primary difference between the proposed design and the current designs for electrostatic RF microswitch is the charged cantilever. The charge embedded in the cantilever allows control of the deflection of the beam by an external voltage. When a voltage is applied between electrodes, the beam becomes attracted toward the lower electrode and closes the switch gap with the contact, allowing a signal to pass through. By reversing the polarity, the beam will repel the charged cantilever opening the switch (Refer to Figure 1.13).

Figure 1.13: MEMS switch based on embedded charge concept using a bi-layer film stack for the cantilever.

The benefits of this device address some of the issues related to MEMS technology. For instance, by using standard CMOS fabrication materials such as  $SiO_2$  and  $Si_xN_y$  integration and low cost manufacturing are possible. Also, the device is designed to be self-packaged within a hermetically sealed chamber created during fabrication. The embedded charge switch also offers good control over the beam position, which mitigates

the effects of stiction. Most importantly, the device will actuate at lower voltages compared to the present day MEMS devices.

#### 1.8 Thesis Overview

This thesis consists of four main parts: background, theory of the design, manufacturing of the device and study of high field charge injection. Chapter 1 examines current designs of microswitches. It explains the motivation for the work presented here. Topics such as electrets and nonvolatile memory devices are described in Chapter 2. Also, background information about charge transport mechanisms is provided in this chapter.

Chapter 3 provides the results of the high field charge injection experiments. Chapter 4 focuses on the theoretical analysis of the performance of the electret device. Chapter 5 presents processing details related to the fabrication and the final testing of the device. Chapter 6 concludes this work, summarizes the key findings, and provides recommendations for future work.

#### References

1. "RF MEMS Market To Top \$1B by '07," MRF Microwaves & RF v. 41, no. 12, (2002), pg. 40

2. Hector J. De Los Santos, "Introduction to Microelectromechanical (MEM) Microwave Systems" Artech House ,Boston London, 1999, pg 166-168

3. Gabriel M. Rebeiz ,"RF MEMS theory, design and technology" John Wiley & Sons NJ, 2003, pg 259-262

4. Chris Bowick, "RF Circuit Design", Boston: Newnes, 1982. ,pg 9

5. J. Jason Yao, "RF MEMS from a device perspective Topical review "J. Micromech. Microeng. 10(200) pg R9-R38 printed in UK

6. Bill Doherty, "Pin Diode Fundamentals" MicroNotes Series 701, Microsemi Watertown

7. Robert Pierret, "Semiconductor Devices Fundamentals" Addison Wesley 1996, pg 278

8. Samuel Y. Liao, "Microwave Devices and Circuits", Second edition. Prentice Hall, 1985, pg329-332

9. Gabriel M.Rebeiz, "RF MEMS Theory, Design and Technology", 2003, John Wiley & Sons, pg 4-5

10. Richard P. Fynman,"There's Plenty of Room at the Bottom" presented at the American Physical Socielty Meeting in Pasadena, CA December 1959; J. Microelectromechanical Systems, Vol.2, 1992, pp 60-66

11. Charles H. Smith "Piezoresistance Effect in Germanium and Silicon", Phys. Rev. V94 No1, 1954, pg42-49

12. Harvey C. Nathanson, William E. Newell, Robert A. Wickstrom and John Ransford Davis, "The Resonant Gate Transistor" IEEE Transactions on Electron Devices, Vol ED-14, No3, 1967, pg117-133

13. John A. Wrigth and Yu-Chong Tai, "Micro-Minature Electromagantice Switches Fabricated Using MEMS technology," Proceeding: 46<sup>th</sup> Annual International Relay Confrence: NARM '98, Oak Brook, Illinois, 1998, pp13-1 to 13-4

14. Marc J. Madou, "Fundamentals of Microfabrication: the science of miniaturization " 2<sup>nd</sup> Edition, CRC Press LLC NY,2002, pg 591-593

15. <u>http://www.cs.ualberta.ca/~database/MEMS/sma\_mems/sma.html</u> SMA/MEMS Research Group, Aug 17, 2001

16. Marc J. Madou, "Fundamentals of Microfabrication, The science of miniaturization", CRC Press LLC, 2002, pg 545-546

17. http://www.tedlind.net/Piezoelectricity.htm Theodore Lind Nov. 24 2000

18. S. J. Gross, S. Tadigadapa, T. N. Jackson, S. Trolier-McKinstry, and Q. Q. Zhang," Lead-zirconate-titanate-based piezoelectric micromachined switch", Applied Physics Letters Vol 83(1) pp. 174-176. July 7, 2003

19. Zavracky, PM., S. Majumder, and N.E. McGruer, "Micromechanical Switches Fabricated Using Nickel Surface Micromachining," J. Microelectromechanical Syst. Vol. 6, 1997, pp.3-9.

20. W.S.N. Timmer and K.J. Gabriel "Design Considerations for a Practical Electrostatic Micro-Motor", Sensor& Actuator Application, vol. 11,pg 189-206, 1987

21. W.C.K. Tang, "Electrostatic comb drive levitation and control method." Journal of Microelectromechanical Systems, vol. 1, no. 4, 1992.

22. Girbau, D.; Lazaro, A.; Pradell, L,"RF MEMS switches based on the buckle-beam thermal actuator"Microwave Conference, 2003. 33rd European, Vol. 2, 7-9 Oct. 2003 pg651 - 654

23. Gross, S.J.; Zhang, Q.Q.; Trolier-McKinstry, S.; Tadigadapa, S.; Jackson, T.N "RF MEMS piezoelectric switch" Device Research Conference, June 2003 pg99 – 100

24. Hector J. De Los Santos, "Introduction to Microelectromechanical (MEM) Microwave Systems" Artech House ,Boston London, 1999, pg 26

25. Patrick Johnston, "Free response of piezoelectric crystals in series and in parallel" NASA Langley Research Center, Dec 2003

26. E. A. Sovero, R. Mihailovich, D.S. Deakin, J..A. Higgins, J. J. Yao, J. F. DeNatale and J. H. Hong, "Monolithic GaAs PHEMT MMICs Intergrated with High Performance MEMS Microrelays", SBMO/IEEE MTT-S International Microwave and Optoelectronics Conference Proceedings 1999 p 257-260

27. Gabriel M. Rebeiz ,"RF MEMS theory, design and technology" John Wiley & Sons NJ, 2003, pg 133-134

28. Charles L. Goldsmith Shimino Yao, Susan Eshelman and David Denniston, "Performance of Low Loss RF MEMS Capacitive Switch", IEEE Microwave ands guide wave letters Vol 8, No 8, August 1998,pg269-71

# CHAPTER TWO: CHARGE WITHIN INSULATORS

## 2.1 Introduction

The proposed design of the RF microswitch is comprised of a free-standing electret. The electret is created with oxide and nitride film stack employing the same charge embedding technique, which is commonly used in fabrication of nonvolatile memory devices. In the following chapter some background information is provided on electrets, nonvolatile memory technology, and charge transport mechanisms to facilitate better understanding of the design, fabrication, and operation of the proposed RF microswitch.

# 2.2 Electrets

Dielectric materials, which retain electric charge for a period of time are referred to as electrets [1]. One of the early applications of electrets was in audio microphones. Currently, a variety of materials are available for creating electrets and they address a broad range of applications. A few examples include a polymer electret, a photo-sensitive electret, and a piezo-ceramic electret. Some of the typical applications of electrets include converting mechanical motion into electricity [1], which is the principle used in audio microphones and will likely find use in nano-scale energy harvesting devices. Other areas where electrets have been used with considerable success include filtering of contaminates [2], lubrication, protective coatings, or as a sealing material [3]. They are also found in the biomedical industry [4]. The first electrets were demonstrated in 1919 by Eguchi [5]. They were produced by melting a mixture of carnauba wax, rosin, and bee's wax and cooling it under a static electric field until it solidified. Such electrets were shown to retain the charge at their initial value  $(10^{-5} - 10^{-4} \text{ C/m}^2)$  for three years [5]. Eguchi's technique of making electrets is referred to as thermal heating. This process offers great stability not only on the surface but throughout the bulk of the dielectric, and can be even applied to some non-polar materials like Teflon. The drawbacks of this method are non-uniformity of the lateral charge distribution and the charging speed. There are other techniques of charging and polarizing of organic and inorganic dielectric materials such as contact electrification, which occurs when two dielectrics in contact with each other are in motion relative to each other. Rubbing of two plastic rods is an example of contact electrification. The charging occurs due to electron transfer from one insulator to another. This technique of charging is not popular due to the lack of accurate reproducibility.

Isothermal charging is yet another technique, that depends on electron discharge through an air gap, commonly known as corona charging. The advantages of this method lie in simplicity of the set up and the charging speed. The primary drawback is a large lateral non-uniformity if a special grid electrode is not used.

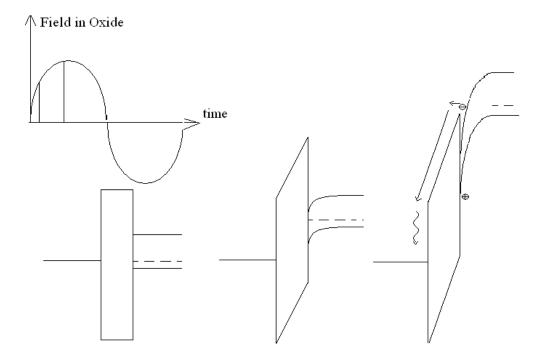

Figure 2.1: Schematic representing corona charging system

Another charging method is based on electron beam injection. As an electron beam strikes the surface, the electrons penetrate the material while scattering within the sample. During the penetration secondary (SE) and backscatter (BS) electrons are generated as shown in Figure 2.2. The secondary electrons exhibit a relatively small energy of 50eV [6]. Some of the secondary electrons escape from the sample and some are trapped close to the surface while all of the backscatter electrons escape from the sample. Due to scattering, the primary electrons (PE) slow down enough to become trapped, resulting in a negatively charged dielectric. The electron beam technique offers a reasonable degree of control over the lateral charge distribution by controlling the energy of the injected electrons via the applied electric potential. Both electron beam and isothermal charging are some of the most popular techniques used for producing electrets [7].

Figure 2.2: Illustration of electron penetration within 1000Å of oxide film using Casino v 2.42 program. The e-beam potential was 1kV, and the beam diameter was 1nm.

## 2.3 Nonvolatile Memory

The first nonvolatile memory device, which was based on metal-oxide-metaloxide-semiconductor (MIMIS) configuration, was proposed by Kahng and Sze in 1967 [8]. The initial oxide was very thin (less than 50Å) to allow direct tunneling of electrons from the silicon substrate into the floating gate. The electrons then remained on the floating gate, since they were insulated by a second, much thicker oxide layer (Figure 2.3). When the potential was removed from the control gate, the field within the thin oxide was too small for back tunneling to occur, and therefore electrons were trapped.

Unfortunately, pinholes in the thin oxide layer, which were unavoidable due to the manufacturing limitations at the time, led to charge leakage. This major obstacle was solved by Frohman-Bentchkowsky in 1971 where a thicker oxide and a polysilicon replaced the tunneling oxide and the metal floating gate (Figure 2.4). Instead of direct tunneling, avalanche injection mechanism, which will be explained in section 2.4, allowed charge to be trapped in the polysilicon floating gate. Changing the state of the device was possible using the control gate [9].

Figure 2.4: Floating gate nonvolatile memory device [10].

Almost concurrently another device using a metal-nitride-oxide-semiconductor (MNOS) configuration, was introduced by Wegner [10]. It was made of thin oxide and nitride films, and a metal gate (Figure 2.5). The nitride and oxide-nitride interface contain many trapping centers where charge can be captured and retained. Even if the

oxide proved to be leaky, some charge would remain due to the deep traps in the oxidenitride interface and the nitride film.

Figure 2.5: Cross section of a MNOS device [10].

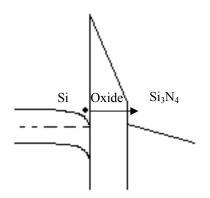

Additional development led to the design of a polysilicon-oxide-nitride-oxide-silicon (SONOS) device (refer to Figure 2.6). The additional oxide layer prevented charge injection into nitride during the erasing step. The SONOS device also offers higher trap charge density compared to the MONS device due to its oxide-nitride-oxide stack and its interfaces. It also provided pinhole coverage, which might be present in the thin nitride layer. With the additional interface between the top oxide and the nitride, thinner nitride films were possible, which allowed lowering of the operational voltage for the SONOS device [11].

Figure 2.6: Cross section of a SONOS device. Tunneling oxide thickness  $(X_{OT})$  2 nm, storage nitride  $(X_N)$  4.5nm and blocking oxide  $(X_{OB})$  5.5nm. Injection voltage of 10V and erasing voltage –9V [11].

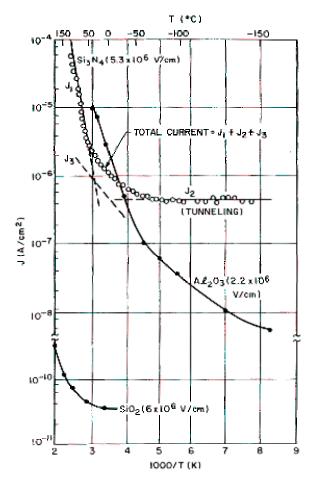

# 2.4 Charge Transport Mechanisms

In an ideal insulator the conduction of the film is assumed to be zero. However, in reality given high enough electric field and/or temperature, a finite carrier current is present. The current in a given material depends on the dominant conduction mechanism present at given conditions as well as on the properties of the film. Figure 2.7 presents a plot of current density versus temperature for three different films (SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, Si<sub>3</sub>N<sub>4</sub>) at a constant electric field. From this plot the transport mechanism at different temperatures can be determined. In the case of Si<sub>3</sub>N<sub>4</sub>, there are three regions of current conduction. J1 region is due to Frankel-Pool emission, J2 is due to the tunnel emission such as Fowler-Nordheim tunneling, and J3 is due to ohmic conduction [9]. Similarly, Al<sub>2</sub>O<sub>3</sub> film illustrates three regions of current conduction similar to Si<sub>3</sub>N<sub>4</sub>. Finally, SiO<sub>2</sub> film shows some conductivity, which is lower by many orders of magnitude compared to either Si<sub>3</sub>N<sub>4</sub> or Al<sub>2</sub>O<sub>3</sub> films.

Figure 2.7: Current vs. temperature relationship for various dielectrics (  $SiO_2$ ,  $Al_2O_3$ ,  $Si_3N_4$ ) [9].

At room temperature and high electric field, Frankel-Poole emission transport mechanism dominates in silicon nitride film [9]. The expression representing Frankel-Pool emission is defined in Eq. 2.1.

$$J \sim E \exp\left[\frac{q}{kT} \left(\Phi_b - \sqrt{qE/\pi\varepsilon_i}\right)\right]$$

(2.1)

where J is the current density,  $\Phi_b$  is the energy barrier of the trap, E is the electric field,  $\varepsilon_i$ is the permittivity of the insulator, T is the absolute temperature, k is Bolzmann's constant, and q is the charge of a single electron. As Eq. 2.1 demonstrates, the current density is associated with thermionic emission and a field-induced barrier lowering of the trap sites [12]. A trapped charge with a sufficient amount of energy can overcome the energy barrier of the trap site and jump into the conduction band, where it can drift due to an electric field. However, once it loses energy it can become trapped again. Figure 2.8 illustrates how a trapped charge propagates through the film.

Figure 2.8: Illustration of Frankel-Pool emission where field-induced barrier lowering allows thermally energized charger to escape.

Another transport mechanisms present in  $Si_3N_4$  film is charge-hopping conduction also referred to as ohmic conduction. It dominates at moderate to high temperatures and at low electric fields. The current flow is due to thermal excitation of charges, which hop from one trap site to the next. The current density depends on the density of defect states and their energy distribution. If the localized states are at the band tail states, the ohmic conduction mechanism follows the expression below [13].

$$J \sim E \exp\left(\frac{-E_a}{kT}\right) \tag{2.2}$$

where  $E_a$  is the activation energy for electron excitation. Figure 2.9 depicts the chargehopping transport mechanism, where trap sites are located close to the conduction band.

Figure 2.9: Illustration of charge hopping conduction where trap sites are close to the conduction band.

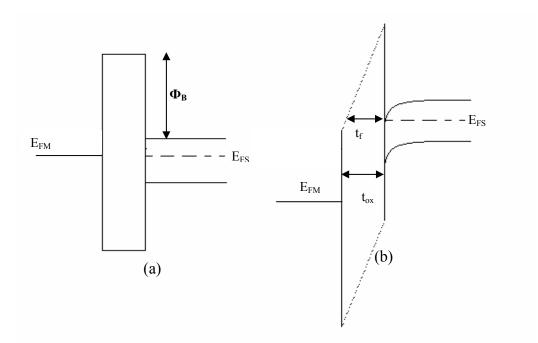

In case of SiO<sub>2</sub> film, the main charge transport mechanism is by charge injection. This is a result of the wide bandgap of 9 eV and low trap charge density found in SiO<sub>2</sub> compared to Si<sub>3</sub>N<sub>4</sub> film. There are two types of mechanisms that can feasibly provide charge transport through SiO<sub>2</sub>. One is based on quantum mechanical tunneling, and the other one is based on hot electron injection.