### Rochester Institute of Technology

# **RIT Digital Institutional Repository**

Theses

5-1-1995

# A VHDL model of a digi-neocognitron neural network for VLSI

**Troy Brewster**

Follow this and additional works at: https://repository.rit.edu/theses

#### **Recommended Citation**

Brewster, Troy, "A VHDL model of a digi-neocognitron neural network for VLSI" (1995). Thesis. Rochester Institute of Technology. Accessed from

This Thesis is brought to you for free and open access by the RIT Libraries. For more information, please contact repository@rit.edu.

# A VHDL Model of a Digi-Neocognitron Neural Network for VLSI

by

**Troy D. Brewster**

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in Computer Engineering

Approved by:

Graduate Advisor - George A. Brown, Professor

Peter G. Anderson, Professor

Tony H. Chang, Professor

**Department of Computer Engineering**

College of Engineering Rochester Institute of Technology Rochester, New York

May 1995

# ABSTRACT

Optical character recognition is useful in many aspects of business. However, the use of conventional computers to provide a solution to this problem has not been very effective. Over the past two decades, researchers have utilized artificial neural networks for optical character recognition with considerable success. One such neural network is the neocognitron, a real-valued, multi-layered hierarchical network that simulates the human visual system. The neocognitron was shown to have the capability for pattern recognition despite variations in size, shape or the presence of deformations from the trained patterns. Unfortunately, the neocognitron is an analog network which prevents it from taking full advantage of the many advances in VLSI technology. Major advances in VLSI technology have been in the digital medium. Therefore, it appears necessary to adapt the neocognitron to an efficient digital neural network if it is to be implemented in VLSI.

Recent research has shown that through preprocessing approximations and definition of new model functions, the neocognitron is well suited for implementation in digital VLSI. This thesis uses this methodology to implement a large scale digital neocognitron model. The new model, the digi-neocognitron, uses supervised learning and is trained to recognize ten handwritten numerals with widths of one pixel.

The development of the neocognitron and the digi-neocognitron software models, and a comparison of their performance will be discussed. This is followed by the development and simulation of the digital model using the VHSIC Hardware Description Language (VHDL). The VHDL model is used to demonstrate the functionality of the hardware model and to aid in its design. The model functions of the digi-neocognitron are then implemented and simulated for a 1.2  $\mu$ m CMOS process.

# **THESIS RELEASE PERMISSION FORM**

### ROCHESTER INSTITUTE OF TECHNOLOGY COLLEGE OF ENGINEERING

Title : A VHDL Model of a Digi-Neocognitron Neural Network for VLSI

I, Troy D. Brewster, hereby deny permission to the Wallace Memorial Library of RIT to reproduce this thesis in whole or in part.

Signature : \_\_\_\_\_

Date :

# **TABLE OF CONTENTS**

| ABSTRACT                                                                    | i   |

|-----------------------------------------------------------------------------|-----|

| TABLE OF CONTENTS                                                           | iii |

| LIST OF FIGURES                                                             | v   |

| LIST OF TABLES                                                              | vi  |

| GLOSSARY OF TERMS                                                           | vii |

| CHAPTER 1                                                                   | 1   |

| 1. 0 Introduction                                                           | 1   |

| 1.1 What are Artificial Neural Networks?                                    | 1   |

| 1.2 Optical Character Recognition and the Neocognitron                      |     |

| 1.3 Digital vs. Analog VLSI Artificial Neural Networks                      |     |

| CHAPTER 2                                                                   | 6   |

| 2. 0 Theory of the Neocognitron Neural Network                              | 6   |

| 2.1 The Neocognitron Model Functions                                        |     |

| 2.2 The Digi-Neocognitron Model Functions                                   |     |

| CHAPTER 3                                                                   | 21  |

| 3. 0 Software Models for the Neocognitron and the Digi-Neocognitron         |     |

| 3.1 Converting from a Neocognitron to a Digi-Neocognitron Model             |     |

| 3.2 Implementation of the Neocognitron Model                                |     |

| 3.2.1 Training the Neocognitron                                             |     |

| 3.2.2 Testing the Neocognitron                                              |     |

| 3.3 Implementation of the Digi-Neocognitron Model                           |     |

| 3.3.1 Training the Digi-Neocognitron                                        |     |

| 3.4 Performance Comparison of the Neocognitron and Digi-neocognitron Models |     |

| CHAPTER 4                                                                   |     |

| 4.0 VHDL Implementation of the Digi-neocognitron                            |     |

| 4.1 VHDL Overview                                                           |     |

| 4.2 Hardware Description of the DNC Model Functions                         |     |

| 4.3 VHDL Simulation of the DNC Model Functions                              | 46  |

| 4.4 Architecture of the Digi-Neocognitron Model                             |     |

| 4.5 VHDL Simulation of the Digi-Neocognitron Model                          | 55  |

| CHAPTER 5                                                               | 58 |

|-------------------------------------------------------------------------|----|

| 5. 0 Circuit Implementation of the Digi-Neocognitron Model Functions    | 58 |

| 5.1 Synthesis and Simulation of the DNC Model Functions                 | 58 |

| 5.1.1 Logic Synthesis of the DNC Model Functions                        | 58 |

| 5.1.2 Simulation of the Synthesized Circuits                            | 60 |

| CONCLUSION                                                              | 70 |

| APPENDIX A                                                              | 72 |

| A-1 C Source Code for the Neocognitron Model Functions                  |    |

| A-2 C Source Code for the Digi-Neocognitron Model Functions             |    |

| A-3 VHDL Source Code for the Digi-Neocognitron Model Functions          |    |

| A-4 Test Bench Models for the Output Functions of the Digi-Neocognitron | 92 |

| REFERENCES                                                              | 97 |

,

# **LIST OF FIGURES**

| Figure 1-1: A single processing element of a neural network and the non-linear function used to limit           |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| its response to the interval [0, 1]                                                                             |    |

| Figure 2-1 : Correspondence between the model by Hubel and Wiesel and the neocognitron neural network           |    |

| Figure 2-2 : The architectural organization of the neocognitron neural network.                                 | 8  |

| Figure 3-1: A one-dimensional view of the interconnections between the cells of the different                   |    |

| layers in the neocognitron.                                                                                     | 23 |

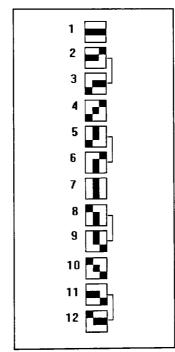

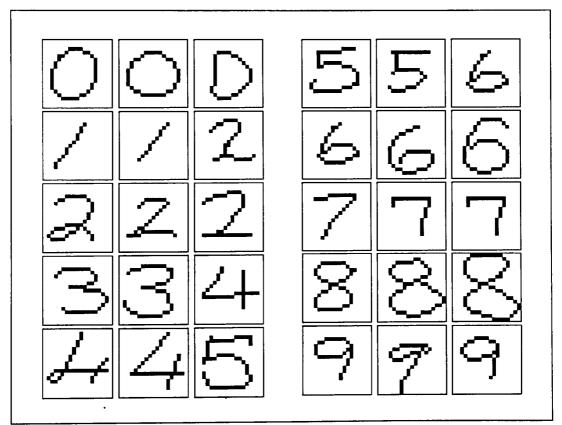

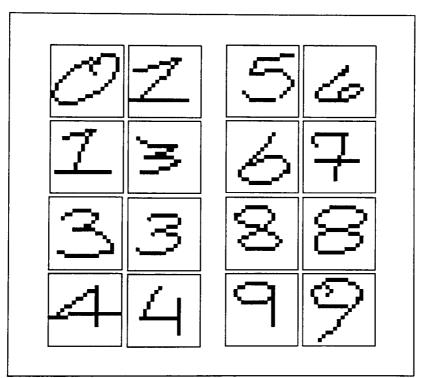

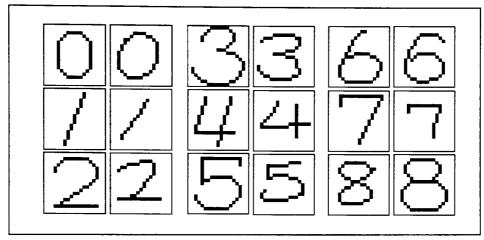

| Figure 3-2 : Patterns used to train the 12 cell planes of layer $u_{SI}$ . How these planes are                 |    |

| combined at the input stage of layer $u_{CI}$ is indicated on the right of the training patterns                | 27 |

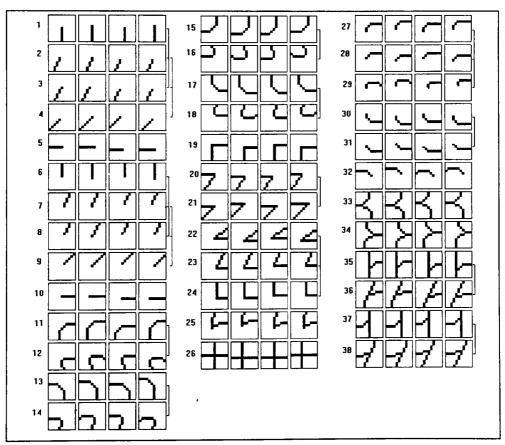

| Figure 3-3 : Patterns used to train the 38 cell planes of layer $u_{s2}$ . How these planes are                 |    |

| combined at the input stage of layer $u_{C2}$ is indicated on the right of training patterns.                   | 28 |

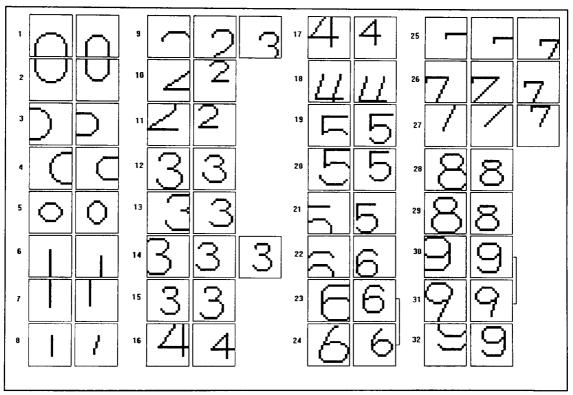

| Figure 3-4 : Patterns used to train the 32 cell planes in layer $u_{S3}$ . How these planes are combined at the |    |

| input stage of layer $u_{C3}$ is indicated on the right of the training patterns                                | 29 |

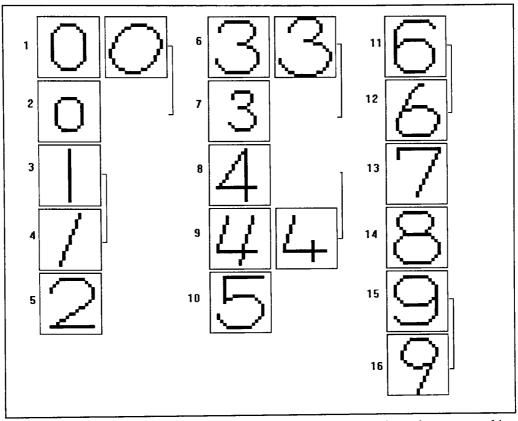

| Figure 3-5 : Patterns used to train the 16 cell planes in layer $u_{S4}$ . How these planes are combined        |    |

| at the input stage of layer $u_{C4}$ is indicated on the right of the training patterns                         |    |

| Figure 3-6 : Sample patterns that were correctly classified by the neocognitron                                 | 31 |

| Figure 3-7 : Sample test patterns that the neocognitron failed to correctly classify                            | 32 |

| Figure 3-8 : Sample test patterns that the digi-neocognitron correctly classified.                              |    |

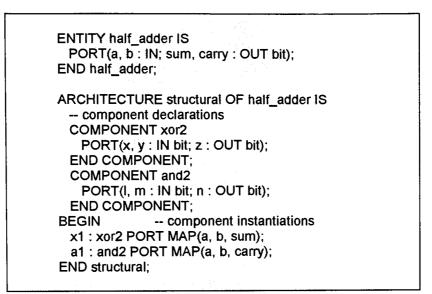

| Figure 4-1 : Structural VHDL model of a half-adder circuit                                                      |    |

| Figure 4-2 : Behavioral VHDL model of a half-adder circuit.                                                     |    |

| Figure 4-3 : Dataflow VHDL model of a half-adder circuit                                                        |    |

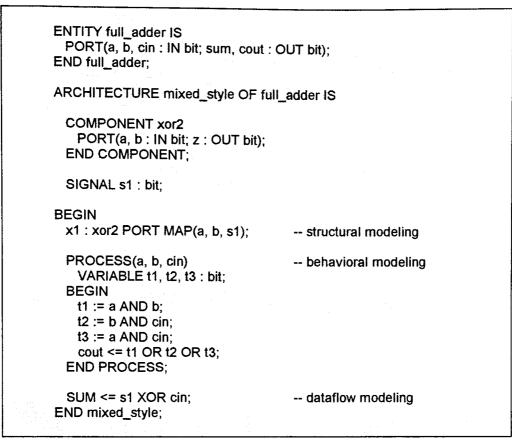

| Figure 4-4 : Mixed-style VHDL model of a full-adder circuit.                                                    |    |

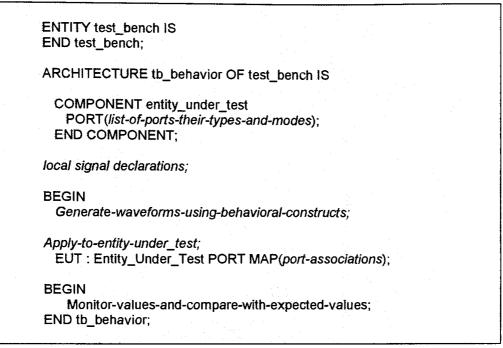

| Figure 4-5 : Typical format of a VHDL test bench model.                                                         |    |

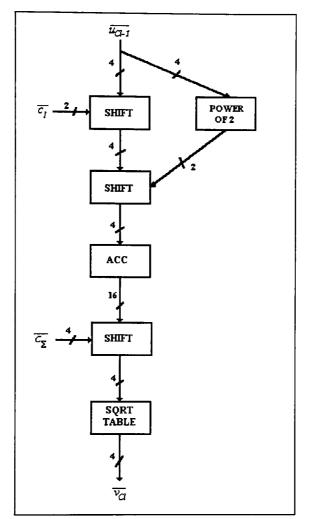

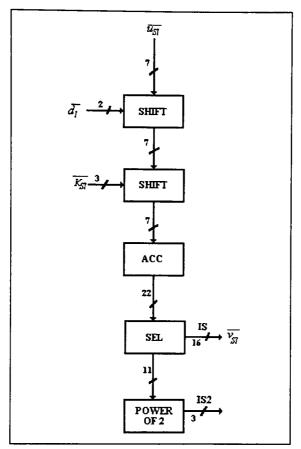

| Figure 4-6 : Block diagram for the Vc-cell output calculation of the digi-neocognitron                          |    |

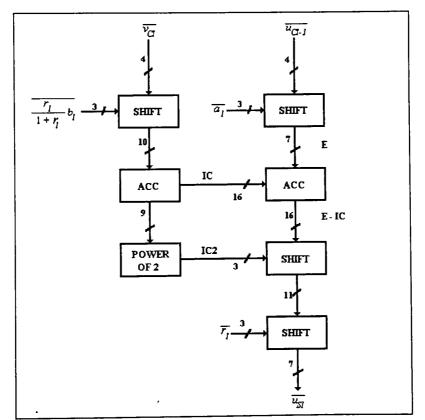

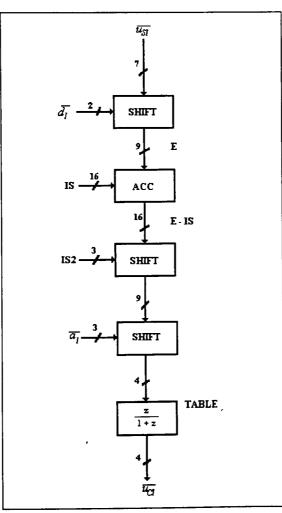

| Figure 4-7 : Block diagram for the S-cell output calculation of the digi-neocognitron                           |    |

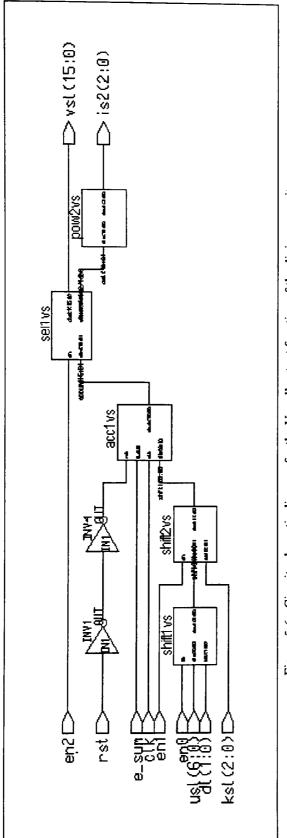

| Figure 4-8 : Block diagram for the Vs-cell output calculation of the digi-neocognitron                          |    |

| Figure 4-9 : Block diagram for the C-cell output calculation of the digi-neocognitron.                          |    |

| Figure 4-10 : Block diagram of the Vc-cell VHDL component.                                                      |    |

| Figure 4-11 : Block diagram for the S-cell VHDL component.                                                      |    |

| Figure 4-12 : Block diagram for the Vs-cell VHDL component.                                                     |    |

| Figure 4-13 : Block diagram for C-cell VHDL component                                                           |    |

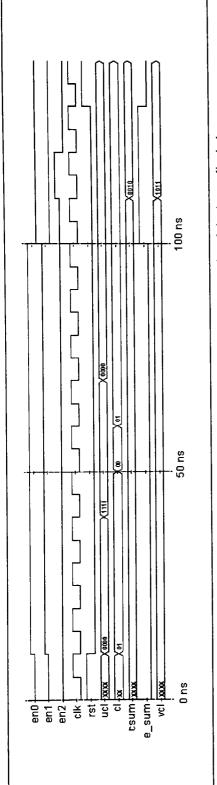

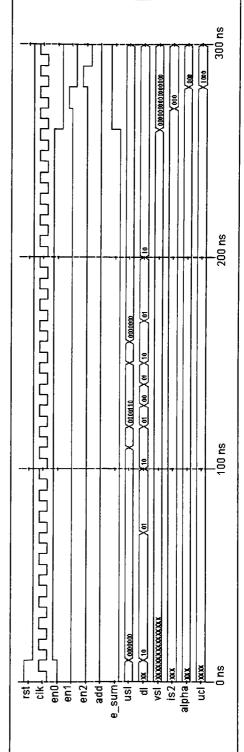

| Figure 4-14 : Simulation results for the Vc-cell component using the test bench in Appendix A-4                 |    |

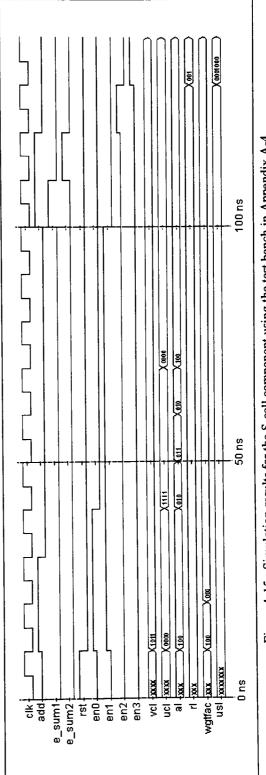

| Figure 4-15 : Simulation results for the S-cell component using the test bench in Appendix A-4                  |    |

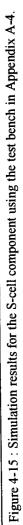

| Figure 4-16 : Simulation results for the Vs-cell component using the test bench in Appendix A-4                 |    |

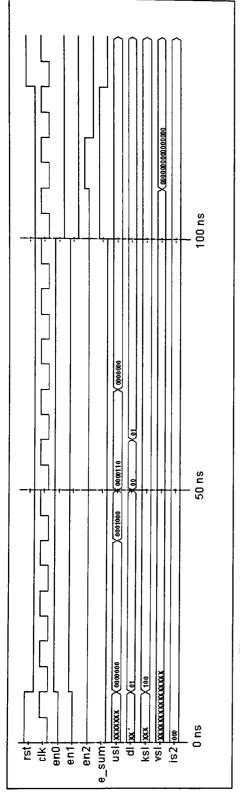

| Figure 4-17 : Simulation results for the C-cell component using the test bench in Appendix A-4.                 |    |

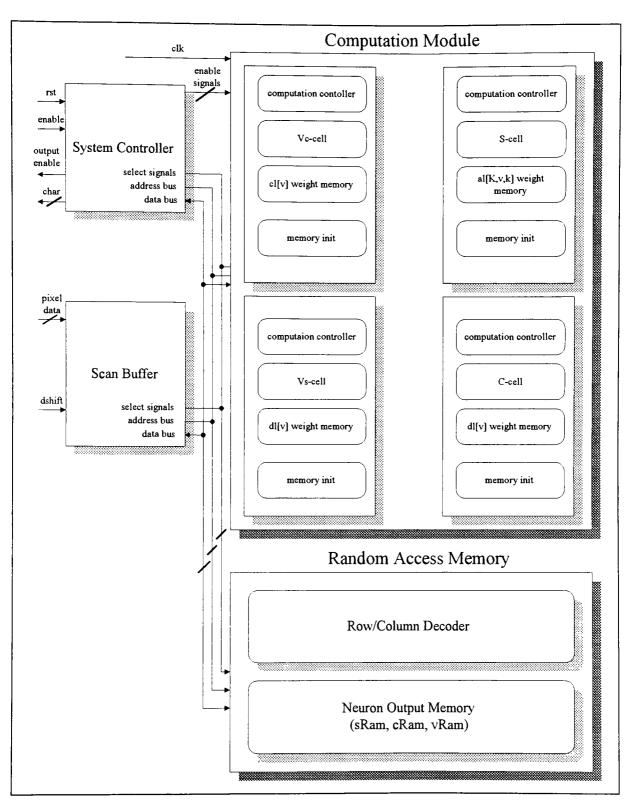

| Figure 4-18 : Architecture of the digi-neocognitron VHDL model.                                                 |    |

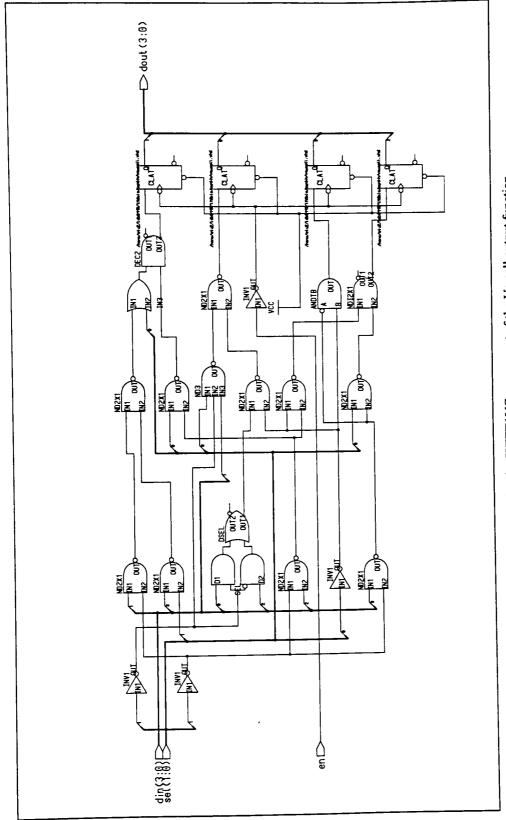

| Figure 5-1 : Logic circuit for the SHIFT1VC component of the Vc-cell output function                            |    |

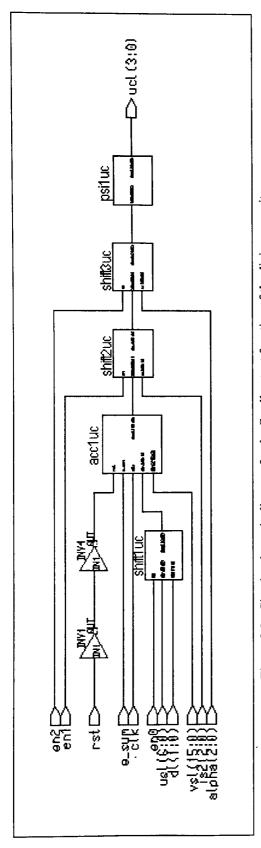

| Figure 5-2 : Circuit schematic diagram for the Vc-cell output function of the digi-neocognitron                 |    |

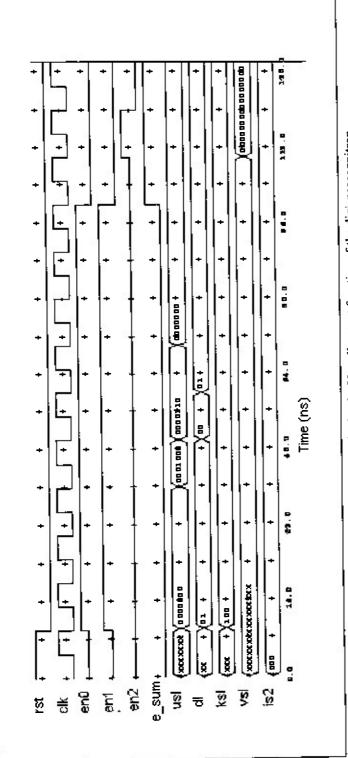

| Figure 5-3 : Logic simulation results for the Vc-cell output function of the digi-neocognitron.                 |    |

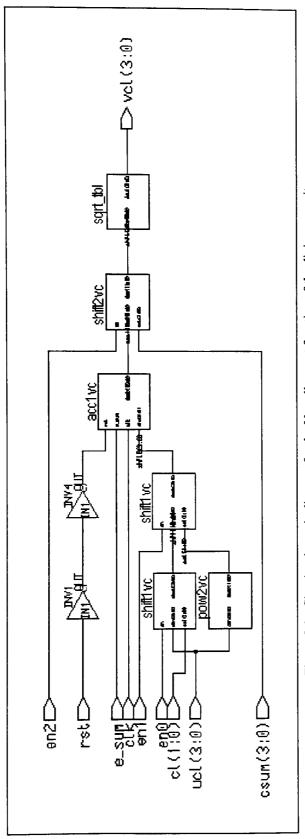

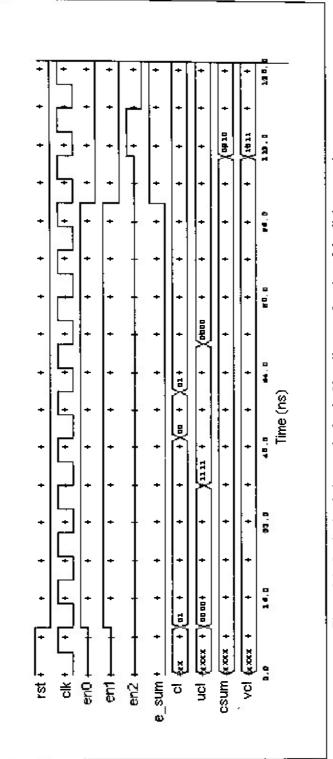

| Figure 5-4 : Circuit schematic diagram for the S-cell output function of the digi-neocognitron                  |    |

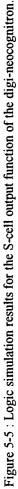

| Figure 5-5 : Logic simulation results for the S-cell output function of the digi-neocognitron                   |    |

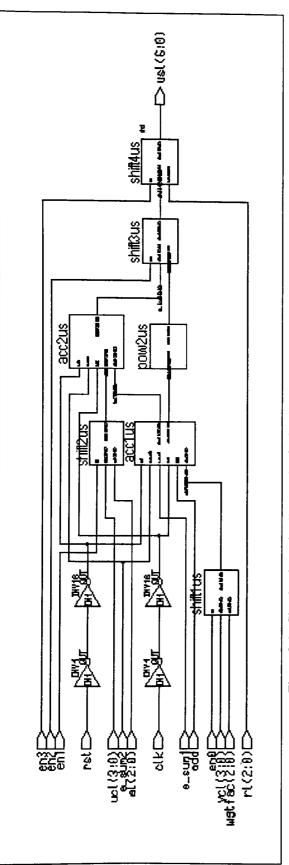

| Figure 5-6 : Circuit schematic diagram for the Vs-cell output function of the digi-neocognitron                 |    |

| Figure 5-7 : Logic simulation results for the Vs-cell output function of the digi-neocognitron.                 |    |

| Figure 5-8 : Circuit schematic diagram for the C-cell output function of the digi-neocognitron.                 |    |

| Figure 5-9 : Logic simulation results for the C-cell output function of the digi-neocognitron.                  | 69 |

|                                                                                                                 |    |

# LIST OF TABLES

| . 14 |

|------|

| 15   |

| 16   |

| 18   |

| 20   |

| 2    |

| 56   |

|      |

.

# **GLOSSARY OF TERMS**

| ANN    | Artificial Neural Networks                          |

|--------|-----------------------------------------------------|

| DNC    | Digi-Neocognitron                                   |

| CMOS   | Complementary Metal Oxide Semiconductor             |

| EEPROM | Electrically Erasable Programmable Read Only Memory |

| EPROM  | Erasable Programmable Read Only Memory              |

| IC     | Integrated Circuit                                  |

| I/O    | Input/Output                                        |

| LGB    | Lateral Geniculate Body                             |

| NC     | Neocognitron                                        |

| OCR    | Optical Character Recognition                       |

| PDP    | Parallel Distributed Processing                     |

| RAM    | Random Access Memory                                |

| ROM    | Read Only Memory                                    |

| VHDL   | VHSIC Hardware Description Language                 |

| VHSIC  | Very High Speed Integrated Circuit                  |

| VLSI   | Very Large Scale Integration                        |

,

### **CHAPTER 1**

### 1.0 Introduction

#### 1.1 What are Artificial Neural Networks?

The task of pattern processing is present in many real-world problems. This problem set includes areas such as image processing, speech processing, natural language processing, planning, forecasting, and optimization. Such problems deal with large amounts of data with mutually interacting factors. They also require that the information to be processed be precisely specified. Due to these two factors, conventional computers are not well suited for such types of problems. However, artificial neural networks (ANNs) or parallel distributed processing (PDP) models addresses both problems. These networks attempt to simulate the functionality of natural, biological brains in solving pattern processing problems.

ANNs are parallel signal processing networks comprised of a large number of processing elements or neurons which interact via weighted connections. These weighted connections are representative of the biological synapses in the neural system; they can be excitatory, causing the neurons to become active, or inhibitory, suppressing the neurons' outputs. Altering the value of the weights associated with the connections enables the network to adapt to changes in the environment. This procedure is referred to as learning and can be either supervised or unsupervised.

During supervised and unsupervised learning, numerous sets of training patterns are repeatedly presented to the network until it develops the ability to recognize those patterns. Typically, in supervised learning, the trainer presents a pair of patterns to the network consisting of an input pattern and the target output. The network then adjusts the weights of the processing elements based on a calculated error value. This is usually the difference between the expected output and the computed output of each processing element. In contrast, unsupervised learning attempts to classify the input patterns with no information about the expected output. The network detects the patterns' regularities and the grouping for

1

each to produce a consistent output. This type of model is referred to as biological model, and the process described above is known as "self-organization" [1].

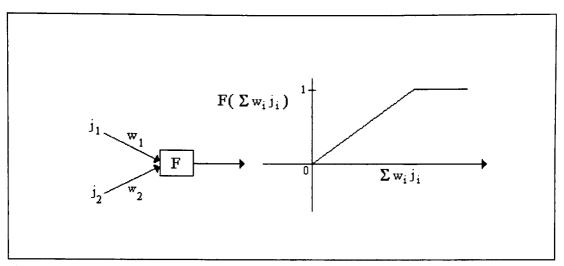

Figure 1-1 : A single processing element of a neural network and the non-linear function used to limit its response to the interval [0, 1].

A trained neural network recalls patterns based on information derived from the associations established between the input and output patterns during training. The activation of a processing element either induces or hinders the activation of the neurons to which it is connected, depending on whether the interconnections are excitatory or inhibitory. Consequently, the response of a processing element indicates the degree of confidence that its associated feature is present in, or absent from the input pattern.

During training and the pattern recognition task, the output of each neuron is passed through a non-linear function called an activation function. This function typically limits the response of the neuron to a particular interval. An example of an activation function that limits the neuron's output to the interval [0,1] is illustrated in Figure 1-1 [2].

# 1.2 Optical Character Recognition and the Neocognitron

The pattern processing task that this thesis investigates is optical character recognition (OCR). In OCR, a character must be recognized from its image pixels. This task can be fairly

straightforward or extremely difficult, depending on the nature of the image. For images consisting of cleanly printed, fixed-point symbols, simple template matching would suffice. However, when using multiple fonts or when the images are noisy, more sophisticated techniques such as neural networks are required. In handwritten character recognition the images can vary significantly, making this task very difficult even for neural networks. To solve the difficult task of handwritten character recognition, Fukushima designed an artificial neural network called the cognitron [3]. This neural network had the ability for hand-written character recognition, but its accuracy was dependent on the position of the stimulus pattern on the input plane. In essence, the same pattern presented at different positions on the input plane were judged to be different by the cognitron. Several years later, he extended the concept of the cognitron to develop what he called the neocognitron [4]. In its original design, the neocognitron is a real-valued, multi-layered self-organizing network which when trained, recognizes visual patterns with a high degree of accuracy. Unlike the cognitron, the neocognitron is not affected to some degree by deformations, scaling or shifting of the input patterns.

#### 1.3 Digital vs. Analog VLSI Artificial Neural Networks

Due to their intrinsic parallelism, the regularity of the processing elements, and the size of typical networks, ANNs are well suited for hardware implementation. Even though a neural network can comprise thousands of processing elements, each element is relatively simple and identical in all stages of the network. Therefore, a single processing element of each type can be constructed and replicated, leaving the greatest construction difficulty to be the interconnections of these components. Unfortunately, the hardware implementation is normally analog and does not take full advantage of the benefits and major advances in VLSI technologies. To do so, ANNs must be adapted to facilitate an all digital VLSI implementation.

Using digital VLSI to implement artificial neural networks offers many advantages over analog implementations. High density circuits with high speeds are possible with analog

implementations. However, analog circuits are susceptible to noise and temperature changes, and unavoidable inter-chip variations make manufacturing functionally equivalent circuits very difficult. In addition, the need for long-term storage for the connection weights requires special fabrication techniques. The largest shortfall however, is that the construction of such systems typically requires several integrated circuits (ICs). In such cases, care must be taken to guarantee the compatibility of the off-chip electrical environments. It is extremely difficult, if not impossible, to match board-level capacitive loads and time constants to their on-chip counterparts. Even though analog VLSI is well suited for parallel processing using locally connected networks, the system interface difficulties make it cumbersome for multi-chip ANNs [5].

In contrast, using digital VLSI to implement ANNs can be much easier because digital circuits are more tolerant of intra-chip and inter-chip variations, and are easily manufactured to be functionally identical. Also several devices such as static RAMs, EPROMs, EEPROMs and ROMs are available to enable long-term weight storage. Most neural networks utilize a convolution-like operation to compute the output of the neurons. Digital VLSI elements have been widely used to perform similar convolution-like operation suggests construction using time-division multiplexing. I/O bottlenecks may also exist in ANN solutions, but they are better resolved by digital techniques than analog. The use of input buffers, shift registers and pipelining to process the data also offer significant advantages relative to performance and the need for external storage [6], [7].

One concern with digital VLSI implementations of neural networks is the multiplication and division that must be performed on fixed-point digital values. These circuits consume a significant amount of silicon area which has a negative impact on performance. In addition to the multiplication and division operations, the neocognitron also requires square and square-root operations. The digital implementation of the neocognitron overcomes these potential problems by implementing the square and square-root functions

4

using look-up tables, and by using shift operations to perform multiplication and division. Hence, the neocognitron model implemented is ideal for digital VLSI.

This thesis utilizes the procedure described by White and Elmasry [8] for adapting a neocognitron to a digital neocognitron model. The network implemented consisted of nine stages with the last stage containing ten processing elements representative of the ten digits to be recognized. Unlike, the model described in [4], this neocognitron model utilized supervised training (learning with a teacher) to reinforce the modifiable synapses or weights of the network.

A VHDL Model of a Digi-Neocognitron Neural Network for VLSI

### **CHAPTER 2**

# 2.0 Theory of the Neocognitron Neural Network

#### 2.1 The Neocognitron Model Functions

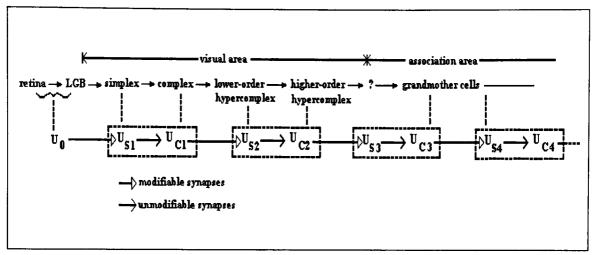

Unlike most ANNs which tend to have general purpose architectures, the neocognitron was designed primarily for handwritten character recognition, even though it has been applied to a variety of pattern recognition tasks. The neocognitron is a multi-layered hierarchical network consisting of several layers of neuron-like cells intended to simulate the human visual system. Its architecture is based on research performed by Hubel and Wiesel on the functionality and structure of the visual nervous system [9] - [11]. Figure 2-1 shows the relation between the Hubel and Wiesel model and the neocognitron [4]. Similar to the human visual system, upon completion of training, the neocognitron recognizes patterns with a high degree of generalization relatively independent of shifts in position, changes in size or shape, or the presence of deformations from the learned patterns. The neocognitron consists of a cascaded connection of a number of modular structures preceded by an input plane. The input plane, denoted by  $u_{o_3}$  is a two-dimensional photoreceptor array of cells corresponding to the lateral geniculate body (LGB) shown in Figure 2-1. Each of the remaining modular structures in the network is composed of two layers of cells connected in cascade.

The first layer of the module consists of S-cells which correspond to simple cells or lower-order hypercomplex cells. This is called the S-layer, and is denoted by  $u_{SI}$  representing the S-layer in the  $l^{th}$  module. The second layer of the module consists of C-cells and correspond to complex or higher-order hypercomplex cells. This is referred to as the C-layer, and the C-layer in the  $l^{th}$  module is denoted by  $u_{CI}$ .

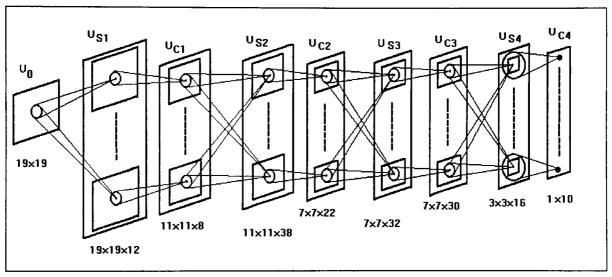

The S-cells and C-cells in a layer are alternately arranged into subgroups according to the stimulus features of their receptive field. Each subgroup is a two-dimensional array and is referred to as a cell-plane. Consequently, S-planes and C-planes represent cell planes consisting of S-cells and C-cells, respectively. All the cells in a single cell plane have input synapses of the same spatial distribution, and only the positions of the presynaptic cells are shifted in parallel from cell to cell. Therefore, all the cells in a single cell plane have receptive fields of the same function, but at different positions. The layer of C-cells at the highest stage of the network, is the recognition layer representing the final result of the pattern recognition task. Figure 2-2 illustrates the architecture of the neocognitron model implemented.

Figure 2-1: Correspondence between the model by Hubel and Wiesel and the neocognitron neural network.

In Figure 2-2 each of the large tetragons represents an S-layer or a C-layer, and the interior tetragons are S-planes or C-planes, respectively. The labeling below each layer indicates the dimensions of each cell-plane and the number of cell-planes in that layer. For example, 19x19x12 is interpreted as 12 cell-planes of dimension 19x19 pixels. In the neocognitron, S-cells and C-cells receive afferent connections from cells in its receptive field in the layer preceding it. This is indicated by the areas enclosed by the ellipses.

The S-cells of the neocognitron are feature extracting cells. These cells receive input from the preceding layer, detect the presence of specific features, and pass them to the following layer of C-cells. The input connections of the S-cells are variable and are modified during training, while those to the C-cells are unmodifiable and determined by the architecture. Through training, the S-cells come to extract features from the input patterns presented at the input layer. At lower stages of the network, the S-cells extract lines at different orientations, and at higher stages they extract higher-order features of the training patterns. Eventually, the complete pattern is recognized by the last layer of the network. The layer of C-cells following each S-layer is included in the neocognitron's architecture to allow for variability in the position of the features extracted by the S-layer. Each C-cell receives input from a group of S-cells that extract a specific feature from the stimulus pattern from slightly different positions. At least one cell in this group being active is sufficient to activate the corresponding C-cell. This reduces the dependence on the position of the feature detected, which is further reduced as the number of stages in the network increases.

Figure 2-2 : The architectural organization of the neocognitron neural network.

Not shown in Figure 2-2 are the inhibitory Vc-cells and Vs-cells of the neocognitron. These cells are included in the neocognitron to provide a shunting affect to reduce the likelihood of the excitatory S-cells and C-cells responding to irrelevant features.

The output of the four cell types of the neocognitron are determined by the proceeding numerical expressions [8]. In these equations n=(x,y) is the two-dimensional coordinate representing the cell's location, k is the current cell plane, and l represents the current layer.  $u_0$  is the input plane of the neocognitron, and the output of a cell in this plane is denoted by  $u_0(n)$ .  $u_{sl}$  and  $u_{cl}$  represents the S-layer and C-layer, respectively, in the  $l^{th}$  module of the

network. However, in layer 1,  $u_{Cl}$  is equivalent to  $u_0$ , the input plane. The corresponding inhibitory cells, Vc-cells and Vs-cells are denoted by  $v_{Cl}$  and  $v_{Sl}$ , respectively. The output of an S-cell in the  $k^{th}$  S-plane of the  $l^{th}$  module is described mathematically as follows:

$$u_{Sl}(k,n) = r_l \cdot \Phi \left[ \frac{1 + \sum_{K_l = 1}^{K_{Cl-1}} \sum_{k_l = 1} a_l(K, v, k) \cdot u_{Cl-1}(K, n+v)}{1 + \frac{r_l}{1 + r_l} \cdot b_l(k) \cdot v_{Cl}(n)} - 1 \right],$$

(1)

where

$$\Phi \begin{bmatrix} x \end{bmatrix} = \begin{cases} x & (x \ge 0) \\ 0 & (x < 0) \end{cases}$$

(2)

In Equation (1),  $a_i(K,v,k)$  and  $b_i(k)$  represents the strength of the variable excitatory and inhibitory connections from the preceding stage. During training the modifiable weights associated with an excitatory S-cell are reinforced only when its output is larger than the neighboring cells in its competitive region. When this occurs, the excitatory synapses  $a_i(K,v,k)$  and inhibitory synapses  $b_i(k)$  which are afferent to the S-cells of the  $\hat{k}^{th}$  S-plane are reinforced by

$$\Delta a_{l}\left(K, \mathbf{v}, \hat{k}\right) = q_{l} \cdot c_{l}(\mathbf{v}) \cdot u_{Cl-1}\left(K, \hat{n} + \mathbf{v}\right), \qquad (3)$$

and

$$\Delta b_l(\hat{k}) = q_l \cdot v_{Cl-1}(\hat{n}) , \qquad (4)$$

where

- $c_l(v)$  represents the efficiency of the unmodifiable excitatory weights and is a monotonically decreasing function with respect to |v|, and

- $q_l$  is a positive constant that determines the speed at which the excitatory and inhibitory synapses are reinforced. This parameter is commonly referred to as the learning rate.

This procedure implements a form of Hebbian learning that was first introduced in [3] to train the original cognitron. The representative S-cell selected for reinforcement is denoted by  $u_{Sl}(\hat{k}, \hat{n})$ , where  $\hat{k}$  is the cell plane being trained, and  $\hat{n}$  is the two-dimensional coordinate representing the cell's location on the plane. Another important parameter in Equation (1) is the selectivity parameter,  $r_l$ , which controls the intensity of the inhibition. A large value for  $r_l$ makes the S-cells' response more selective to a specific feature or pattern, and endows the network with a high ability to discriminate between patterns of different classes. However, this increase in selectivity also reduces the network's ability for deformation independent pattern recognition. Therefore, the value of  $r_l$  must be chosen at a point of compromise between these two contradictions. A detailed discussion on selecting values for  $r_l$  can be found in [12] and [13].

To facilitate the approximations required for the digital neocognitron model, modification of the neocognitron's inhibitory Vc-cell output was required. In the neocognitron described by Fukushima, the  $c_l(v)$  fixed weights which are usually taken as twoa dimensional Gaussian such that

$$K_{Cl} \cdot \sum_{\mathbf{v} \in A_l} c_l(\mathbf{v}) = 1, \tag{5}$$

was changed so that

$$c_i(0) = 1.$$

(6)

This change in the normalization provides a consistent range of values for the  $c_l(v)$  fixed weights but it requires division by the value *csum* in the Vc-cell output equation. This ensures that the Vc-cell output remains unaffected by the normalization, and that the output of a Vccell is consistent with the original neocognitron. The new Vc-cell output equation of the neocognitron model is a weighted root-mean-square average of the preceding level C-cells' output over the same connection area  $A_b$ , and is given by

$$v_{Cl}(n) = \sqrt{\frac{1}{csum} \sum_{K=1}^{K_{Cl-1}} \sum_{v \in A_l} c_l(n) \cdot u_{Cl-1}^2(K, n+v)} , \qquad (7)$$

where

.

$$csum = \sum_{K=1}^{K_{Cl-1}} \sum_{\nu \in A_l} c_l(\nu).$$

(8)

With the normalization requirement of Equation (6), the first learning rule shown in Equation (3) becomes

$$\Delta a_{l}\left(K,\boldsymbol{v},\hat{\boldsymbol{k}}\right) = q_{l} \cdot \frac{c_{l}(\boldsymbol{v})}{csum} \cdot \boldsymbol{u}_{Cl-1}\left(K,\hat{\boldsymbol{n}}+\boldsymbol{v}\right). \tag{9}$$

The excitatory C-cells of the neocognitron have a shunting-type inhibitory input,  $v_{sl}(n)$ , similar to S-cells, but their outputs show a saturation characteristic. The output of a C-cell in the  $k^{th}$  C-plane of the  $l^{th}$  module is given by

$$u_{Cl}(k,n) = \Psi \left[ \frac{1 + \sum_{k=1}^{K_s} j_l(K,k) \sum_{v \in D_l} d_l(v) \cdot u_{Sl}(k,n+v)}{1 + v_{Sl}(n)} - 1 \right],$$

(10)

where  $\Psi$ [] is the threshold characteristic of the C-cell defined by

$$\Psi[x] = \begin{cases} \frac{x}{\alpha_i + x} & (x \ge 0), \\ 0 & (x < 0). \end{cases}$$

(11)

This function limits the response of the C-cells to the interval [0,1]. The  $d_l(v)$  term in Equation (10) is a two-dimensional Gaussian similar to  $c_l(v)$ , and denotes the strength of the fixed excitatory connections. The normalization change of Equation (6) is also applicable to the  $d_l(v)$  fixed weights. The term  $j_l(K,k)$  is used to indicated how the S-planes which extract similar features are combined for input to a C-plane.  $j_l(K,k)$  takes on a value of one or zero depending on whether or not the synaptic connections really exist from the  $K^{th}$  S-plane to the  $K^{th}$  C-plane. Finally, the parameter  $\alpha_l$  in Equation (11) is a positive constant which specifies the degree of saturation of the C-cells.

In Equation (10),  $v_{st}(n)$  is the output of the inhibitory Vs-cells defined as a weighted average of the S-cells' output of the preceding stage within the receptive field of n. The Vscell provides a form of lateral inhibition and are optional in the neocognitron. Typically, only the final layer in the neocognitron contains Vs-cells. The output of a Vs-cell is given by the following equation:

$$v_{sl}(n) = \frac{1}{K_{sl}} \sum_{K=1}^{K_{cl-1}} \sum_{\nu \in A_l} d_l(\nu) u_{sl}(K, n+\nu)$$

(12)

#### 2.2 The Digi-Neocognitron Model Functions

To implement the neocognitron neural network using digital VLSI, the model functions and fixed weight values described in the previous section were modified. This resulted in a new neural network model that the authors of [8] called the digi-neocognitron (DNC). In the DNC model, multiplications and divisions are replaced with shift operations by converting the multiplication and division factors to powers of 2. This is a significant benefit since shifters are easily implemented in digital hardware; as such, they require less silicon area and reduce the propagation delays associated with multipliers. The complex functions, square and square root, of the neocognitron are replaced by look-up tables, and can be implemented with simple combinatorial logic or memory arrays.

To understand the DNC model functions, a discussion on performing power of 2 representations and the notations used in these functions is necessary. The DNC model uses a single-term power of 2 approximation in all cases except one, for which a two-term approximation is required. The notation used to describe the DNC model functions is similar to that used in [14], with modifications to accommodate positive values and fractions.

The set of admissible values in a single-term power of 2 representation is denoted as  $P_{m,n} = \{2^m, 2^{m+1}, \dots, 2^{n-1}, 2^n\}$  where *m* and *n* are integers and  $m \le n$ . Also,

$$\langle x \rangle_{2^m,2^n;b} \tag{13}$$

denotes rounding x to the nearest term in the representation  $P_{m,n}$  with bias  $b \in [0,1]$  to rounding up. If the value of x is outside the range of the representation, the appropriate endpoint is chosen as the approximation. A bias of 0.0 selects the power of 2 that is less than or equal to the number; a bias of 1.0 selects that which is greater than or equal, and a bias of 0.5 selects the closest power of 2. These representations are denoted by the following set of equations.

$$\langle x \rangle_{2^{m},2^{n};le} = \langle x \rangle_{2^{m},2^{n};00} \qquad \langle x \rangle_{2^{m},2^{n};ge} = \langle x \rangle_{2^{m},2^{n};10}$$

$$\langle x \rangle_{2^{m},2^{n}} = \langle x \rangle_{2^{m},2^{n};05}$$

$$(14)$$

An extension of the concepts for a single-term power of 2 representation is used to define the set of possible values for the two-term power of 2 approximations. The representation used is

$$P_{m,n}^{2} = \left\{ y | y = 2^{p} + s \cdot 2^{k}, y > 0 \right\}$$

where *m* and *n* are integers, with  $m \le n, p, k \in \{m, m+1, ..., n-1, n\}$  and  $s \in \{-1, 0, 1\}$ The rounding used to determine the nearest value for *x* in the representation  $P_{m,n}^2$  is

$$\langle\langle x \rangle \rangle_{2^m, 2^n}$$

(15)

with the usage of the bias equivalent to that for the single-term approximation.

Following is a summary of the preprocessing performed on the neocognitron model functions to obtain the output functions for the digi-neocognitron model. A detailed discussion of the steps described below can be found in [8]. The bit ranges of the inputs and outputs of the four cell types are represented with 4 bits to the right of the binary point. In cases where the output of a cell is more than four bits it is truncated. This restriction also requires a change in the lower level C-cells or the input layer. In the input pattern, each pixel is represented by four bits to the right of the binary point, resulting in 0.0000 (0.0) for a zero pixel and 0.1111 (0.9375) for a one pixel, where zero indicates a white pixel and one a black pixel. Also, the s-cell's output is represented as seven bits (with 4 binary places) allowing outputs up to 8. This provides a safety margin because the digi-neocognitron model

approximation of the modifiable weights as powers of 2 can result in S-cell outputs greater than 1 if the excitatory weights are rounded up, and the inhibitory weights are rounded down. In the model implemented, the S-cell's output was always less than 2.

| Fixed Weight<br>c <sub>l</sub> , d <sub>l</sub><br>Interval | Fixed Weight<br>$\overline{c_i}, \overline{d_i}$<br>Approximation | Interpretation |

|-------------------------------------------------------------|-------------------------------------------------------------------|----------------|

| [0.0, 0.1)                                                  | 0                                                                 | Force 0        |

| [0.1, 0.4]                                                  | 1/4                                                               | Shift 2 R      |

| [0.4, 0.75)                                                 | 1/2                                                               | Shift 1 R      |

| [0.75, 1.0]                                                 | 1                                                                 | Shift 0        |

Table 2-1 : Preprocessing approximations for the fixed weight connections.

To obtain the output of the inhibitory Vc-cell, the normalization change of Equation (6) is required. This change provides a consistent range of values for the  $c_l$  fixed weights to enable approximations by values restricted to zero and powers of 2. These approximations shown in Table 2-1 are used to replace the multiplication by a shift operation in the Vc-cell output function. With these approximations, Equation (8) now becomes

$$C_{\Sigma} = \sum_{\kappa=1}^{K_{Cl-1}} \sum_{\nu \in A_l} \overline{c_l(\nu)}, \qquad (16)$$

where the overbar indicates a power of 2 approximation. The division in Equation (7) is then replaced by a shift operation using a power of 2 approximation of Equation (16) according to the following rules:

$$\overline{C_{\Sigma}} = \begin{cases} \langle C_{\Sigma} \rangle_{1,2048,le,} & l = 1 \\ \langle C_{\Sigma} \rangle_{1,2048,ge,} & l > 1 \end{cases}$$

(17)

where l represents the layers of the network.

| Input $\overline{u_c}$ (binary) | Input $\overline{u_c}$ (decimal) | Power of 2 ( $\overline{u_c}$ ) Shift Control |

|---------------------------------|----------------------------------|-----------------------------------------------|

| 0000                            | 0.0000                           | Force 0                                       |

| 0001                            | 0.0625                           | Force 0                                       |

| 0010                            | 0.1250                           | Force 0                                       |

| 0011                            | 0.1875                           | Shift 2 R                                     |

| 0100                            | 0.2500                           | Shift 2 R                                     |

| 0101                            | 0.3125                           | Shift 1 R                                     |

| 0110                            | 0.3750                           | Shift 1 R                                     |

| 0111                            | 0.4375                           | Shift 1 R                                     |

| 1000                            | 0.5000                           | Shift 1 R                                     |

| 1001                            | 0.5625                           | Shift 0                                       |

| 1010                            | 0.6250                           | Shift 0                                       |

| 1011                            | 0.6875                           | Shift 0                                       |

| 1100                            | 0.7500                           | Shift 0                                       |

| 1101                            | 0.8125                           | Shift 0                                       |

| 1110                            | 0.8750                           | Shift 0                                       |

| 1111                            | 0.9375                           | Shift 0                                       |

Table 2-2 : Power of 2 approximation for squaring the output of a c-cell.

With the preprocessing approximations described above, the Vc-cell output of the DNC model is given by

$$\overline{v_{Cl}(\boldsymbol{n})} = \sqrt{\frac{1}{\overline{C_{\Sigma}}} \sum_{K=1}^{K_{Cl-1}} \sum_{\boldsymbol{\nu} \in A_l} \overline{c_l(\boldsymbol{\nu})} \cdot \overline{u_{Cl-1}(K, \boldsymbol{n}+\boldsymbol{\nu})}^2}$$

(18)

In this equation, the square of the C-cell output is obtained by using a power of 2 approximation of  $\overline{u_c}$ , as shown in Table 2-2, to control the shift operation eliminating the need for a multiplier. A shifter is used here as opposed to a look-up table because the square operation is done for every term in the summation and can be calculated in parallel using some form of pipelining. Also, in this instance a shifter requires less area than a look-up table.

| Input<br>(decimal) | Input<br>(binary) | Output<br>(binary) | Output<br>(decimal) |

|--------------------|-------------------|--------------------|---------------------|

| 0.0000             | 0.0000            | 0.0011             | 0.1875              |

| 0.0625             | 0.0001            | 0.0100             | 0.2500              |

| 0.1250             | 0.0010            | 0.0110             | 0.3750              |

| 0.1875             | 0.0011            | 0.0111             | 0.4375              |

| 0.2500             | 0.0100            | 0.1000             | 0.5000              |

| 0.3125             | 0.0101            | 0.1001             | 0.5625              |

| 0.3750             | 0.0110            | 0.1010             | 0.6250              |

| 0.4375             | 0.0111            | 0.1011             | 0.6875              |

| 0.5000             | 0.1000            | 0.1011             | 0.6875              |

| 0.5625             | 0.1001            | 0.1100             | 0.7500              |

| 0.6250             | 0.1010            | 0.1101             | 0.8125              |

| 0.6875             | 0.1011            | 0.1101             | 0.8125              |

| 0.7500             | 0.1100            | 0.1110             | 0.8750              |

| 0.8125             | 0.1101            | 0.1110             | 0.8750              |

| 0.8750             | 0.1110            | 0.1111             | 0.9375              |

| 0.9375             | 0.1111            | 0.1111             | 0.9375              |

Table 2-3 : Square root approximation for the output of a Vc-cell.

However, because the square root is computed once for each Vc-cell, it is implemented using the look-up table shown in Table 2-3.

To obtain the S-cell output function for the DNC model, the modifiable weights  $a_l(K, v, k)$  and  $b_l(k)$  are approximated by powers of 2. To improve alignment with the power of 2 representation, it is suggested that these weights be scaled by a factor  $f_l$  as shown in the equations below. The weight factor  $r_l \cdot b_l(k)/(1 + r_l)$  from Equation (1) is approximated by one or two power of 2 terms defined by

$$\overline{r_i \cdot b_i(k)/(1+r_i)} = \left\langle f_i \cdot r_i \cdot b_i(k)/(1+r_i) \right\rangle_{1,64}$$

(19)

or

$$\overline{r_{l} \cdot b_{l}(k)/(1+r_{l})} = \left\langle \left\langle f_{l} \cdot r \cdot b_{l}(k)/(1+r_{l}) \right\rangle \right\rangle_{1,64}.$$

(20)

At lower levels, a single-term approximation is sufficient, however, at higher levels, a twoterm power of 2 approximation is required to avoid significant loss of precision due to rounding. The approximation for the  $a_i$  weights is done after scaling by  $f_i$  using the following equation:

$$\overline{a_{l}} = \begin{cases} \left\langle f_{l} \cdot a_{l} \right\rangle_{\frac{1}{8},8} & f_{l} \cdot a_{l} \ge \frac{1}{16} \\ 0 & Otherwise. \end{cases}$$

(21)

$r_i$ , which is multiplied by the function  $\Phi[x]$  in Equation (1), is also represented by a power of 2 approximation. This is obtained using

$$r_{i} = \langle r_{i} \rangle_{1,16,\frac{2}{3}}$$

, (22)

which selects the closest power of 2 representation in the range, but rounds up if  $r_i$  is in the upper two-thirds of the range and down otherwise. Applying these approximations to Equation (1), the digi-neocognitron's S-cell output is given by

$$\overline{u_{SI}(k,n)} = \overline{r_i} \cdot \Phi\left[\frac{E - IC}{1 + IC}\right]$$

(23)

where

$$\Phi [x] = \begin{cases} x & (x \ge 0) \\ 0 & (x < 0) \end{cases}$$

The excitatory term *E*, is given by

$$E = \sum_{k=1}^{K_{Cl-1}} \sum_{\boldsymbol{\nu} \in A_l} \overline{a_l(K, \boldsymbol{\nu}, k)} \cdot \overline{u_{Cl-1}(K, \boldsymbol{n} + \boldsymbol{\nu})}, \qquad (24)$$

and the inhibitory term IC, is given by

$$IC = \overline{r_i \cdot b_i(k)/(1+r_i) \cdot v_{Cl}(n)}.$$

(25)

The function 1/(1 + IC) in Equation (23) is approximated by the function 1/IC2 where IC2 is a power of 2 as defined in Table 2-4. The resulting S-cell output function is

$$\overline{u_{sl}(k,n)} = \begin{cases} \overline{r_l} \cdot \left[\frac{E - IC}{IC2}\right] & E > IC \\ 0 & Otherwise. \end{cases}$$

(26)

The output of the optional Vs-cells, which provides a form of lateral inhibition to the C-cells, is given by

$$\overline{v_{Sl}(n)} = \frac{1}{\overline{K_{Sl}}} \sum_{\kappa=1}^{K_S} \sum_{\nu \in D_l} \overline{d_l(\nu)} \cdot \overline{u_{Sl}(K, n+\nu)}.$$

(27)

Table 2-4 : Power of 2 approximations for 1/(1+I) inhibit function for the S-cells and C-cells.

| IC, IS<br>Interval | IC2, IS2<br>Approximation | Interpretation |

|--------------------|---------------------------|----------------|

| < 0.5              | 1                         | Shift 0        |

| [0.5, 2.0)         | 2                         | Shift 1 R      |

| [2.0, 4.5]         | 4                         | Shift 2 R      |

| [4.5, 10.0)        | 8                         | Shift 3 R      |

| [10.0, 21.0]       | 16                        | Shift 4 R      |

| ≥ 21.0             | 32                        | Shift 5 R      |

As with the  $c_l(v)$  modifiable weights, the  $d_l(v)$  fixed weights are two-dimensional Gaussian and use the same normalization,  $d_l(0) = 1$ . The approximation for  $d_l(v)$  is identical to that used for  $c_l(v)$  as shown in Table 2-1.  $K_{sl}$  represents the number of S-planes in the previous level, and is approximated using

$$\overline{K_{Sl}} = \left\langle K_{Sl} \right\rangle_{1,64;le} \tag{28}$$

so that the division  $1/K_{Sl}$  can be replaced by a shift operation.

The power of 2 approximation required for the C-cell output is performed on the  $d_i(v)$  fixed weights as discussed above, and on the saturation parameter  $\alpha_i$  by

$$\overline{\alpha_{l}} = \left\langle \alpha_{l} \right\rangle_{\frac{1}{32}, 1; le}.$$

<sup>(29)</sup>

The resulting C-cell output equation is

$$\overline{u_{CI}(k,n)} = \Psi\left[\frac{E-IS}{1+IS}\right],\tag{30}$$

where the excitatory term E, is defined as

$$E = \sum_{k=1}^{K_{s}} j_{l}(K,k) \sum_{\boldsymbol{v} \in D_{l}} \overline{d_{l}(\boldsymbol{v})} \cdot \overline{u_{sl}(k,\boldsymbol{n}+\boldsymbol{v})}, \qquad (31)$$

and the inhibitory term IS, is given by

$$IS = \overline{v_{Sl}(n)}.$$

(32)

Similar to the S-cell output, the function 1/(1 + IS) in Equation (30) is approximated by the function 1/IS2, where *IS2* is a power of 2 as defined in Table 2-4. This results in the following output equation for the C-cells:

$$\frac{1}{u_{Cl}(k,n)} = \begin{cases} \Psi\left[\frac{E-IS}{IS2}\right] & E > IS \\ 0 & Otherwise. \end{cases}$$

(33)

The final output of the C-cells is obtained by approximating the saturation function  $\Psi[x]$ , which is implemented using the look-up table shown in Table 2-5. This function is redefined for the digi-neocognitron model as

$$\overline{\Psi[x]} = \frac{z}{1+z}, \quad z = x/\overline{\alpha_1}.$$

(34)

| Input<br>(decimal) | Input<br>(binary) | Output<br>(binary) | Output<br>(decimal) |

|--------------------|-------------------|--------------------|---------------------|

| 0.00               | 00.00             | 0.0000             | 0.0000              |

| 0.25               | 00.01             | 0.0011             | 0.1875              |

| 0.50               | 00.10             | 0.0101             | 0.3125              |

| 0.75               | 00.11             | 0.0111             | 0.4375              |

| 1.00               | 01.00             | 0.1000             | 0.5000              |

| 1.25               | 01.01             | 0.1001             | 0.5625              |

| 1.50               | 01.10             | 0.1010             | 0.6250              |

| 1.75               | 01.11             | 0.1010             | 0.6250              |

| 2.00               | 10.00             | 0.1011             | 0.6875              |

| 2.25               | 10.01             | 0.1011             | 0.6875              |

| 2.50               | 10.10             | 0.1011             | 0.6875              |

| 2.75               | 10.11             | 0.1100             | 0.7500              |

| 3.00               | 11.00             | 0.1100             | 0.7500              |

| 3.25               | 11.01             | 0.1100             | 0.7500              |

| 3.50               | 11.10             | 0.1100             | 0.7500              |

| 3.75               | 11.11             | 0.1101             | 0.8125              |

| >                  | >                 | 0.1111             | 0.9375              |

| Table 2-5 : Z/(1+Z) | ) look-up table for | the output of a C-cell. |

|---------------------|---------------------|-------------------------|

|---------------------|---------------------|-------------------------|

,

### **CHAPTER 3**

# 3.0 Software Models for the Neocognitron and the Digi-Neocognitron

Prior to designing the digital VLSI version of the neocognitron neural network model, some preliminary steps were required. The basic neocognitron model was constructed, trained, simulated and subsequently used to develop the digi-neocognitron. This also provides a comparative tool for the DNC model, which is necessary to determine if the pattern recognition capability of the digi-neocognitron is similar to that of the neocognitron. Constructing a DNC model is a viable alternative to an neocognitron model only if its capability for pattern recognition is similar to that of the neocognitron model. Both the neocognitron and digi-neocognitron were implemented using the C-programming language on a SUN SPARCStation 20.

#### 3.1 Converting from a Neocognitron to a Digi-Neocognitron Model

To obtain the digital version of the neocognitron with similar pattern recognition capability, White and Elmasry developed a procedure for converting a neocognitron model to a digi-neocognitron [8]. However, this method utilizes the inherent fault tolerant characteristics of the neocognitron, and its unsupervised learning capability to compensate for inaccuracies that result from implementing the required approximations. Because the model implemented utilized supervised learning, some modifications to this methodology were required. The procedure developed consists of the following steps.

1) Do unconstrained simulation, including learning, with the neocognitron model in order to get something that works for the particular problem. If there is not already an existing neocognitron model also incorporate step 2.

2) Change the neocognitron model to use the approximate fixed weights in Table 2-1. If feasible, also use appropriate powers of 2 for the selectivity  $(r_i)$  and saturation  $(\alpha_i)$  parameters. This recognizes that some of the DNC model preprocessing approximations can be treated as just another set of

21

neocognitron model parameters. Repeat simulation, including learning, with the neocognitron model and adjust the learning rate  $(q_i)$  to develop weights that are appropriate for the DNC representations, as in Equations (19), (20) and (21).

3) Preprocess level 1 to create level 1 DNC model approximations.

4) Run the DNC model simulator on level 1 for all input patterns in the training set and compare with level 1 neocognitron model outputs.

5) If necessary, repeat steps 2, 3, and 4 in order to obtain good weight approximations, trying different scaling factors, changing the amount of training, or adjusting the cell's inhibitory input for each S-plane.

6) Use the level 1 outputs from the DNC model to retrain level 2 of step 2 in the neocognitron Model. This is a critical because the level 2 feature detectors must be developed with inputs from the lower levels that are representative of what will be seen in the DNC model. Otherwise, there will not be enough similarity between lower-level outputs and higher-level feature detectors to have a robust conversion of the neocognitron model pattern recognition capabilities to the DNC model.

7) Preprocess level 2 to create level 2 DNC model approximations.

8) Repeat this process for all levels in the architecture; e.g., if there are three or more levels, next run the DNC simulator on level 2, and use these outputs to retrain level 3 in the neocognitron model.

9) Use the DNC model to check final level outputs for all input patterns using all levels in the neural network.

### 3.2 Implementation of the Neocognitron Model

The neocognitron model constructed consisted of four levels of S-cell and C-cell planes, as shown in Figure 2-2. Also shown at the bottom of Figure 2-2 are the dimensions of the cell planes in each layer. Though not shown, each layer contains a Vc-cell plane, which provides inhibitory input to the S-cells. In addition, the last layer of the network which represents the patterns to be recognized, contains a Vs-cell plane which provides a form of lateral inhibition to the C-cells. The dimensions of these inhibitory planes are identical to the

excitatory planes that receive their outputs. This network is similar to those described in [9] and [10] with some modifications to the architecture and parameters.

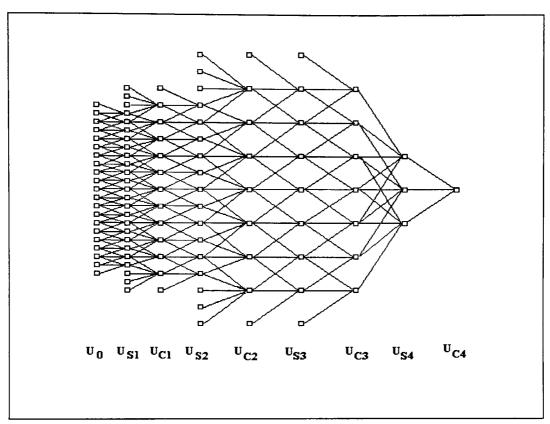

Figure 3-1 : A one-dimensional view of the interconnections between the cells of the different layers in the neocognitron.

As shown in Figure 2-2, the neocognitron is interconnected in a cascaded manner in which the size of the receptive field of a cell is dependent on the layer in which the cell is located. The deeper the cell is in the network, the larger is the cell's receptive field. Consequently, the density of the cells in each plane decreases as the size of the receptive field increases. Figure 3-1 shows a one-dimensional view of how the cell planes of each layer are inter-connected. Only a single plane is shown for each layer since the connection scheme is identical for all planes in the layer. Figure 3-1 also indicates the size of the receptive field of each layer. This connection scheme must be followed if the neocognitron is to be effective in its pattern recognition capability. The thinning out of the cell planes as the number of stages

increases is also necessary. This is required since the information in adjacent cells is almost identical due to smearing of the S-cell outputs through the receptive field averaging.

To calculate the output of a neuron, a non-linear convolution-like operation is performed on two 3x3 or 5x5 masks. However, edge pixels have a connection area that is smaller than the mask size of the remaining pixels in the plane thus complicating this convolution operation. Therefore, care must be taken when computing the output of pixels on the edge of a cell plane to avoid loosing any feature detector outputs. To resolve this dilemma, some planes are oversized to ensure that all cells in the plane have identical size receptive fields. The outputs of these cells are always zero, therefore no computational time is required. In Figure 3-1, these cells do not receive inputs from the preceding plane.

In a software implementation, the cost of oversizing the cell planes is negligible. However, in a hardware implementation, a trade-off between the cost of oversizing, and the cost of the additional circuitry that would be required to determine a cell's receptive field must be considered.

In performing the convolution operation, one of three different two-dimensional masks is required, an a, c or d mask. A mask is associated with each cell in the plane and, if implemented in this manner, would require a substantial amount of memory. However, the cells of each plane all extract the same feature from the input pattern and have an identical set of connections. This can be easily exploited in a software simulation to reduce memory requirements. In the model constructed, a different a mask and a common c mask is used for each plane in an S-layer. For example, in layer  $u_{S1}$  there are 12 planes and one in the input plane  $u_0$ . Correspondingly, there are 12 different a masks and one c mask. A single c mask is required in all layers, but the number of a masks depends on the number of S-planes in the current stage and the number of C-planes in the preceding stage. Layer  $u_{32}$  consists of 38 planes and  $u_{C1}$  contains 8 planes; therefore, the number of distinct a masks required is 38x8. Also, a d mask is associated with each C-plane and S-plane pair, but each mask is identical. Therefore, like the c mask, a single d mask is used for all cell planes in each C-layer. Critical to the training and the performance of the neocognitron is the selection of the values for its parameters. The learning rate  $q_i$ , the saturation parameter,  $\alpha_i$ , the selectivity parameter  $r_i$ , and the fixed excitatory weights,  $c_i(v)$  and  $d_i(v)$ , must be chosen carefully to provide an acceptable balance between the training time, and the neocognitron's pattern recognition capability.

The learning rate  $q_i$ , determines the amount of reinforcement of the modifiable synapses  $b_i(k)$  and  $a_i(K, v, k)$ . For unsupervised training, the value chosen for the learning rate is paramount if the network is to be trained successfully. However, for supervised training as used in this implementation,  $q_i$  is often chosen sufficiently large so that the training of each layer can be completed in a single iteration. Since the primary purpose of constructing the neocognitron is to facilitate the development of the digi-neocognitron, the learning rate for each layer is chosen so that the final weight values will be similar to those of the digineocognitron. The values utilized for the learning rate were  $q_i = 45.0$ ,  $q_2 = 175.0$ ,  $q_3 = 285.0$ and  $q_4 = 625.0$ .

The values chosen for the saturation parameter,  $\alpha_l$ , were identical to those used for the neocognitron described in [13]. The model implemented here was based on that described by the authors of [13]. Therefore, these values were an appropriate starting point, which proved adequate for this implementation. The values used were  $\alpha_l = \alpha_2 = \alpha_3 = 0.25$  and  $\alpha_4 = 1.0$ .

The selectivity parameter was chosen as follows:  $r_1 = 1.7$ ,  $r_2 = 5.0$ ,  $r_3 = 1.5$  and  $r_4 = 1.0$ . This value determines the efficiency of the inhibitory inputs to the S-cells and controls the selectivity during feature extraction.  $r_1 = 1.7$  is chosen for  $u_{s_1}$  because the connection area for this layer is 3x3. The S-cell will yield a non-zero output when the stimulus feature detected contains up to two additive elements of noise, or one additive and one subtractive element. However, the cell yields a zero output if the stimulus feature has two or more subtractive elements of noise. With  $r_2 = 5.0$  the S-cells' output will be non-zero with up to one additive or one subtractive element of noise, and zero with both. Such selectivity is necessary because the training patterns are specific portions of the 10 numerals to be recognized. In layers 3 and 4 the selectivity parameter is chosen to be  $r_3 = 1.5$  and  $r_4 = 1.0$ . The s-cells' selectivity should not be too large, since these layers are trained on complete patterns and must be more tolerant of deformations.

The exact values chosen for the fixed weights,  $c_i(v)$  and  $d_i(v)$ , are not important as long as Equation (6) is satisfied. The values for  $c_i(v)$  is given by

$$c_l(v) = \gamma_l^{|v|} \tag{35}$$

where  $\gamma_1 = \gamma_2 = \gamma_3 = 0.7$  and  $\gamma_4 = 0.6$ .  $d_i(v)$  is given by

$$d_{l}(v) = \overline{\delta_{l}} \cdot \delta_{l}^{|v|} \tag{36}$$

where  $\overline{\delta_1} = \overline{\delta_2} = 1.0$ ,  $\overline{\delta_3} = 0.6$  and  $\overline{\delta_4} = 0.3$ ;  $\delta_1 = 0.7$ ,  $\delta_2 = 0.6$ ,  $\delta_3 = 0.5$  and  $\delta_4 = 0.8$ . Both equations are taken from [15] but are used with different parameters since the patterns to be recognized and the architecture of this implementation differs from that described in [15]. In Equations (35) and (36),  $|\nu|$  is the normalized distance between the cell located at the position  $\nu$  and the center of the receptive field.

The software for neocognitron's model functions are shown in Appendix A-1. These functions utilizes two routines that are not included in the Appendix. The first, *getCfield()*, is utilized by the Vc-cell and S-cell output functions to determine the cell's receptive field on the C-planes in the preceding stage. Similarly, the function *getSfield()* determines the receptive field of a Vs-cell and C-cell on the S-planes in the preceding stage.

#### 3.2.1 Training the Neocognitron

The neocognitron can learn to recognize a set of patterns via unsupervised or supervised training. The latter training methodology was used to train the software model constructed. Training of the neocognitron was performed layer by layer, beginning at the lowest level and proceeding to the highest level. A training pattern was presented to the input layer and the layer to be trained was selected. The inhibitory Vc-cell outputs are first computed since they are required in the S-cell computation. After the outputs of all S-planes are calculated, the weight updates to the modifiable inhibitory and excitatory connections are made according to Equations (4) and (9), respectively. The cell at the center of each cell plane is always selected as the representative,  $u_{Sl}(\hat{k}, \hat{n})$ , for that plane. This requires that the training pattern be centered on the input plane to ensure that the complete pattern is within the receptive field of the representative cell. It is necessary to train only a single cell in each plane since all the cells in a given plane have the same receptive field and extract the same feature from the input pattern. For layers other than the first this training procedure is also used. However, in those layers it is necessary to calculate the output of all preceding S-layers and C-layers even though no updates to the weights are performed. This is possible since these layers have already been trained and will recognize those features, for which they were trained, that are present in the current training pattern.

Figure 3-2: Patterns used to train the 12 cell planes of layer  $u_{SI}$ . How these planes are combined at the input stage of layer  $u_{CI}$  is indicated on the right of the training patterns.

The  $u_0$  input plane is oversized to 21x21 as a result of the 3x3 receptive field of the cell in layer  $u_{SI}$ . This photoreceptor array is the input to the 12-25x25 S-planes in layer  $u_{SI}$ . The cell planes in this stage are oversized to accommodate the 5x5 receptive field of the cells in the next stage. Shown in Figure 3-2 are the 12 patterns used to train layer  $u_{SI}$ . These 12 S-planes, with a 3x3 connection area, extracts line components at different orientations from the input pattern. Due to the similarity between some of these lines, they are combined at layer  $u_{CI}$  thus requiring only 8 C-planes in this stage. These 8 cell planes are thinned out from the previous stage to 13x13 and have a 5x5 connection area. In this and the remaining stages of the network, the value  $j_1(K, k)$  in Equation (10) indicates how the S-planes are combined for input to the C-planes. K indicates the current C-plane, and k is a one if the S-planes are to be joined and zero otherwise.

Figure 3-3: Patterns used to train the 38 cell planes of layer  $u_{S2}$ . How these planes are combined at the input stage of layer  $u_{C2}$  is indicated on the right of training patterns.

There are 38-17x17 S-planes in stage  $u_{S2}$  which receive input from the 8 C-planes in layer  $u_{C1}$  through a 3x3 connection area. Thinning out is not performed in this stage but, all cell planes are oversized. Figure 3-3 illustrates the 38 sets of training patterns used to train this stage. Due to the 2-to-1 thinning of the cells in layer  $u_{C2}$  from  $u_{S1}$ , four patterns are used to train each S-plane at this stage. Each training set consists of the identical pattern presented at four different locations, by shifting it both vertically and horizontally on the input plane. Training each cell plane using four patterns was necessary to ensure each plane's ability to extract its assigned feature. How these 38 cell planes are combined for input to the 22 cell planes in layer  $u_{C2}$  is indicated to the right of the training patterns in Figure 3-3.

Figure 3-4 : Patterns used to train the 32 cell planes in layer  $u_{S3}$ . How these planes are combined at the input stage of layer  $u_{C3}$  is indicated on the right of the training patterns.

At the third stage of the neocognitron, the 32-9x9 S-planes in layer  $u_{S3}$  receive input from the 22 C-planes in layer  $u_{C2}$  through a 3x3 connection area. The training patterns for the 32 S-planes in this stage are shown in Figure 3-4. This training set consists of partial patterns and some of the actual patterns that are to be recognized by the network. Two or three patterns of varying size, shape and deformations are used to train the 32 planes in this layer. These 32 S-planes are combined as indicated to the right of the cell planes in Figure 3-4 for input to the 30  $u_{C3}$  planes. Thinning out of the cells in the planes from those in the previous layer is not performed at this stage but each plane is oversized.

Figure 3-5 : Patterns used to train the 16 cell planes in layer  $u_{S4}$ . How these planes are combined at the input stage of layer  $u_{C4}$  is indicated on the right of the training patterns.

The patterns used for training the final S-layer,  $u_{s4}$ , are illustrated in Figure 3-5. There are 16-3x3 cell planes in this layer, each with a 5x5 receptive field. Each of these cell are trained using one or two complete patterns. The outputs of these 16 S-planes are the inputs to 10 C-planes in layer  $u_{C4}$ , each consisting of a single cell representing the 10 numerals to be recognized. How the 16  $u_{s4}$  planes are combined for input to the 10  $u_{C4}$  planes is indicated at the right of the cell planes in Figure 3-5. Also, as in layer 3, no thinning of the cells in this layer is performed.

# 3.2.2 Testing the Neocognitron

In testing the pattern recognition capability of the neocognitron network, the following criteria was used. If the cell plane corresponding to the input character yields the largest output of the 10  $u_{C4}$  planes, the response is judged to be correct. If no cell plane responds or this value is identical to that of a different plane, the character is classified as unknown. This will prevent the network from making incorrect guesses when it is uncertain. Finally, a wrong classification is used when the appropriate cell plane exhibit a weaker response than a cell in another plane.

Figure 3-6 : Sample patterns that were correctly classified by the neocognitron.

Training the neocognitron as described in the previous section took approximately 4 minutes 36 seconds on a SUN SPARCStation 20. However, during the recognition phase processing a single character took approximately 4 seconds. The model was tested with numerals of different writing styles, with varying degrees of deformations from the training patterns, and with patterns placed on different positions on the input plane. In addition, testing was also conducted on the complete patterns utilized during training. These patterns are illustrated in Figures 3-4 and 3-5. The neocognitron correctly classified all the patterns in this test set. Other patterns that the neocognitron correctly classified are illustrated in Figure 3-6. Patterns that the neocognitron incorrectly classified or judged unknown are shown in Figure 3-7.

Figure 3-7 : Sample test patterns that the neocognitron failed to correctly classify.

The variety of patterns that can be recognized by the neocognitron is dictated by the numbers of layers and planes in the network, and the variations of the training patterns. Since this implementation has nine levels of C-cells and S-cells, increasing the number of layers is

not necessary. It would suffice to increase the number of planes in layers two and three, and/or the number and variations of the training patterns. These additional training patterns should include partial and complete patterns of the new styles of patterns to be recognized.

# 3.3 Implementation of the Digi-Neocognitron Model

Architecturally, the digi-neocognitron is identical to the neocognitron model described in Section 3.2. However, the learning rates and saturation parameters were changed in order to improve the weights developed and to satisfy the required bit restrictions. Also, to implement the DNC model functions as described in Equations (18), (26), (27) and (33), modifications to the C-routines in section 3.2 were required.

Like the neocognitron, the learning rate varied for all the layers. However, these values were developed during training to ensure that the computed weights adhered to the digi-neocognitron's bit-width restrictions. The final values for the learning rates were  $q_1 = 40$ ,  $q_2 = 135$ ,  $q_3 = 185$  and  $q_4 = 525$ . The procedure utilized to obtain these results is discussed in Section 3.3.1. Also developed through training were the values for the saturation parameter. These values were  $\alpha_1 = \alpha_2 = \alpha_3 = 0.125$  and  $\alpha_4 = 1.0$ .

The digi-neocognitron model functions required power of 2 approximations, the use of look-up tables, and shifters to implement multiplications and divisions. With the exception of the shift operations, all the required changes for converting the neocognitron to a digineocognitron model were made. Shifters could not be used since the calculations are performed on floating point values, and the C-compiler utilized did not allow bit-wise operations on floating point values. The C-routines for the DNC model functions are shown Appendix A-2.

## 3.3.1 Training the Digi-Neocognitron

With the inclusion of the procedure described in Section 3.1, training the digineocognitron is identical to the training described for the neocognitron. Using the procedure described in Section 3.1, the planes in the first layer of S-cell are trained. The neocognitron model is first used and the learning rate is adjusted to ensure that the weights are within the prescribed limits. This is necessary since the approximations used by the DNC model assigns the maximum allowable values if the results are greater than or equal to these limits. In such a situation the excitatory weights will be rounded down even though the inhibitory weights are increasing. As a result the digi-neocognitron would loose its ability for pattern recognition. It is preferable to develop excitatory weights with the neocognitron that are at the minimum value required by the digi-neocognitron for rounding up. When this is achieved, two criteria are used to determine if the weights computed achieves an acceptable pattern recognition capability. First, the excitatory and inhibitory weights are compared with those for the neocognitron and the learning rate is modified; and the simulation is repeated until an acceptable correlation is obtained. Next, the pattern recognition capability of this layer is tested using known good patterns. If the results of this test are unacceptable, the saturation parameter is modified and the networks response is rechecked. If this also fails to yield an acceptable response, the inhibitory input  $b_i(k)$  is adjusted. The process is repeated until the desired response is achieved or some compromise is reached. This procedure is used to train all the layers of the network. Modification of the inhibitory inputs were not required for the first layer in this model. However, it was required for the remaining layers in the network.

# 3.4 Performance Comparison of the Neocognitron and Digi-neocognitron Models

Both the neocognitron and the digi-neocognitron neural network models were tested using patterns from the training set, and patterns of different individual hand-writing styles. These patterns varied in size, shape, the presence of deformations, and their position on the input plane. Patterns that the neocognitron failed to recognized or classified as unknown contained significant deformations from those in the training set, or were extremely similar one of the other ten numerals. For the test set utilized, the neocognitron correctly classified 93% of the patterns, and classified 7% as unknown. In addition, for patterns that were included in the training set the neocognitron correctly classified 100% of these patterns. As expected, the performance of the digi-neocognitron was lower than that of the neocognitron. For patterns that were included in the training set, the digi-neocognitron correctly classified 90% of the patterns, and classified 10% as unknown. For the complete set of test patterns the digi-neocognitron's classifications were 80% correct and 20% unknown. Some of the patterns that were correctly classified by the digi-neocognitron model are illustrated in Figure 3-8.

Figure 3-8 : Sample test patterns that the digi-neocognitron correctly classified.

The digi-neocognitron's performance shortfall is due to the type of training method used, the set of training patterns used, and the need for further refinement of the weight values developed.

Using the supervised training methodology, each plane is trained to recognize a specific feature from each pattern. If the power of 2 approximations are too gross, some of the cell planes will not learn to recognize its assigned feature. These cell planes will either learn to recognize a different feature or will fail to extract any features from the patterns on its input planes. As this failure to recognize an assigned feature propagates to higher stages in the network, the problem worsens and the pattern will be incorrectly classified.

The other problem with this DNC model was the set of patterns utilized during training. The training patterns used to train the last two layers of the digi-neocognitron made

it difficult to train these layers. Because the number of patterns used to train the cell planes in these layers varied, it was difficult to control the inhibitory inputs to the S-cells. For the few planes with more training patterns than the remaining planes in the layer, the inhibit output would reach the maximum upper limit before adequate excitatory weights could be developed for the remaining cell planes.