# Rochester Institute of Technology

# **RIT Digital Institutional Repository**

Presentations and other scholarship

Faculty & Staff Scholarship

7-2-2019

# Integrated Photonics and Application-Specific Design on a Massive Open Online Course Platform

Sajan Saini Massachusetts Institute of Technology

Stefan F. Preble Rochester Institute of Technology

Miloš Popović Boston University

Jaime Cardenas University of Rochester

Alan Kost University of Arizona

See next page for additional authors

Follow this and additional works at: https://repository.rit.edu/other

# **Recommended Citation**

Sajan Saini, Stefan Preble, Miloš Popović, Jaime Cardenas, Alan Kost, Erik Verlage, Gregory Howland, and Lionel C. Kimerling "Integrated photonics and application-specific design on a massive open online course platform", Proc. SPIE 11143, Fifteenth Conference on Education and Training in Optics and Photonics: ETOP 2019, 111430Y (2 July 2019); https://doi.org/10.1117/12.2523878

This Conference Proceeding is brought to you for free and open access by the RIT Libraries. For more information, please contact repository@rit.edu.

# Authors

Sajan Saini, Stefan F. Preble, Miloš Popović, Jaime Cardenas, Alan Kost, Erik Verlage, Gregory A. Howland, and Lionel C. Kimerling

This conference proceeding is available at RIT Digital Institutional Repository: https://repository.rit.edu/other/986

# Integrated Photonics and Application-Specific Design on a Massive Open Online Course Platform

Sajan Saini<sup>\*a</sup>, Stefan Preble<sup>b</sup>, Miloš Popović<sup>c</sup>, Jaime Cardenas<sup>d</sup>, Alan Kost<sup>e</sup>, Erik Verlage<sup>a</sup>, Gregory Howland<sup>b</sup>, Lionel C. Kimerling<sup>a,f</sup>

<sup>a</sup>AIM Photonics Academy, Materials Research Laboratory, Massachusetts Institute of Technology, 77 Massachusetts Ave., Cambridge, MA, USA 02139; <sup>b</sup>Kate Gleason College of Engineering, Rochester Institute of Technology; <sup>c</sup>Dept. of Electrical & Computer Engineering, Boston University;

<sup>d</sup>The Institute of Optics, University of Rochester; <sup>c</sup>College of Optical Sciences, The University of Arizona; <sup>f</sup>Dept. of Materials Science and Engineering, Massachusetts Institute of Technology.

#### ABSTRACT

Silicon-based photonics is mobilizing into a manufacturing industry with specialized integrated circuit design requirements for applications in low power cloud computing, high speed wireless, smart sensing, and augmented imaging. The AIM Photonics Manufacturing USA Institute, which operates the world's most advanced 300mm semiconductor research fab, has co-developed a Process Design Kit (PDK) in fabless circuit design for these expanding digital and analog applications; however, there currently isn't available an in-depth curriculum to train engineers (academia, industry) in the AIM PDK process and Electronic Photonic Design Automation (EPDA) software. AIM Photonics Academy, an education initiative of AIM Photonics based at MIT, has collaborated with faculty to create three online MOOC edX courses that (1) introduce integrated photonics devices, and applications performance needs and metrics; and (2) train into the AIM PDK and specialized EPDA tools in a six week design project to lay out an application-specific photonic transceiver. The courses are structured around asynchronous video lectures and exploratory design problems that involve Python and Matlab-based first-principles calculations (systems modeling) or advanced EPDA tools (circuit design and layout). The online MOOC courses can optionally form a tandem blended learning component with two AIM Photonics Academy on-site training programs: the annual AIM Summer Academy one-week intensive program (held every July at MIT), or a photonic integrated circuit testing workshop (the first workshop is planned for fall 2019). These courses are a cornerstone effort at AIM to found and support a specialized cohort community of future integrated photonics designers.

**Keywords:** integrated photonics, silicon photonics, remote learning, Process Design Kit, Electronic Photonic Design Automation, AIM Photonics Academy, AIM Photonics Institute, edX course, MOOCs, blended learning

# **1. INTRODUCTION**

High index contrast planar waveguide structures were first investigated on the silicon-wafer platform in the 1980s-90s<sup>1,2,3,4,5</sup> as device-sparse die structures, patterned lithographically and measured in arrays of tens of devices. Since then, the processing maturity of silicon and silicon nitride waveguide-based devices has improved to a degree of dense integration that now accommodates hundreds of *integrated* devices<sup>6</sup> within chip dies of typical dimensions 6x8.5 mm<sup>2</sup> (passive/active PIC chips)<sup>7</sup>. At the same time, photonics as an application-specific technology has migrated beyond telecommunications<sup>8,9</sup> to become a necessary component solution for power, speed, sensitivity, and resolution needs in datacom<sup>10,11,12</sup>, wireless<sup>13,14,15</sup>, sensing<sup>16,17</sup>, and imaging<sup>18,19</sup>, respectively.

As a result of this chip processing and application area evolution, a critical need exists today to stand up a new advanced photonics curriculum that instructs the learner in emerging design concepts for photonic integrated circuit (PIC) chips:

- fabless photonic circuit design<sup>20,21</sup> that relies on a Process Design Kit (PDK), an electronic library of standardized components that cleanroom fabricators can manufacture with reliable performance specifications;

- strategic design with PDK component blocks, in addition to custom-designed components, to realize application-specific (AS) optimized PIC chips;

\* <u>sajan@mit.edu; https://aimphotonics.academy/</u>

Fifteenth Conference on Education and Training in Optics and Photonics: ETOP 2019, edited by Anne-Sophie Poulin-Girard, Joseph A. Shaw, Proc. of SPIE Vol. 11143, 111430Y · © 2019 SPIE, ICO, IEEE, OSA · CCC code: 0277-786X/19/\$18 · doi: 10.1117/12.2523878

- a Design for Manufacturing<sup>22,23,24</sup> methodology that addresses an unavoidable degree of process variation within and across mass-manufactured PIC chips; and

- a Design for Test <sup>20,25,26</sup> methodology that determines both circuit layout and packaging needs to assess circuit performance during manufacture or in-field deployment/maintenance.

Aside from these curricula criteria, there are also pedagogy constraints governing this photonics teaching need. In terms of a feasible Technology Readiness Level (TRL), integrated photonics today remains a largely state-of-art solution than can solve application-area needs in principle, but apart from significant advances in commercial datacom, has yet to be thoroughly established in practice for the latter three application areas. In addition to incipient engineers—graduate students in-training at universities—there is an incumbent workforce of veteran industry engineers who need to rapidly retrain, within the time and geographic constraints of their companies, in order to synthesize their application-area expertise with a fundamental-thru-advanced foundation of PIC design principles.

Workforce research by the AIM Photonics Academy project at MIT,<sup>27,28</sup> led by Prof. L.C. Kimerling, has concluded a new education curriculum is needed, characterized by:

- a) modular, short-term learning that confers sufficient in-depth engagement for design mastery;

- b) stackable learning that supplements traditional photonics curricula, and focuses on the post-PDK era of photonics instruction;

- c) self-paced learning that accommodates independent study and reskilling/upskilling for incumbent engineers;

- d) remote learning that sustains perennial upskilling for engineers, and introduces a global academic-industrial audience to a singular pedagogy based on a leading edge TRL level for PICs on a 300mm wafer fab platform.

To uphold these demanding characteristics, AIM Academy has partnered with the edX Massive Open Online Course (MOOC) cloud platform to produce a sequence of three courses that train students in the fundamentals of silicon photonics devices, fabless PIC design, and application-specific PIC design. We present our findings from the second course in this sequence, which introduces students to the PDK design library and software tools that employ it in order to automate circuit design and layout.

#### 2. EDUCATION NEED FOR PIC DESIGN LIBRARY & CLOUD IMPLEMENTATION

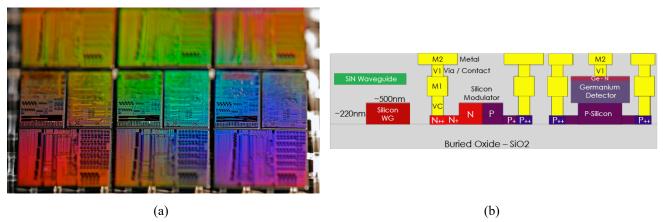

Fig. 1(a) shows a plane-view image of a modern PIC circuit, and a cursory visual inspection indicates the complex degree of circuit design competency required: the areal lithographic design maximally reduces the proximity of waveguide based devices (to pack maximum functionality within a chip), while incorporating manufacturing approaches such as *dummy fill* and *cheesing*<sup>29,30</sup> to facilitate more uniform post-lithography processing (i.e., reactive ion etch rate, over-cladding deposition) across the chip. At the same time, Fig. 1(b) shows the necessity to fabricate multiple hierarchical layers in a PIC circuit, to enable crossover of electrical interconnects and waveguides; avoid shorts between feedback control (e.g. heating) and bias (e.g. modulator contacts) interconnects; and facilitate optical power transfer from materials-diverse waveguides (silicon nitride to silicon) or waveguides-to-detectors. This combination of areal and hierarchical layer complexity, for hundreds of device components in a PIC, makes it prohibitive for a single chip designer to lay out a suitable lithography mask set and process flow sequence to fabricate without the inevitable creep of artifact design errors.

Taking guidance from the IC chip industry's manufacturing practices, a method for chip design automation is needed to systematically and repeatedly direct the layer-by-layer fabrication of a PIC, subject to design rules that govern the build of each device component. This design automation is achieved by pairing an electronic PDK library—that contains experimentally vetted performance specifications for fabricated device components—with software tools that combine the library components to simulate cumulative circuit performance. In addition, the software tools must rely on the PDK to assemble a PIC circuit layout with an instruction set for fabricating the integrated chip structure, in a so-called "tape-out" electronic file format that the cleanroom fabrication technician can access and follow.

The pedagogical goal of a PDK library and such Electronic-Photonic Design Automation (EPDA) software is to cultivate a new class of photonics engineer with master-training in optical circuit design, but not necessarily in photonics device physics or materials processing. This workforce specialization—separating photonics device engineers, circuit

designers, and chip fabricators from each other-enables a division of labor to accelerate PIC innovation in the manufacturing setting.

Figure 1. (a) Plane view of AIM Photonics education teaching PIC chip, highlighting the dense areal complexity of integrated photonics; chip designed by RIT Integrated Photonics Group and fabricated by AIM Photonics Institute. (Photo courtesy Michael Fanto, RIT.) (b) Cross-section schematic view of a canonical PIC chip, highlighting the intensive multi-layer hierarchy of PDK-based PIC chip design. (Courtesy RIT Integrated Photonics Group.)

The content of a PDK includes a collection of theoretical and empirical-adjusted compact models that describe the frequency-dependent impulse response of each photonic device, subject to its varied parameter settings. Fig. 2.(a) shows select device component specifications as-published on the AIM Photonics Institute website. The empirical contribution to compact models incorporates the experimental characterization of fabricated device components, accrued over multiple wafer process runs, and thus represents a statistical evaluation of a fabrication facility's processing fidelity (accuracy) and variation (precision). With this experimental feedback, compact models become phenomenological building blocks to simulate photonics circuits (an integrated combination of device components) of arbitrary complexity. This enables the PDK to become a resource library for circuit design. In addition, the PDK contains the instruction set for fabricating each device component, subject to hierarchy layer rules and areal alignment rules, so that each physical device can be seamlessly concatenated with other PDK device components, to form an integrated circuit layout.

As Fig. 2.(b) indicates, the PDK serves as an intermediary between circuit designer and circuit fabricator. While the designer engages with it via EPDA tools, the fabricator follows the library's process flow instruction set via tape-out, in concert with fab tool Standard Operating Procedures (SOPs). A circuit design pedagogy, based on a PDK and EPDA software, is thus a digital instruction format conducive to on-site intensive program training, or extended remote/online instruction—such as in a multi-week edX course.

The PDK is a comprehensive benchmark for a fabrication facility's processing competencies, and hence foundry-specific PDKs are proprietary electronic resources whose user access is typically governed by confidential Non-Disclosure Agreements (NDAs). The AIM Photonics Institute, a Manufacturing USA fabrication institute located in the United States, is charged by its federal mandate to support the photonics innovation of small-to-medium-scale enterprise businesses by provisioning a 300mm silicon wafer processing line via Multi-Project Wafer runs (MPWs). Access to the AIM PDK and its MPW runs is open to a global community, excepting restricted nations and nationals per US export control regulations. Pursuant to an attendant commitment to enhance PIC circuit designer education and stimulate workforce growth, AIM has repurposed a dated and redacted PDK version release into an Education PDK (EdPDK) for instructional use in a MOOC platform.

Global student access within a Massive Open Online Course (MOOC) on edX—whose education mission is delineated by low-cost and accessible remote learning (to US export-approved nations and nationals)—is partly at odds with the proprietary confidentiality of the EdPDK. To resolve this cross-purposes constraint, AIM has established a secure online cloud portal, the AIM Photonics Virtual Design Center,<sup>31</sup> within which registrants can remotely access the EdPDK and EPDA software, subject to terms of use, and not download either the library or software tool to their local computer.

| Passive Components          | Qty | Selected Performance         |                                              |         |                                         |              |  |

|-----------------------------|-----|------------------------------|----------------------------------------------|---------|-----------------------------------------|--------------|--|

| Waveguides                  | 6   | <1dB/cm                      |                                              |         |                                         |              |  |

| Edge Couplers               | 5   | <1.5dB/facet                 |                                              |         |                                         |              |  |

| Vertical Couplers           | 2   | <3dB/coupler                 | Treat_coupler_si                             |         |                                         |              |  |

| 3dB 4-Port Splitters        | 2   | <0.5dBloss                   | Iz I                                         |         |                                         |              |  |

| 3dB Y-junctions             | 3   | <0.2dBloss                   | spiller_Sport_si<br>=-lat                    |         | System Level Design                     |              |  |

| Power Taps (1% & 10%)       | 3   | <0.1dBloss                   | - II - IIS                                   |         | PIC / ASIC / SOC                        |              |  |

| Layer Transitions           | 5   | <0.1dBloss                   | Anode<br>photodetector                       |         |                                         | 10,300       |  |

| Crossing                    | 1   | <0.15dB loss, <-50dB Xtalk   |                                              |         |                                         |              |  |

| Polarization Rotator        | 1   | <0.8dBloss                   | Cathode                                      |         | Schematic                               | RTL/IP       |  |

| Polarization Splitter &     | 1   | <0.8dB PDL, >20dB PER        |                                              | N       |                                         |              |  |

| Rotator                     |     | <0.80B PDL, >200B PER        |                                              |         | Entry and                               | Partitioning |  |

| Waveguide Termination       | 1   | <-50dB reflection            | Heater2+ -= h2 n 6<br>                       |         | Design                                  | and Design   |  |

| Active Devices              | Qty | Selected Performance         |                                              |         |                                         |              |  |

| C Band Photodetector        | 1   | BW>45GHz, R~1A/W             | -3 - Crop odd                                | PDK     |                                         |              |  |

| C+L Band Photodetector      | 1   | BW>35GHz, R~1.1A/W           |                                              | Library |                                         |              |  |

| O Band Photodetector        | 1   | BW>40GHz, R~0.9A/W           | Heater - = = = = = = = = = = = = = = = = = = |         | Physical Design / Layout                |              |  |

| C+L Band MZM 25G            | 1   | 50Gbps PAM4, 0.9Vcm          | di edge cospier_si                           |         | Design Simulation,<br>Verification, DRC |              |  |

| C+L Band MZM 50G            | 1   | 100Gbps PAM4, 1.2Vcm         | d B                                          |         |                                         |              |  |

| O Band MZM                  | 1   | 50Gbps PAM4, 1.3Vcm          | splitter_doort_si                            |         |                                         |              |  |

| Microring Bandpass Filters  | 4   | 0.5nm FWHM, ~26nm FSR        | •- <u>1</u> •-•                              |         |                                         |              |  |

| Microdisk Bandpass          | 4   | <3ns switch, >30dB           |                                              |         |                                         |              |  |

| Switches                    | 1   | isolation                    |                                              |         | ↓                                       |              |  |

| Microdisk Modulators        | 5   | 50Gbps, 1Vpp >4dB ER         | Hoaler = h2                                  |         |                                         |              |  |

| Analog Photodetector        | 1   | SFDR>113dB/Hz <sup>2/3</sup> | •                                            |         | Fabrication                             |              |  |

| Analog MZM                  | 1   | SFDR>100dB/Hz <sup>2/3</sup> |                                              |         |                                         |              |  |

| Thermo-Optic Phase          | 2   | <25mW/π                      | & more                                       |         |                                         |              |  |

| Shifter                     | 2   | <25mvv/m                     |                                              |         |                                         |              |  |

| Thermo-Optic Switch         | 2   | <25mW/switch                 |                                              |         |                                         |              |  |

| Variable Optical Attenuator | 1   | up to 10dB                   |                                              |         |                                         |              |  |

|                             |     |                              |                                              |         |                                         |              |  |

|                             | (a) |                              |                                              |         | (b)                                     |              |  |

|                             |     |                              |                                              |         | × /                                     |              |  |

Figure 2. (a) Published performance specifications for AIM Photonics Institute's APSUNY PDK v.3.0.<sup>32</sup> (b) Schematic of fabless photonics PIC design process flow. (Courtesy RIT Integrated Photonics Group.)

#### 3. EDUCATION NEED FOR DESIGN AUTOMATION & CLOUD IMPLEMENTATION

As noted in the previous section, while the PDK serves as the intermediary resource library to afford specialization of design and fabricator vocations in integrated photonics, EPDA software is the indispensable design tool for reading the PDK to automatically and consistently simulate circuits from its compact models, and lay out device components for fabrication. In addition to circuit simulation and layout, EPDA automation tools enable designers to rapidly model novel device components (not included in contemporary PDKs) and generate theoretical compact models to simulate their performance in a circuit; finally, EPDA tools provide Design Review Checking (DRC) of a PIC circuit's layout, to ensure architecture errors don't degrade the circuit's intended performance. A variety of tool vendors offer these capabilities, and for the edX course developed by AIM Photonic Academy, a partnership has been developed with the software providers Synopsys, Lumerical, and Mentor; in addition, the freeware layout tool K-Layout has been implemented.

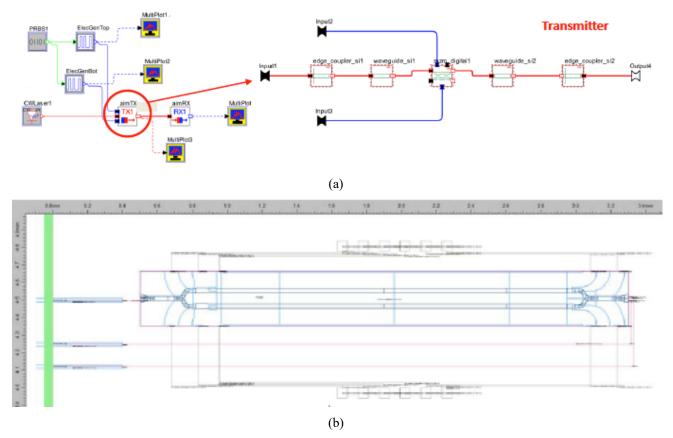

Fig. 3 shows a screen capture from a circuit simulator and a circuit layout tool (courtesy of Synopsys). In order to provide students of the MOOC edX course sufficient time to train and practice with these tools to attain a formative mastery, one or more weeks of instruction and assignment challenges are requisite to teach adequately about (i) device component modeling, (ii) circuit simulation, (iii) circuit layout, and (iv) DRC check.

The access limitations for the EdPDK necessitate installing the library and EPDA tools for (i)-(iv) on the Design Center cloud platform. This enables students to remotely operate these software tools with no installation overhead; the complexity of select software tools commonly result in installation artifact errors, and the migration of all tools to the cloud precludes such problematic start-up delays during the intensive schedule of the edX course.

In addition, it is becoming increasingly apparent that the initial acquisition of or yearly licenses for these EPDA tools is cost-prohibitive for smaller college programs and SME businesses. In the long term, the Design Center cloud platform

may serve a comparable provisioning role for helping smaller academic/industrial entities to design PICs, akin to the MPW run service provided by the AIM Photonics Institute.

Figure 3. (a) An EPDA circuit simulator (courtesy Synopsys *OptSim* software tool); and (b) a circuit layout for a transceiver link within the circuit (courtesy Synopsys *OptoDesigner* software tool).

# 4. EDX COURSES OVERVIEW

Integrated photonics is a neophyte manufacturing technology at present, with a contingent set of processing standards and a partial range of best practice methodologies. The technology is largely informed by its photonics telecom roots, and near-term datacom demands for modern cloud computing data centers. In addition to datacom, there are emergent photonics solutions for high-speed RF wireless, smart sensing, and augmented imaging, developed to varying degrees technological readiness for industry adoption.

As a result, the hierarchical specialization of workforce skills for integrated photonics remains fragmentary, and it is advantageous for present-day integrated photonics designers to cultivate to some degree, threefold knowledge in circuit design and layout, device physics and modeling, and thin film materials processing. At the same time, an application-comparative instruction in circuit design may prompt AS-PIC innovation in the three lagging application areas.

To address these pedagogy needs, AIM Photonics Academy is producing a sequence of three MOOC edX courses in an asynchronous (accessible any time of year) or synchronous (accessible at select times of the year) learning format:

- Fundamentals of Integrated Photonics FIP (device physics, modeling, materials processing; 6-week asynch);

- Photonic Integrated Circuits 1 PIC1 (device modeling, circuit design, layout, DRC check; 6-week synch);

- Photonic Integrated Circuits 2 PIC1 (device modeling, application-specific circuit design; 6-week synch).

The courses are produced with the Massachusetts Institute of Technology's (MIT) edX production house, in collaboration with instructors from MIT, Rochester Institute of Technology (RIT), Boston University (BU), University

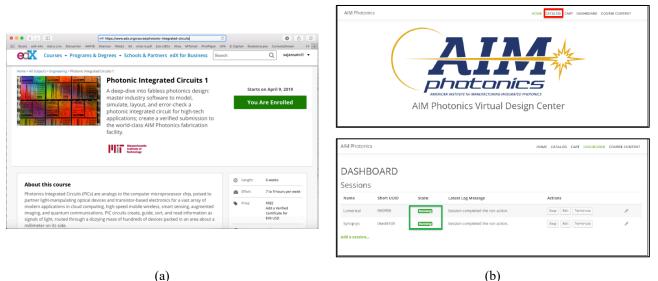

of Rochester (UR), and The University of Arizona (UA). While FIP will offer a foundational background in silicon photonics devices and planar processing technologies to fabricate them, PIC1 will provide an introduction to the PDK design methodology and working with industry-leading EPDA tools for design practices (i)-(iv). PIC2 will elaborate on this circuit-level design instruction with a comparative analysis of application-specific design similarities or differences for datacom, wireless, sensing, and imaging AS-PICs. Presently, PIC1 completed course production and its first offering was given in April 2019<sup>33</sup> (see Fig. 4(a)). FIP and PIC2 are scheduled for release in fall of 2019.

PIC1 is structured in an apprentice-learning format: the course begins with students investigating a malfunctioning "buggy" datacom transceiver (TxRx) AS-PIC. Instruction in weeks 1-2 review core device and circuit simulation concepts, as students assess and identify the buggy TxRx's faulty design errors. With week 3, the course transitions to students developing their own novel TxRx PIC circuit design, and this weekly effort culminates in a final design project submission and analysis report submitted at the end of week 6. The course's weekly workload includes a minimum of one hour of video lecture instruction, a weekly live webinar, and 10-12 hours of assignments/design project homework.

The edX course delivery format is primarily comprised of 1-1.5 hour of weekly video lectures, packaged as a series of short videos running 5-12 minutes in duration. The videos are paired with multiple choice and blank entry questions; select questions also pair with three interactive simulations of photonics devices, developed in the Unity software game programming language. Finally, several Jupyter software Notebooks, which resemble Wikipedia pages with embedded interactive Python and Matlab programming code to explore device design, are linked to online questions about modulators and optical link Bit Error Rate analysis. This part of the course is open to all US export-control cleared nationals. In addition, registrants who enroll for a paid edX certificate receive access to the AIM Photonics Virtual Design Center cloud platform (see Fig. 4(b)). These "verified" or credit seeking students work on the design project using the AIM EdPDK and EPDA tools installed in the cloud platform; the unverified or non-credit seeking registrants are defined as auditors, and have no recourse to work on the design project.

(a)

Figure 4. (a) edX registration page for MOOC course Photonic Integrated Circuits 1.33 (b) AIM Photonics Virtual Design Center,<sup>31</sup> the cloud platform supported by AIM Photonics Institute, on which the AIM EdPDK and EPDA tools are securely stored and only accessible via user remote login.

Upon completion of the inaugural offering of PIC1, a competition will be held to identify the twenty-five best verified student TxRx circuit designs, and these designs will avail of a unique opportunity to be aggregated into an MPW run this summer and be fabricated into PIC chips. A subsequent chip-testing bootcamp, tentatively planned for fall of 2019, will be held at RIT, in which the lead PIC1 lecturer (Prof. Stefan Preble, Kate Gleason College of Engineering) will instruct on chip packaging and testing practices, and guide students in experimental testing of a foundational education PIC chip produced by AIM Photonics, in addition to the fabricated PICs from the competition-winning student designs in PIC1. Students from PIC1 who elect to attend this hands-on on-site training at RIT, will avail of a complete blended-learning curriculum in which they accrue firsthand data on the manufacturing accuracy and precision of the fabbed PICs. Finally, students attending the bootcamp will explicitly learn the necessity of design centering<sup>24</sup> as a methodology to mitigate the

effects of process variation. This statistical data in process control will subsequently be provided to the AIM EdPDK, to update its empirical assembly of device and link compact models.

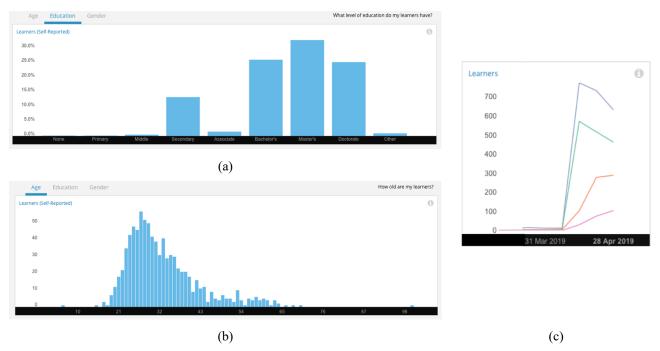

### 5. PHOTONICS INTEGRATED CIRCUITS 1 ONLINE ASSESSMENT

The inaugural offering of PIC1 includes 1,348 auditors and 338 verified certificate-earning registrants. Halfway into the course, auditors have grown in number by 30% and verified students have decreased by only 1.5%. This uncharacteristically low attrition in certificate-earning students (and negative attrition—growth—in auditor audience) indicates an atypical audience for a professional development course. This may be explained in part by Fig. 5(a), which reveals the majority of registrants already have a background MSc degree, with a comparable second tier of BSc and PhD. This large number of post-graduate registrants are an undetermined admixture of academic and industry learners. That said, Fig. 5(b) implies this admixture is preferentially weighted towards industry learners: the registrants' age demographic data may be roughly approximated as an overlap of three normal distributions, with the mean value of the first two distributions around 27 and 35 years of age. These distributions suggest a cohort of recently MSc matriculated industry engineers, and an older cohort of PhD matriculated industry engineers. Lastly, the gender distribution of attendees are 10% women and 90% men, and these numbers correlate with AIM Academy's registration data during its annual training program held at MIT, which is primarily attended by industry members.

Figure 5. User analytics data for registered learners (verified students and auditors) from the first offering of PIC1 on edX. (a) Education background of learners. (b) Age distribution of learners. (c) Learners' engagement measure during first three weeks (blue: total user activity; green: lecture video views; orange: homework activity; pink: discussion forum activity). (Courtesy *edX Insights* analytics tool.)

Fig. 5(c) shows total user engagement in the course during the first three weeks. The blue and green trend lines represent total user activity on the edX course page and views of lecture videos, respectively. In contrast, the orange and pink trend lines represent user activity with the online homework and discussion forum, respectively; these two measures largely qualify verified students who are completing the homework to earn the certificate of completion, and whose discussion comments are largely about working with the cloud EPDA tools (verified student cohort). These trends suggest the decrease in total user activity during weeks 2 and 3 of the course (a drop of 18% from peak active engagement in week 1), is likely indicative of a primarily auditor audience falling behind with the course's extensive weekly workload, or an attrition of comprehension due to lack of EPDA tool and EdPDK access. The verified cohort,

who have largely kept up with homework exercises, have increased engagement as the number of exercises increase in weeks 2 and 3.

Table 1 shows select registration data for the course, from citizens belonging to eighty-five nations from around the world, with the top audiences hailing from the US, India, and Canada. A few education research questions may be drawn from this data. In light of alternative foundry options, it will be instructive to measure the correlation between registration numbers from Europe, Singapore, and South Korea with these semiconductor industrial nations' current annual submissions to AIM Photonics Institute MPW runs. Nations where English is an in-practice language are generally registering actively; to better assess the relatively low participation of the United Kingdom, Ireland (<1%), and Israel (<1%), registration from these nations should be normalized to their percentage workforce in semiconductor industries. Transcribing video lecture subtiling into Japanese, French, Russian, Mandarin, Italian, Portuguese, Turkish, and Spanish may increase engagement from select nations; a control study here may assess if a relative participatory boost from Brazil and Mexico occurs. Education research with Indian and Brazilian students may reveal additional routes to promote yet higher registration. Finally, the low engagement from proximate Canadian academia and industry may only allude to a small engineering workforce population; this should be investigated further.

Table 1. Select registration data from the first offering of the online course *Photonic Integrated Circuits 1* (April, 2019). Course registrants include certificate earning "verified" students, and auditors.

|                       | United<br>States | India | Canada | Brazil<br>United<br>Kingdom | Germany | Pakistan,<br>South<br>Korea | Egypt,<br>France,<br>Russia,<br>Singapore | Italy,<br>Portugal | Japan |

|-----------------------|------------------|-------|--------|-----------------------------|---------|-----------------------------|-------------------------------------------|--------------------|-------|

| Course<br>Registrants | 33%              | 7%    | 5.7%   | 2.7%                        | 2.5%    | 1.7-1.6%                    | 1.5%                                      | 1.3%               | 1.1%  |

#### 6. CONCLUSIONS

Table 2 summarizes AIM Photonics Academy educational offerings to train an incipient-thru-incumbent integrated photonics workforce at the engineer or technician level. In addition to the on-site AIM Summer Academy training program, online MOOC edX education is a flagship effort to stimulate workforce development in two learning modes.

- Reskilling: providing practice-based education to post-graduate academic and industry learners in PDK instruction and EPDA training.

- Upskilling: provide repeat practice-based learning (revisiting on-site training programs, consulting the archived version of a completed edX course, or retaking the next offering of the course), as post-graduate academic and industry learners iteratively determine how to leverage a PDK and EPDA tools for AS-PIC design.

A combination of AIM Academy edX courses with the on-site PIC design training program (which features week-long application-specific design project breakouts), and a soon-to-release onsite PIC-testing bootcamp, offer alternate *blended learning* modes for upskilling as well.

Historically, the transformative communications impact of the fiber optics industry, compounded with the computational demands of the IC microelectronics industry, jointly prompted the research thrust to develop high index contrast siliconbased planar photonics, and these studies have subsequently cohered into a mature integrated photonics research technology that now leverages the standardized design methodology of a PDK. However, the technology has still to proliferate at a manufacturing readiness level in diverse area applications. The education challenge today for integrated photonics, is to begin training a specialized workforce in PIC design, PIC fabrication, and PIC packaging & testing, while these topical specializations are still being ratified by industry needs.

PIC fabrication curriculum largely emulates IC fab training, and thus PIC design represents the priority pedagogy to authoritatively articulate; PIC packaging & testing is an attendant specialization topic that will more optimally develop in response to a vetted PIC design curriculum. Because PIC design is still an emergent specialization with developing standards and methodologies, the audience for this curriculum—typically post-graduate engineers—need to be trained not only in their specialized discipline of PIC simulation and layout, but also need to attain a minor degree of *lateral* competency in the adjacent specialization topics of device physics (the purview of common current photonics curricula)

and materials processing (i.e., PIC fabrication learning goals). This lateral competency will invaluably prepare PIC designers to better assess unexpected performance in fabricated PIC chips due to process variation, and troubleshoot *a priori* or *a posteriori* solutions that rely on Design for Test and Design for Manufacturing concepts such as design centering—the design of lower-performance circuit components, that are more robust to the influence of process variation.

|                                                         | Topical Specialization                                                                                                                                                                                                                              | Mastery Level                                                                                                                 | Time Commitment                                                                                                                                                                                                                                                 | Location |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| AIM Summer<br>Academy<br>(MIT, July)                    | <ul> <li>Track 1: device physics;<br/>material proc/fab; intro to PIC<br/>design; intro to PIC packaging,<br/>test; intro to application-<br/>specific design</li> <li>Track 2: PIC circuit design with<br/>DDV_EDDA to ab interfect pIC</li> </ul> | moderate-high                                                                                                                 | <ul><li>intermediate (1 week)</li><li>intermediate (1 week)</li></ul>                                                                                                                                                                                           | on-site  |

|                                                         | PDK, EDPA tools); intro to PIC<br>packaging, test; intro to<br>application-specific design                                                                                                                                                          | • moderate-high                                                                                                               |                                                                                                                                                                                                                                                                 |          |

| edX Course<br>Modules                                   | <ul> <li>FIP (device physics, materials proc/fab)</li> <li>PIC1 (PIC circuit design with PDK, EPDA tools)</li> <li>PIC2 (application-specific PIC design)</li> </ul>                                                                                | <ul><li> high</li><li> high</li><li> high</li></ul>                                                                           | <ul><li>long (6 weeks)</li><li>long (6 weeks)</li><li>long (6 weeks)</li></ul>                                                                                                                                                                                  | online   |

| Education Packs                                         | <ul> <li>device physics</li> <li>materials proc/fab</li> <li>AS-PIC: sensing</li> <li>PIC packaging</li> <li>PIC test</li> </ul>                                                                                                                    | <ul> <li>moderate-high</li> <li>moderate-high</li> <li>moderate-high</li> <li>moderate-high</li> <li>moderate-high</li> </ul> | <ul> <li>short (single-sitting / class lectures)</li> </ul> | online   |

| Virtual<br>Manufacturing<br>Lab learning<br>simulations | <ul><li> device physics</li><li> materials/proc/fab</li><li> PIC testing</li></ul>                                                                                                                                                                  | <ul><li>moderate</li><li>moderate</li><li>moderate</li></ul>                                                                  | <ul> <li>short (single-sitting)</li> <li>short (single-sitting)</li> <li>short (single-sitting)</li> </ul>                                                                                                                                                      | online   |

| TED-Ed<br>Animated Video<br>explainers                  | <ul> <li>photonics principle</li> <li>application-specific needs for<br/>integrated photonics</li> </ul>                                                                                                                                            | <ul><li>moderate</li><li>low</li></ul>                                                                                        | <ul><li> short (single-sitting)</li><li> short (single-sitting)</li></ul>                                                                                                                                                                                       | online   |

| Photonics<br>Bootcamp (PIC<br>packaging, test)          | <ul><li>MIT bootcamp (packaging, test)</li><li>RIT bootcamp (test)</li></ul>                                                                                                                                                                        | <ul><li>high</li><li>high</li></ul>                                                                                           | <ul><li>intermediate (1 week)</li><li>intermediate (1 week)</li></ul>                                                                                                                                                                                           | on-site  |

Table 2. A summary of AIM Photonics Academy's on-site and online education offerings.

Textbooks and software with education licenses in a university workshop setting have been the traditional format for delivering advanced technical design instruction. However, the MOOC format of edX liberates this costly approach with modestly priced online courses that may serve as a perennial refresher to upskill not only university students, but veteran industry engineers. AIM Photonics Academy workforce research suggests such a perennial low-cost access format—that allows the trained learner to repeat-practice without missing work time—will prove to be an enabling practice mode of learning that complements the historic role of the trusted theory textbook accessible at arm's length, on a technology practitioner's bookshelf.

Textbooks remain an instrumental learning mode to cultivate deeper design mastery, as attested by the compilation of master texts in IC microelectronics chip design. It remains to be seen what division of learning goals the next authoritative PIC design textbook will co-plot, alongside a practice-driven edX course on PDK instruction and EPDA tool use.

The collective conclusions drawn from this data are that verified student engagement is high and led by an older, postgraduate audience that is weighted towards an industrial background. Furthermore, auditor retention and growth seem driven by increasing curiosity as word of the course quality is spreading; however, auditor engagement tends to lag due to either the demanding course content, or attrition of comprehension without access to EPDA tools and the EdPDK.

This material is based on research conducted under AIM Photonics and sponsored by Air Force Research Laboratory via agreement number FA8650-15-2-5220. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon.

The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of Air Force Research Laboratory or the U.S. Government.

We also acknowledge partial support of this project by the Open Learning office at MIT (MITx Grant Program).

#### REFERENCES

[1] Goodman, J.W., Leonberger, F.J., Kung, S.-Y. and Athale, R.A., "Optical interconnections for VLSI systems," Proc. IEEE 72(7), 850-866 (1984).

[2] Soref, R. and Larenzo, J., "All-silicon active and passive guided-wave components for  $\lambda = 1.3$  and 1.6 µm," IEEE J. Quant. Electr. 22(6), 873-879 (1986).

[3] Weiss, B.L. and Reed, G.T., "The transmission properties of optical waveguides in SIMOX structures," Opt. and Quant. Electr. 23, 1061-1065 (1991).

[4] Foresi, J.S., Villeneuve, P.R., Ferrera, J., Thoen, E.R., Steinmeyer, G., Fan, S., Joannopoulos, J.D., Kimerling, L.C., Smith, H.I. and Ippen, E.P., "Photonic-bandgap microcavities in optical waveguides," Nature 390, 143-145 (1997).

[5] Miller, D.A.B., "Rationale and challenges for optical interconnects to electronic chips," Proc. IEEE 88(6), 728-749 (2000).

[6] Sun, C., Wade, M.T., Lee, Y., Orcutt, J.S., Alloatti, L., Georgas, M.S., Waterman, A.S., Shainline, J.M., Avizienis, R.R., Lin, S., Moss, B.R., Kumar, R., Pavanello, F., Atabaki, A.H., Cook, H.M., Ou, A.J., Leu, J.C., Chen, Y.-H.,

Asanović, K., Ram, R.J., Popović, M.A. and Stojanović, V.M., "Single-chip microprocessor that communicates directly using light," Nature 528, 534–538 (2015).

[7] "AIM Photonics Multi Project Wafers (MPW)," AIM Photonics, <u>http://www.aimphotonics.com/mpw</u> (30 April 2019).

[8] Soref, R., "The Past, Present, and Future of Silicon Photonics," IEEE J. Sel. Topics Quant. Electr. 12(6), 1678-1687 (2006).

[9] Reed, G.T., "The optical age of silicon," Nature 427, 595-596 (2004).

[10] Vlasov, Y., Green, W.M.J. and Xia, F., "High-throughput silicon nanophotonic wavelength-insensitive switch for on-chip optical networks," Nature Phot. 2 (4), 242-246 (2008).

[11] Liu, A., Liao, L., Rubin, D., Nguyen, H., Ciftcioglu, B., Chetrit, Y., Izhaky, N. and Paniccia, M., "High-speed optical modulation based on carrier depletion in a silicon waveguide," Opt. Expr. 15 (2), 660-668 (2007).

[12] Kirchain, R. and Kimerling, L.C., "A roadmap for nanophotonics," Nature Phot. 1(1), 303-305 (2007).

[13] Marpaung, D., Yao. J. and Capmany, J., "Integrated microwave photonics," Nature Phot. 13(1), 80-90 (2019).

[14] Coldren, L.A., "Photonic Integrated Circuits for microwave photonics," Proc. 2010 IEEE Int. Top. Meeting Microwave Phot., 1-4 (2010).

[15] Kimerling, L.C., Ahn, D., Apsel, A.B., Beals, M., Carothers, D., Chen, Y.-K., Conway, T., Gill, D.M., Grove, M., Hong, C.-Y., Lipson, M., Liu, J., Michel, J., Pan, D., Patel, S.S., Pomerene, A.T., Rasras, M., Sparacin, D.K., Tu, K.-Y., White, A.E. and Wong, C.W., "Electronic-photonic integrated circuits on the CMOS platform," Proc. SPIE Silicon Phot., 6125, 612502 (2006).

[16] Subramanian, A.Z., Ryckeboer, E., Dhakal, A., Peyskens, F., Malik, A., Kuyken, B. Zhao, H., Pathak, S., Ruocco, A., De Groote, A., Wuytens, P., Martens, D., Leo, F., Xie, W., Dave, U.D., Muneeb, M., Van Dorpe, P., Van Campenhout, J., Bogaerts, W., Bienstman, P., Le Thomas, N., Van Thourhout, D., Hens, Z., Roelkens, G. and Baets, R., "Silicon and silicon nitride photonic circuits for spectroscopic sensing on-a-chip," Phot. Res. 3(5), B47-B59 (2015).

[17] Lin, H., Luo, Z., Gu, T., Kimerling, L.C., Wada, K., Agarwal, A. and Hu, J., "Mid-infrared integrated photonics on silicon: a perspective," Nanophot. 7(2), 393-420 (2018).

[18] Sun, J., Timurdogan, E., Yaacobi, A., Hosseini, E.S. and Watts, M.R., "Large-scale nanophotonic phased array," Nature 493, 195-199 (2013).

[19] Heck, M.J.R., "Highly integrated optical phased arrays: photonic integrated circuits for optical beam shaping and beam steering," Nanophot. 6(1), 93-107 (2017).

[20] Hochberg, M. and Baehr-Jones, T., "Towards fabless silicon photonics," Nature Phot. 4, 492-494 (2010).

[21] Hochberg, M. and Chrostowski, L., [Silicon Photonics Design: From Devices to Systems], Cambridge University Press, Cambridge, 3-27 (2015).

[22] Hochberg, M., Harris, N.C., Ding, R., Zhang, Y., Novack, A. Xuan, Z. and Baehr-Jones, T., "Silicon Photonics: The Next Fabless Semiconductor Industry," IEEE Solid-State Circ. Mag. 5(1), 48-58 (2013).

[23] Zortman, W.A., Trotter, D.C. and Watts, M.R., "Silicon photonics manufacturing," Opt. Express 18(23), 23598-23607 (2010).

[24] Chen, X., Mohamed, M., Li, Z., Shang, L. and Mickelson, A.R., "Process variation in silicon photonic devices," Appl. Opt. 52(31), 7638-7647 (2013).

[25] Lu, Z., Jhoja, J., Klein, J., Wang, X., Liu, A., Flueckiger, J., Pond, J. and Chrostowski, L., "Performance prediction for silicon photonics integrated circuits with layout-dependent correlated manufacturing variability," Opt. Express 25(9), 9712-9733 (2017).

[26] Bogaerts, W., Fiers, M. and Dumon, P. "Design challenges in silicon photonics," IEEE J. Sel. Top. Quantum Electron. 20, 1-8 (2014).

[27] Kauffman, Y. and Kimerling, L.C., "AIM Photonics Academy 2016 Workforce Needs Assessment (Final Report)," 2016, <u>https://aimphotonics.academy/form/contact?destination=%2Fworkforce%2Fworkforce-needs-assessment</u> (30 April 2019).

[28] Kauffman, Y. and Kimerling, L.C., "AIM Photonics Academy 2017 Regional Workforce Needs Assessment," 2017, <u>https://aimphotonics.academy/form/contact?destination=%2Fworkforce%2Fworkforce-needs-assessment</u> (30 April 2019).

[29] Heins, M., Cone, C., Ferguson, J., Cao, R., Pond, J., Klein, J., Korthorst, T., Bakker, A., Stoffer, R., Fiers, M., Khanna, A., Bogaerts, W., Dumon, P. and Nesmith, K., "Design Flow Automation for Silicon Photonics: Challenges, Collaboration, and Standardization," [Silicon Photonics III Systems and Applications (Topics in Applied Physics)], Springer, Berlin, Heidelberg, 99-156 (2016).

[30] Bœuf, F., Carpentier, J.F., Baudot, C. Le Maitre, P. and Manouvrier, J.-R., "Silicon Photonics Research and Manufacturing Using a 300-mm Wafer Platform," [Silicon Photonics III Systems and Applications (Topics in Applied Physics)], Springer, Berlin, Heidelberg, 277-315 (2016).

[31] "AIM Photonics Virtual Design Center," 2019, https://aimphotonics.services (30 April 2019).

[32] "AIM Photonics Multi Project Wafers (MPW)," 2016, <u>http://www.aimphotonics.com/mpw</u> (30 April 2019).

[33] "edX courses: Photonic Integrated Circuits 1," 19 February 2019, <u>https://www.edx.org/course/photonic-integrated-circuits</u> (30 April 2019).