### **Rochester Institute of Technology**

## **RIT Digital Institutional Repository**

**Theses**

5-2019

## Verification of SHA-256 and MD5 Hash Functions Using UVM

Dinesh Anand Bashkaran dab8730@rit.edu

Follow this and additional works at: https://repository.rit.edu/theses

#### **Recommended Citation**

Bashkaran, Dinesh Anand, "Verification of SHA-256 and MD5 Hash Functions Using UVM" (2019). Thesis. Rochester Institute of Technology. Accessed from

This Master's Project is brought to you for free and open access by the RIT Libraries. For more information, please contact repository@rit.edu.

#### VERIFICATION OF SHA-256 AND MD5 HASH FUNCTIONS USING UVM

#### by Dinesh Anand Bashkaran

#### GRADUATE PAPER

Submitted in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE in Electrical Engineering

| pproved by:                                                                  |        |

|------------------------------------------------------------------------------|--------|

|                                                                              |        |

| Ir. Mark A. Indovina, Lecturer                                               |        |

| raduate Research Advisor, Department of Electrical and Microelectronic Engin | eering |

| r. Sohail A. Dianat, Professor                                               |        |

| epartment Head, Department of Electrical and Microelectronic Engineering     |        |

DEPARTMENT OF ELECTRICAL AND MICROELECTRONIC ENGINEERING

KATE GLEASON COLLEGE OF ENGINEERING

ROCHESTER INSTITUTE OF TECHNOLOGY

ROCHESTER, NEW YORK

MAY 2019

## **Abstract**

Data integrity assurance and data origin authentication are important security aspects in commerce, financial transfer, banking, software, email, data storage, etc. Cryptographic hash functions specified by the National Institute of Standards and Technology (NIST) provides secure algorithms for data security. Hash functions are designed to digest the data and produce a hash message; a hash is a one-way function which is highly secured and difficult to invert. In this paper, two such hash algorithms are verified using the Universal Verification Methodology (UVM). UVM is IEEE 1800 standard developed to assist in the verification of digital designs; it reduces the hurdle in verifying complex and sophisticated designs.

## **Declaration**

I hereby declare that except where specific reference is made to the work of others, the contents of this paper are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other University. This paper is the result of my own work and includes nothing which is the outcome of work done in collaboration, except where specifically indicated in the text.

Dinesh Anand Bashkaran

May 2019

# Acknowledgements

I would like to thank my advisor, professor, and mentor, Mark A. Indovina, for all of his guidance and feedback throughout the entirety of this project. He is the reason for my love of digital hardware design and drove me to pursue it as a career path. He has been a tremendous help and a true friend during my graduate career at RIT.

# **Contents**

| A۱ | bstrac             | et                |                             |  | ii     |    |

|----|--------------------|-------------------|-----------------------------|--|--------|----|

| De | eclara             | tion              |                             |  | iii    |    |

| A  | Acknowledgements   |                   |                             |  | Acknow | iv |

| Co | onten              | ts                |                             |  | v      |    |

| Li | st of l            | Figures           |                             |  | viii   |    |

| Li | st of '            | <b>Fables</b>     |                             |  | ix     |    |

| 1  | <b>Intr</b><br>1.1 | oductio<br>Resear | on<br>arch Goals            |  | 1 2    |    |

| 2  | Bibl               | iograpł           | hical Research              |  | 3      |    |

| 3  | Ove                | rview o           | of Hash Functions           |  | 9      |    |

|    | 3.1                | Hash I            | Functions                   |  | . 9    |    |

|    |                    | 3.1.1             | Preimage resistance         |  | . 9    |    |

|    |                    | 3.1.2             | Second preimage resistance  |  | . 10   |    |

|    |                    | 3.1.3             | Collision resistance        |  | . 12   |    |

|    | 3.2                | Constr            | ruction of Hash Functions   |  | . 12   |    |

|    |                    | 3.2.1             | MD5                         |  |        |    |

|    |                    | 3.2.2             | SHA-256                     |  |        |    |

|    | 3.3                | APPL              | JICATIONS OF HASH FUNCTIONS |  |        |    |

|    |                    | 3.3.1             | Data Integrity              |  |        |    |

|    |                    | 3.3.2             | Secured Digital Signature   |  |        |    |

|    |                    | 3.3.3             | Authentication              |  | . 14   |    |

| 4  | Ove                | rview o           | of UVM                      |  | 15     |    |

|    | 11                 | Evolut            | tion of LIVM                |  | 15     |    |

Contents vi

| 7 | Con                          | clusion  Future work                   | 44       |  |  |  |  |  |  |  |  |

|---|------------------------------|----------------------------------------|----------|--|--|--|--|--|--|--|--|

|   | 6.2                          | Simulation Report                      | 35       |  |  |  |  |  |  |  |  |

|   | 6.1                          | Synthesis Report                       | 35       |  |  |  |  |  |  |  |  |

| 6 | Resi                         | ults and Discussion                    | 35       |  |  |  |  |  |  |  |  |

|   |                              | 5.2.2 Verification Flow                | 33       |  |  |  |  |  |  |  |  |

|   |                              | 5.2.1 UVM Environment for Block-Level: | 30       |  |  |  |  |  |  |  |  |

|   | 5.2                          | UVM Block Level Design                 | 30       |  |  |  |  |  |  |  |  |

|   |                              | 5.1.2 Design Flow                      | 29       |  |  |  |  |  |  |  |  |

|   |                              | 5.1.1 UVM Environment for IP-Level     | 26       |  |  |  |  |  |  |  |  |

| 3 | 5.1                          | UVM IP-Level Design                    | 25<br>25 |  |  |  |  |  |  |  |  |

| 5 | Custom UVM Backend Design 25 |                                        |          |  |  |  |  |  |  |  |  |

|   |                              | 4.4.3 Type Override                    | 23       |  |  |  |  |  |  |  |  |

|   |                              | 4.4.2 UVM_component                    | 23       |  |  |  |  |  |  |  |  |

|   |                              | 4.4.1 UVM_Objects                      | 23       |  |  |  |  |  |  |  |  |

|   | 4.4                          | UVM factory                            | 22       |  |  |  |  |  |  |  |  |

|   |                              | 4.3.3 Clean-up Phase                   | 22       |  |  |  |  |  |  |  |  |

|   |                              | 4.3.2.4 Shutdown                       | 22       |  |  |  |  |  |  |  |  |

|   |                              | 4.3.2.2 Configure                      | 22       |  |  |  |  |  |  |  |  |

|   |                              | 4.3.2.1 Reset                          | 20<br>22 |  |  |  |  |  |  |  |  |

|   |                              | 4.3.2 Run Phase                        | 20       |  |  |  |  |  |  |  |  |

|   |                              | 4.3.1 Build Phase                      | 20       |  |  |  |  |  |  |  |  |

|   | 4.3                          | Phases of UVM                          | 20       |  |  |  |  |  |  |  |  |

|   |                              | 4.2.8 Postponed Region                 | 19       |  |  |  |  |  |  |  |  |

|   |                              | 4.2.7 Reactive Region                  | 19       |  |  |  |  |  |  |  |  |

|   |                              | 4.2.6 Observed Region                  | 19       |  |  |  |  |  |  |  |  |

|   |                              | 4.2.5 Non-Blocking Assignment Region   | 18       |  |  |  |  |  |  |  |  |

|   |                              | 4.2.4 Inactive Region                  | 18       |  |  |  |  |  |  |  |  |

|   |                              | 4.2.3 Active Region                    | 18       |  |  |  |  |  |  |  |  |

|   |                              | 4.2.2 Pre-Active Region                | 18       |  |  |  |  |  |  |  |  |

|   |                              | 4.2.1 Preponed Region                  | 18       |  |  |  |  |  |  |  |  |

Contents

| A | Sour | ce Code for MD5                      | 50  |

|---|------|--------------------------------------|-----|

|   | A.1  | MD5 Interface                        | 50  |

|   | A.2  | MD5 Sequence and Sequencer           | 53  |

|   | A.3  | MD5 Driver                           | 62  |

|   | A.4  | MD5 Monitor                          | 72  |

|   | A.5  | MD5 Agent                            | 77  |

|   | A.6  | MD5 Scoreboard                       | 79  |

|   | A.7  | MD5 Environment                      | 83  |

|   | A.8  | MD5 UVM Package                      | 85  |

|   | A.9  | MD5 Test                             | 86  |

|   | A.10 | MD5 Top                              | 88  |

| В | Sour | ce Code for SHA-256                  | 90  |

|   | B.1  | SHA-256 Interface                    | 90  |

|   | B.2  | SHA-256 Sequence and Sequencer       | 93  |

|   | B.3  | SHA-256 Driver                       | 102 |

|   | B.4  | SHA-256 Monitor                      | 113 |

|   | B.5  | SHA-256 Agent                        | 117 |

|   | B.6  | SHA-256 Scoreboard                   | 119 |

|   | B.7  | SHA-256 Environment                  | 122 |

|   | B.8  | SHA-256 Package                      | 124 |

|   | B.9  | SHA-256 Test                         | 125 |

|   | B.10 | SHA-256 Top                          | 127 |

| C | Sour | ce Code for Combined MD5 and SHA-256 | 129 |

| Ŭ | C.1  | MD5 and SHA-256 Interface            | 129 |

|   | C.2  | MD5 Sequence and Sequencer           | 135 |

|   | C.3  | SHA-256 Sequence and Sequencer       | 144 |

|   | C.4  | MD5 Driver                           | 153 |

|   | C.5  | SHA-256 Driver                       | 164 |

|   | C.6  | MD5 Monitor                          | 175 |

|   | C.7  | SHA-256 Monitor                      | 182 |

|   | C.8  | MD5 and SHA-256 Agent                | 186 |

|   | C.9  | MD5 Scoreboard                       | 190 |

|   |      | SHA-256 Scoreboard                   | 193 |

|   |      | MD5 and SHA-256 Environment          | 196 |

|   |      | MD5 and SHA-256 UVM Package          | 198 |

|   |      | MD5 and SHA-256 Test                 | 200 |

|   |      | MD5 and SHA-256 Top                  | 203 |

# **List of Figures**

| 3.1 | Properties of Hash Function[1]                       | 11 |

|-----|------------------------------------------------------|----|

| 3.2 | Merkle-Damgard model [1]                             | 12 |

| 3.3 | Digital Signature [1]                                | 14 |

| 4.1 | UVM Scheduling [2]                                   | 17 |

| 4.2 | UVM_Phases [2]                                       | 21 |

| 5.1 | IP-Level Design                                      | 26 |

| 5.2 | Block-Level Design                                   | 31 |

| 6.1 | MD5 and SHA-256 Area over Different technology       | 38 |

| 6.2 | MD5 and SHA-256 Gate Count over Different technology | 39 |

| 6.3 | SHA-256 Coverage                                     | 41 |

| 6.4 | MD5 Coverage                                         | 42 |

|     | MD5 and SHA-256 Coverage                             | 43 |

# **List of Tables**

| 6.1 | Synthesis Results                    | 37 |

|-----|--------------------------------------|----|

| 6.2 | Timing, Power Results                | 37 |

| 6.3 | Coverage across different test cases | 40 |

# **Chapter 1**

## Introduction

The motivation behind the development of SystemVerilog was to develop a unified language to fulfill the needs of user to design and verify. It was initially promoted by Accellera system initiative, after several revisions it became an IEEE standard of Hardware Description and Verification Language (HDVL). SystemVerilog supports object-oriented programming (OOP) concepts to provide diverse needs in verification and modeling. Despite providing enormous features, SystemVerilog failed to adopt widespread practice. Numerous cultural and practical challenges questioned the adoption of SystemVerilog, which paved way for new libraries, tool kits and methodology guidance. This led to development of the Universal Verification Methodology (UVM), a library which is comprised of SystemVerilog and OOP concepts. UVM is a class library used to create test environment and is a powerful package including support for transaction-level modeling (TLM), phasing, re-usability etc. UVM provides infrastructure which is reliable, robust and improves the quality of a testbench. In this project, such an environment is used to verify the algorithm of hash functions. Hash functions maps any arbitrary data to fixed size data, the values returned by hash functions are called hashes or digests. They are an important and ubiquitous cryptography building block. The size of hash value depends

1.1 Research Goals

on the algorithm used to produce it. This project uses MD5 and SHA-256 algorithm to build hash functions, where MD5 produces a 128 bit hash (32 characters) and SHA-256 produces a 256 bit hash (64 characters).

### 1.1 Research Goals

To create an environment that can verify the hash functions MD5 and SHA-256. The following tasks are considered for success of project.

- 1. Understand the algorithm of hash functions MD5 and SHA-256.

- 2. Build a testing environment in UVM and develop a connection between the test components and RTL core of hash functions.

- 3. Analyze different test plans to verify the functionality of IP.

- 4. Analyze possible assertion driven methods.

- 5. Analyze the functionality and timing relation of RTL core in comparison with a software model.

- 6. Collect the functionality and coverage test results.

- 7. Perform gate level simulation to verify the correctness on technology dependent netlist.

- 8. Achieve enough functional coverage to eliminate corner case bugs.

# **Chapter 2**

# **Bibliographical Research**

In any design, majority of the time is spent in verifying the design. Verification could be a hurdle in product release and success in market but with the help of modern language and tools, the time spent can be drastically reduced. The motivation behind verification is to check the functionality of design. There are many techniques that can be used to build a testing environment. Without standardized techniques, verification could increase the cost of using intellectual property (IP), electronic design automation (EDA) tools and increases the time spent in verification. To address this issue, the verification language SystemVerilog was introduced by IEEE Standard 1800. SystemVerilog provides powerful, reusable, flexible environment for verification which counters the cost, complexity and time [3]. SystemVerilog integrates Verilog Hardware Description Language (HDL) and OOP concepts and provides features like coverage, assertions, SystemVerilog DPI (Direct Programming Interface), and constrained random stimulus.

SystemVerilog lacked certain features like macros to automate the creation of utility methods, metaprogramming, code patching which emerged the evolution of the UVM library. The myth, "UVM is making amends for inadequacies of SystemVerilog"; was proved fallacious

by [4]. The paper discusses the certain features of UVM can be performed by SystemVerilog in its own right. However, SystemVerilog lacks in macros which is still unanswered. UVM outplays any other verification technique and its application programming interface (API) defines a base class library (BPI) which is used to develop scalable and modular components for functional verification. In fact, UVM has its own drawbacks which will be resolved in next revision[5]. [6] is a book used as reference throughout the project. The author describes the concepts of UVM from scratch and provides various examples where the concepts are implemented. Overall this text provides adequate information about UVM along with a few case studies which is enough to start building your own testbench.

Code coverage is one of the important features in a verification methodology. However, the accuracy of code coverage is often disrupted by excitation of functional blocks. A coverage method considering conditional checks and observations can significantly increase the accuracy of code coverage [7]. The paper also addresses the issue with narrowed technique which can be implemented in this project. Functional coverage is another aspect that extensively gives the percentage of logic functions used. Functional coverage plays a vital when it comes to implementation of complicated SOC with numerous IP in field-programmable gate array (FPGA). One such implementation of Functional coverage in SystemC based on aspect orientated programming is discussed in [8]. To verify the results of DUT, a reference model is required which is usually developed in SystemC. SystemC is unified platform based on C++ developed by Open SystemC Initiative. It is composed of hardware class library and simulation kernel. It can work in parallel in RTL and produce the results to compare in scoreboard section. [9] discusses the usage of SystemC using case study, in fact the implementation can be simply reproduced in this project. [10] is a good reference to understand the re-usability of testbench. The DUT is I2C and AMBA AXI lite, both IP's are verified using the same framework in SystemVerilog. This paper provides ideas to build a single flexible framework that can be used irrespective of DUT with minor changes. This approach would increase the verification process of MD5 and SHA-256.

[1] is a very good reference to understand the algorithms used in hash functions. It is one of the oldest papers published which discuss all the properties, features, benefits and applications of hash functions. This reference is extensively used to understand the hash functions. Implementation of any algorithm is not easy even though the algorithm is understood to its extreme. Paper [11] presents a good approach to implement hash functions in hardware. Stages of hash functions are discussed from which the hash function can be constructed in any language. Mathematical equations are used to describe the stages of hash functions. Overall, the functions performed are OR, AND and XOR but, how it is performed is decided by the hash function in the respective stage. [12] presents the hardware level implementation of SHA-256. The algorithm is implemented in HDL, tested and verified using FPGA. The paper also discusses the benchmark and optimization solutions for the RTL. These results can be considered as benchmark in developing hash functions at RTL level.

Hash functions are low collision resistant, if the two identical hash messages are generated from two distinct input. H(A) = H(B), hash message of A and B are same but A != B, the original message A and B are distinct. Hash function is collision free only if the generated hash message is not identical for two distinct data. Reliability of hash functions against the attacks is totally dependent on collision property of hash function. Paper [13] presents a unique approach to increase the reliability of hash functions. Hash function can be made collision free using this approach which deals with altering the mathematical equation in stages of operations. The paper also provides a benchmark result, the chances of collision is 1/22. These references stands out to be extremely helpful for designers to design hash functions in highly secured manner. Though this project focuses mainly on verifying the hash functions using UVM, research was made to understand the hash functions completely.

"How safe are the hash functions", is unanswered so far in this context. [14] discusses the vulnerability index of hash functions and provides an approach to increase the vulnerability of hash functions against chain attacks. Any given hash function is constructed using several nodes which together forms cycles. If a hash function is truly random then the length of hash cycles is  $2^n/2$ . Depending on the size of n, the vulnerability of hash function increases. Generally, for the value of N greater than 128 hash functions are considered safe from chain attacks. However, there is no evident that commonly used hash function does have that property. To attack a hash function, one must find a node and repeatedly hash from it until a cycle is found. With the equation that decides the vulnerability index of Hash function, couple of methods are proposed to increase the vulnerability of hash functions. The proposed algorithm is used on MD5 and SHA hash functions, it dramatically increased the vulnerability. When hash functions are constructed using such algorithms, there are pretty much safe against chain attacks.

Hash functions can be used on any arbitrary string to produce a fixed hash message. The size of fixed message depends on the algorithm which are usually 128-512 bits. Certain application requires variable hash message which becomes uncertain with fixed algorithm and fixed hash message size. [15], provides an approach for MD5 hash function to produce variable hash message without compromising the stages of algorithm. This provides high integrity algorithm with user defined hash message. The only difference in proposed algorithm is the compression block after padding stage where the hash message is compressed to 'n' bits. This enables MD5 to take up to 512 bits and convert into user defined hash message making it flexible for low end application. There are several hash functions but all of them do the same job. Depending on the application and the security level choosing hash function can be arduous. [16] presents a solution to this by discussing the various hash functions and suitable application for them. Database indexing, symbol tables, network processing algorithms are few real time

applications discussed with dynamic, cryptographic, robust and string hashing techniques. In certain applications where the memory allocation for hash functions can be inadequate, a chain hashing technique comes into play where the hash functions are linked using external memory.

[17] presents partial work of this project, verification of SHA-256 algorithm using UVM. Paper presents the analysis of the SHA-256 algorithm, and a UVM platform is used to validate SHA-256 as IP. In fact the same procedure can be reproduced to test the SHA-256 and MD5. This reference is used over the implementation of project. Note that although a few components of testing environment might change with respect to DUT, the framework remains the same. Saying that, SHA 256 or MD5 does not make a major difference in the UVM framework. [18] is a good reference to understand the re-usability of UVM testing framework. The paper presents the concepts of re-usability using few case studies.[17] can be reproduced to construct a UVM framework for SHA-256 followed by [18] to reuse the framework for MD5 algorithm. These two are the most relevant and significant references used over the implementation of this project.[19] presents a method to implement automated verification. UVM is a complete framework that includes coverage metrics, self-checking testbenches and automatic test generation. Even though the DUT here is not complex but rather simple IP's, complete utilization of UVM is another goal.

While reliability and data integrity is one key feature of hash function, the performance is yet unanswered. Especially when used in high end application where low latency is expected, the algorithm is expected to process rapidly. In[20, 21] both references aim at same goal using different approaches. The goal is to optimize the design by adjusting the longest delay path in netlist to provide high throughput and low latency. To overcome this hurdle, unrolling is a technique which focuses on multiple rounds of the core compression function in combinational logic, which helps in reducing the number of clock cycles required to compute the hash. The paper also discusses about pipelining the architecture for better throughput and low latency.

[22] provides a unique approach to optimize MD5 using data dependency, data forwarding and pipelining. The pipeline is 4 stages and the architecture of MD5 is altered to minimize the effect of data dependency. The architecture is tested on a Xilinx Virtex FPGA, benchmark results 1040 M bps as throughput. This architecture seems to be the best design up to date.

[23] talks about the advantage of implementing MD5 on hardware rather than software. Hardware implementations can be more immune to attacks and cannot be altered like software. A Xilinx Virtex 5 FPGA is used to implement the MD5 hardware. The implementation was performed on two ways, iterative looping and full loop unrolling. The overall throughput is 165 M bps. One such common way to increase the efficiency is to pipeline the stages of operation [2]. The paper discusses the pipelined architecture of MD5 through different stages. The pipelined architecture is implemented in FPGA, with a 64 stage pipelined MD5 architecture the throughput is 725 M bps, which is 6 times more than non-pipelined version. [24–26] are online reference for UVM which is extensively used to understand and implement Test Bench.[27, 28] provides the source code for SHA-256 in Verilog and C. [29, 30] provides the source code for MD5 in Verilog and C.

# **Chapter 3**

## **Overview of Hash Functions**

This chapter discusses the basics concepts, construction and applications of hash functions.

### 3.1 Hash Functions

A hash function takes arbitrary data to produce fixed size hash message, the size of hash message depends on hash algorithm. h = H(M), M is input, and h is hash message generated by H algorithm. The reliability of the hash function depends on the algorithm and length of the message generated. Merkle-Damgard model is commonly used hash algorithm in hash functions. In general hash functions should have following properties,

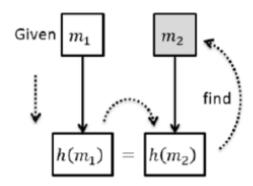

### 3.1.1 Preimage resistance

If hash message h is given, it should be highly impossible to find message M such that h = H(M). Hash functions are one-way property, hash h can be computed from message M but not other way around.

3.1 Hash Functions 10

## 3.1.2 Second preimage resistance

Given message M1, it is highly impossible to find another message M2 such that M1 and M2 generate same hash h. 3.1

3.1 Hash Functions

Figure 2 Preimage resistance

Figure 3 Second-preimage resistance

Figure 3.1: Properties of Hash Function[1]

### 3.1.3 Collision resistance

It should be highly impossible to find two messages S1 and S2 such that S1 = !S2, but h(S1) = h(S2).

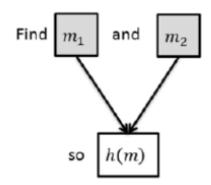

### 3.2 Construction of Hash Functions

Hash functions can be structured in several ways but the Merkle-Damgard model stands out to be popular and reliable. It has been practiced successfully in hash functions like MD5 and SHA-2. In this model, the message is padded and divided into uniform length of blocks. The compression function F processes the blocks in sequential order which generates intermediate hash. The final compression function outputs the hash message. The size of the hash message depends on the user implementation. If the compression function F is collision resistance, so is the generated hash message. SHA-2 and MD5 follow Merkle-Damgard model. They use operations like OR, XOR and AND for the compression functions. Collision-pairs was founded that makes these algorithms vulnerable to collision attacks. Although there was no evidence to support the successful attack against this algorithm. The results from, National Institute of Standards and Technology (NIST) shows SHA-3 seems to be more secured than other versions of SHA-2 algorithm.

Figure 3.2: Merkle-Damgard model [1]

#### 3.2.1 MD5

MD5 is an implementation of Merkle-Damgard. MD5 has 512 bits from M0-M15, sixteen 32-bit word. Internally, the hash state has state variables of four 32-bit word (A1, B1, C1, D1). In the stages of computation, the state variables are changed to new 32-bit value by the compression function F. MD5 has 64 stages of steps grouped in terms of 16 stages. First 16 stages are called Round one, second as Round two and so on. Every Round has unique compression function. The final hash message is the concatenation of state variables A1, B1, C1, D1 in last block of last Round.

#### 3.2.2 SHA-256

SHA-2 can operate on four different modes, SHA-256, SHA-384, SHA-224, and SHA-512. This project uses SHA-256 and discussion is only based on SHA-256. SHA-256 also uses the Merkle-Damgard model and works similar to MD5. The message block size is 512 Bits like MD5, but the state variables are doubled to include 8 state variables. The operations performed on each stage are AND, OR, XOR.

## 3.3 APPLICATIONS OF HASH FUNCTIONS

### 3.3.1 Data Integrity

After receiving data, the hash message can be generated and compared with another hash message, which was generated from original data. Here, the original message should be sent through a secure channel. If both the hash message are equal, then data was not modified during the transmission. This is defined by the second preimage property of hash function.

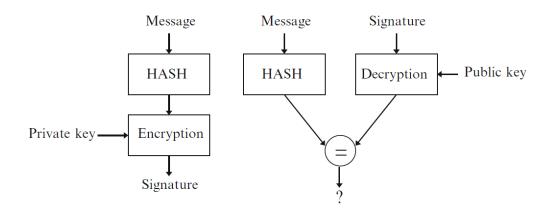

### 3.3.2 Secured Digital Signature

Public-key algorithm combined with Hash functions evolves many applications, one such is Digital Signature. Digital Signature can be generated by combination of Hash message and Encryption from private-key. The Generated Text can be used as signature. The Signature can be verified by decrypting the signature using public-key and comparing it with the hash message.

Figure 3.3: Digital Signature [1]

### 3.3.3 Authentication

The password of the user is hashed and sent to server, where it is compared by the server. Every time the password is hashed, it is concatenated with random values generated by the server. This allows high data-integrity.

## Chapter 4

## **Overview of UVM**

This section dives deep into UVM, and describes about different features, phases, transaction-level modeling (TLM), semantics, test bench components etc.

### 4.1 Evolution of UVM

The initial version of UVM was released on Feb 28, 2011, after which UVM became a standalone verification methodology. Since then UVM has undergone several changes to fix bugs and add features. A few important features of UVM 1.0 were:

- 1. End-of-test objection mechanism to enhance the ease of clean up at end of simulation.

- 2. Call-back mechanism that would alter the existing behavior.

- 3. Report catcher to enhance report handling.

- 4. Heartbeat Mechanism to monitor the life of UVM components.

- 5. Register Level Modeling to enhance the verification of memory unit.

6. TLM interface FIFO, resource database.

Around June 2014, UVM 2.0 was released. Further changes, bugs, features were improved; a few important features are:

- 1. uvm\_sequence\_base::starting\_phase has been replaced by set\_starting\_phase and get\_starting\_phase. This change prevents modification of phase during run time.

- 2. uvm\_sequence\_base::set\_automatic\_phase\_objection were added which avoids the necessity of calling raise\_objection and drop\_objection explicitly.

- 3. New methods like stop\_request, stop\_global\_request, set\_global\_timeout, uvm\_test\_done, do\_kill\_all etc.

Today, SystemVerilog and UVM is the preferred environment to verify from IP, Block, SOC, chip level. Over years of practice, engineers have adapted themselves to the UVM environment. Even though UVM is sophisticated, it is highly flexible to provide the environment for complex verification projects. Even a few Verification IPs (VIPs) were introduced which became handy in creating UVM testbenchs.

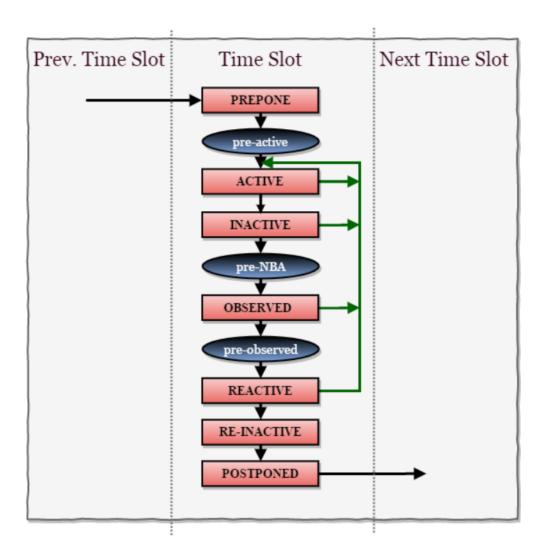

## **4.2 UVM Scheduling Semantics**

A single time slot (One clock period) is divided into multiple regions where several different events are scheduled. UVM time scheduling has been improved from Verilog scheduling semantics. This event scheduling provides clear and predictable interaction with DUT. Verification Engineer should be aware of event scheduling to understand the core of UVM. Following are the different region in event scheduling,

Figure 4.1: UVM Scheduling [2]

### 4.2.1 Preponed Region

The variables used in concurrent assertions are sampled in this region. The preponed region is evaluated only once, and it happens right after advancing simulation time.

### 4.2.2 Pre-Active Region

Pre-Active region is for the PLI (Programming Language Interface) callback mechanism. It allows user code to read and write values just before the active regions are evaluated.

### 4.2.3 Active Region

All the event that needs to be evaluated in corresponding clock period are placed in this region.

The order of execution can be processed in any order.

- 1: Execute blocking assignments, continuous assignments.

- 2: Execute the right-hand side (RHS) of non-blocking assignments and schedule updates in the Non-blocking Assignment Events Region (NBA).

- 3: Execute \$finish and \$display commands.

### 4.2.4 Inactive Region

In this region all the events that needs to be evaluated after active events are placed. #0 blocking assignments are placed in this region.

### 4.2.5 Non-Blocking Assignment Region

The RHS of non-blocking assignments which were evaluated in active region, is updated to left-hand side (LHS) in this region. Since all the non-blocking assignments needs to be inde-

pendent of each other, this region solves the issue.

### 4.2.6 Observed Region

The function of this region is to evaluate the concurrent assertions. The values required for concurrent assertions were sampled in preponed region. The reason for this region is, assertion should be evaluated once in every clock period. Depending on the result of assertion whether pass/fail, the corresponding event is scheduled in reactive region.

### 4.2.7 Reactive Region

This region is allocated for events in program block. The functionality if this region is to execute program block in any order. Since, this region is placed after active and non-active region this can be used to avoid race condition. Another way of avoiding race condition is using clocking block which would induce skew.

- 1. Execute program blocking assignments.

- 2. Execute pass/fail condition that were assigned in concurrent statements.

- 3. Execute program block continuous statements.

- 4. Update the LHS of non-blocking assignments in program block.

### 4.2.8 Postponed Region

\$strobe and \$monitor commands are executed in this region. The final updated value is reflected for the corresponding time slot. This region is also used to collect the functional coverage.

4.3 Phases of UVM

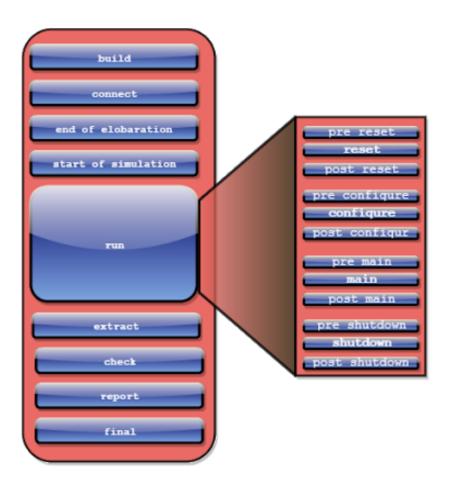

## 4.3 Phases of UVM

UVM phases were made to synchronize the behavior of testbench. This enables organized flow from start of testbench until the end of simulation. UVM phases are mainly divided in three categories build, run and clean up phases.

#### 4.3.1 Build Phase

The build phase is responsible for two different functionalities. Building the phases and connecting the components. Components are constructed and connected at the start of simulation; this happens in zero simulation time. UVM builds components that are registered in the factory and connect them depending on how user defines the connection in connect phase. Once the components are built and connection, the elaboration is done.

### 4.3.2 Run Phase

Run phase is were simulation starts and ends. Entire simulation happens in the run phases. Run phase is time consuming and are usually defined in task. Run phase consists of resetting the DUT, setting up the DUT, generation of randomized value, driving the value, monitoring the value and comparing the results. Run phases is only terminated when the sequence is finished. Run phase is further divided as,

#### 4.3.2.1 Reset

This phase is reserved for reset behavior. This would generate reset and put the interface into default state or send reset signals to DUT. The main motivation of having this phase ahead is to bring the DUT into initial condition.

4.3 Phases of UVM 21

Figure 4.2: UVM\_Phases [2]

4.4 UVM factory 22

#### 4.3.2.2 Configure

This phase is used to configure the DUT. The configuration is done to make sure DUT is ready to accept any transactions which is about to be sent in near future.

#### 4.3.2.3 Main

Main phase is where the stimulus is generated and sent to DUT. User can have N number of test cases or test sequence. Every test case is generating a random variable which is defined using "rand" or "randc" system function. Main Phases is responsible for generating the stimulus using random generator.

#### **4.3.2.4** Shutdown

Shutdown is responsible to assure the stimulus generated in the main phases have propagated through the DUT. It also makes sure any resultant data have been drained away.

### 4.3.3 Clean-up Phase

This phase is initialized once the simulation is done. This phase is responsible to collect the data generated during the simulation run phase. It extracts the information such as reports, errors etc.

### 4.4 UVM factory

UVM factory is a repository where the components of test bench are manufactured and stored. Only one instance of factory is present in a simulation. All the testbench components needs to 4.4 UVM factory 23

be registered and created in the factory. There are two types namely components and objects which can be registered and created in factory.

### 4.4.1 UVM\_Objects

UVM objects are instance that is dynamic in nature and changes during the run time. uvm\_seq\_item and uvm\_sequence are the dynamic objects in testbench environment. User can define and create objects for multiple sequence and transactions. They can be invoked depending on the user needs. UVM objects are registered using uvm\_object\_utilis method and then object is created for every single instance invoked.

### 4.4.2 UVM\_component

UVM components are instance that is static in nature and does not change during the run time. UVM components are static and built during the build phase of UVM. These components can be considered as physical structure or building block of UVM environment. Driver, Sequencer, monitor and scoreboard are examples of components. UVM components are registered using uvm\_component\_utils method. Object are created every time when these components are invoked.

### 4.4.3 Type Override

The component are created using type\_id::create() method instead of new(). Both the methods lets you create a object but new() does not let type override. When a object is created using new() methods, the type of the object can not be changed. This means, once an object is created and memory is allocated the behavior of the object cannot be altered. This is replaced using type\_id::create() which lets user to override the behavior of the object type. Again, this is

4.4 UVM factory 24

one enhancement that lets user to reuse the objects by changing its type. There are few UVM override methods that enables user to replace the object instead of type. UVM gets highly flexible here and provides multiple options to user.

## Chapter 5

# **Custom UVM Backend Design**

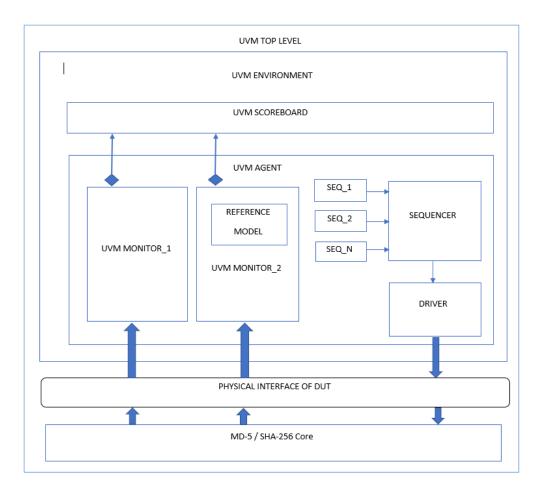

This chapter discusses the structure and design of the custom target-specific UVM framework. UVM is reusable, factor-based environment which can enhance the productivity of verification. UVM is generally used to verify at different level of abstraction from IP, block, chip level. Verification is usually bottom-top approach which provides level of confidence for verification engineers. Section 5.1 discusses the UVM Design for IP verification and Section 5.2 discusses the UVM Design for Block Level Verification.

## 5.1 UVM IP-Level Design

UVM is sophisticated, but on the other hand it is flexible for user requirements. This overall section describes how UVM environment could be developed for IP-Level Verification. IP level is the low level of abstraction in verification process. SHA-256 and MD5 are the two different IP used as DUT to verify its functionality. Next two sub-session describes the environment components of the UVM framework and the process flow between DUT/UVM/C model. For IP level Verification, Generic UVM framework was used. This consists of Multi-

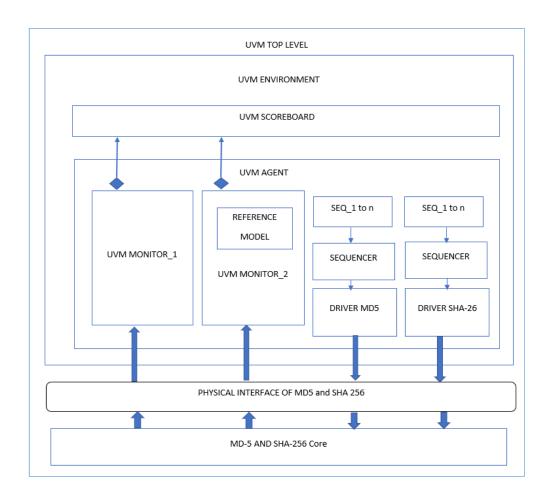

Figure 5.1: IP-Level Design

ple test sequence, sequencer, driver, couple of monitors, Scoreboard. The UVM continuously interacts with the DUT and Reference model during "Run Phase" and compares the results of DUT with reference model and updates the coverage. Phase objection were used to start the sequencer and end the UVM in appropriate way.

#### **5.1.1 UVM Environment for IP-Level**

1. **Sequence**: UVM\_Sequence is the base class, which can be extended to define streams of test sequences for DUT. Here, 5 different test sequences are defined, however they

only have 1 sequencer to run. In other words, only one test sequence can be active at any point of simulation time. In order to run parallel test cases, DUT should be configured in pipelined fashion. "set\_arbitration(UVM\_SEQ\_ARB\_USER)" was used to arbitrate between the sequences. As mentioned, one sequence is selected among five sequences. The sequence is selected based on the priority given as argument. Once, the high priority sequence is completed, the next sequence is selected. In order to achieve this, Multiple sequences are defined extending UVM\_sequence class. Top level virtual sequence is defined in which actual multiple sequences are instantiated and object are created respectively. This virtual sequence is connected to the sequencer.

- 2. 2Sequencer: As mentioned, one sequencer is defined. Sequencer is intermediate connection between the sequence and Driver. The connection between sequencer and driver is static, which is connected using uvm\_seq\_port. The connection between sequencer and sequence is dynamic and changes during run time depending on the logic inside the virtual sequence. In this case, Priority is used to switch between the multiple sequences in the virtual sequence. At any point of simulation time one sequence is connected to the driver through the sequencer.

- 3. Driver: Driver drives the DUT using the random data generated in the sequence. In other words, driver is heart of UVM environment which is responsible to extract the random data from sequence and drive the DUT. Every DUT has its own method to drive the Inputs and outputs. In MD5, data is sent, and output is collected with some reference signals. In SHA-256, the data should be placed in some loop fashion and output is collected with some reference signals. The communication between the Driver and the sequence happens through UVM\_seq\_port. There are few methods like get\_next\_item, which gets the next random value from sequence and item\_done, which implies trans-

action is completed. There are few non-blocking methods like get(), put() which can be handy when more than one random value is required for 1 variable. The communication between the driver and the DUT happens through interface. Driver gets the access to physical interface using the virtual interface which can be passed through the uvm\_config\_db method. This is one of the excellent features added in UVM, which, unlike SystemVerilog, eliminates passing virtual interface through all hierarchical level until driver is reached.

- 4. **Monitor**: One monitor simply monitors the response from DUT. It collects the output from DUT for every valid transaction. This is where UVM becomes transaction level modeling ignoring low level abstraction noises from DUT. The collected value is sent to Scoreboard using Analysis\_port, which is discussed in scoreboard section. Another monitor has reference model embedded in it. This reference model is simply C model which is used to generate expected values. This monitor monitors the input to DUT for every valid transaction and sends the same input to the reference model embedded inside it. The output from reference model is collected and sent to scoreboard for comparison.

- 5. **Agent**: Agent provides high level abstraction of Sequence, Sequencer, Driver and x2 Monitor. Agent provides the environment to wrap these components. The components are built and connected here. Agent holds analysis port which is connected to the analysis port of Monitor. The other end of agent's analysis port is connected to the scoreboard.

- 6. Scoreboard: Scoreboard is the component where results are compared and displayed. Monitor sends the value to scoreboard using analysis port through agent. Scoreboard gets these values for DUT and Reference model, compares them and updates the test results. In other words, scoreboard is simply a subscriber to the monitor. Inside scoreboard, there are 2 FIFOs that collects the value from DUT and reference model in each.

This eliminates the synchronization issues between the two results.

7. **Environment**: The environment is the highest-level abstraction of UVM components which wraps the Scoreboard and Agent. Components are built and connected in the environment. To access any component in UVM framework, it needs to be accessed through the environment.

#### 5.1.2 Design Flow

It is obvious flow starts with randomization and ends at comparing the output with expected result. UVM works in top-bottom methodology, sequence is started on sequencer at UVM\_test. There is multiple sequence, but they all have only sequencer on which they can run. Every sequence shares single sequencer and only one can run at a point of time. To control this, virtual sequence is used which decides what sequence will run when. Virtual sequence is configured using priority, each sequence is provided with some level of priority. Once, this is called sequence starts sending randomized value to driver. Driver and sequence are connected using peer to peer type connection called seq\_item\_port. They both work on system call protocols get\_next\_item, item\_done, get, put. They are blocking methods and waits for transaction to be completed. Driver drives the DUT with the random value generated from sequence.

Monitor monitors the ports of DUT and captures every valid transaction. This eliminates unwanted low-level abstraction noises. One monitor is provided with access to reference model to generate expected result. This is done using DPI library which enables transaction between SystemVerilog and C language. Both the monitors send the DUT output and reference output to the analysis port. Scoreboard is connected to other end of the analysis port which samples these values. The overall flow is synchronized using system methods raise\_objection and drop\_objection. Once all the raised objections are dropped the simulation ends.

Assertions are defined in interface where direct access to input/output is available. Assertions run in parallel during Run phase during simulation time. This provides a level of confidence to verify the functionality of DUT. Cover group consists cover points (input and output) which monitors the toggling of bits. Cover group also provides code coverage which implies how much of code is being executed.

### 5.2 UVM Block Level Design

Sha-256 and MD5 were wrapped together as single block. They are instantiated and wired through a top-level unit. UVM framework was developed to test this block which consists of two independent IP's. Testbench was modified to drive two different IP's. One of the interesting things was these two IP's were driven, sampled, verified in parallel independent of each other. Systemverilog Fork comes handy to perform parallel task.

#### **5.2.1 UVM Environment for Block-Level:**

1. Sequence: UVM\_Sequence is the base class, which can be extended to define streams of test sequences for DUT. Here, 5 different test sequences are defined, individually for SHA-256 and MD5. Each DUT has its own sequencer on which one sequence would run at a time. "set\_arbitration(UVM\_SEQ\_ARB\_USER)" was used to arbitrate between the sequences. one sequence is selected among five sequences. The sequence is selected based on the priority given as argument. Once, the high priority sequence is completed, the next sequence is selected. In order to achieve this, Multiple sequences are defined extending UVM\_sequence class. Top level virtual sequence is defined in which actual multiple sequences are instantiated and object are created respectively. This virtual sequence is connected to the sequencer.

Figure 5.2: Block-Level Design

- 2. Sequencer: As mentioned, two sequencers were defined. Sequencer is intermediate connection between the sequence and Driver. The connection between sequencer and driver is static, which is connected using uvm\_seq\_port. The connection between sequencer and sequence is dynamic and changes during run time depending on the logic inside the virtual sequence. In this case, Priority is used to switch between the multiple sequences in the virtual sequence. At any point of simulation time one sequence is connected to the driver through the sequencer.

- 3. **Driver**: Two Drivers were used to drive two DUT in parallel. Driver drives the DUT using the random data generated in the sequence. In other words, driver is heart of UVM environment which is responsible to extract the random data from sequence and drive the DUT. In MD5, data is sent, and output is collected with some reference signals. In SHA-256, the data should be placed in some loop fashion and output is collected with some reference signals. The communication between the Driver and the sequence happens through UVM\_seq\_port. There are few methods like get\_next\_item, which gets the next random value from sequence and item\_done, which implies transaction is completed. There are few non-blocking methods like get(), put() which can be handy when more than one random value is required for 1 variable. The communication between the driver and the DUT happens through interface. Driver gets the access to physical interface using the virtual interface which can be passed through UVM\_Config\_DB method. This is one of the excellent features added in UVM unlike SystemVerilog, which eliminates passing virtual interface through all hierarchical level until driver is reached.

- 4. **Monitor**: One monitor simply monitors the response from both MD5 and SHA-256. It collects the output from DUT for every valid transaction. This is where UVM becomes transaction level modelling ignoring low level abstraction noises from DUT. The col-

lected value is sent to Scoreboard using Analysis\_port, which is discussed in scoreboard section. Another monitor has reference model embedded in it. This reference model is simply C model which was used to generate expected values. This monitor monitors the input to DUT for every valid transaction and sends the same input to the reference model embedded inside it. The output from reference model is collected and sent to scoreboard for comparison.

- 5. Agent: Agent provides the environment to wrap sequencer, driver and monitor. The components are built and connected here. Agent holds analysis port which is connected to the analysis port of Monitor. The other end of agent's analysis port is connected to the scoreboard.

- 6. **Scoreboard**: Scoreboard is the component where results are compared and displayed. Monitor sends the value to scoreboard using analysis port through agent. Scoreboard gets these values for DUT and Reference model, compares them and updates the test results. In other words, scoreboard is simply a subscriber to the monitor. Inside scoreboard, there are 4 FIFO that collects the value from DUT and reference model in each. This eliminates the synchronization issues between the two results.

- 7. Environment: The environment is the highest-level abstraction of UVM components which wraps the Scoreboard and Agent. Components are built and connected in the environment. To access any component in UVM framework, it needs to be accessed through the environment.

#### **5.2.2** Verification Flow

The testbench starts with randomization and ends at comparing the output with expected result. However, this testbench drives two DUTs, the SHA-256 and MD5 parallel and irrespective of each other. UVM works in top-down methodology; the sequence is started on sequencer at uvm\_test. There is multiple sequences for MD5 and SHA-256, but they all have only one sequencer on which they can run. Every sequence shares single sequencer and only one can run at a point of time. To control this, virtual sequence is used which decides what sequence will run when. Virtual sequence is configured using priority, each sequence is provided with some level of priority. Once, this is called sequence starts sending randomized value to driver. Driver and sequence are connected using peer to peer type connection called seq\_item\_port. They both work on system call protocols get\_next\_item, item\_done, get, put. They are blocking methods and waits for transaction to be completed. Driver drives the DUT with the random value generated from sequence.

Monitor monitors the ports of DUT and captures every valid transaction. This eliminates unwanted low-level abstraction noises. One monitor is provided with access to reference model to generate expected result. This is done using DPI library which enables transaction between SystemVerilog and C language. Both the monitors send the DUT output and reference output to the analysis port. Scoreboard is connected to other end of the analysis port which samples these values. The overall flow is synchronized using system methods raise\_objection and drop\_objection. Once all the raised objections are dropped the simulation ends.

Assertions are defined in interface where direct access to input/output is available. Assertions run in parallel during run phase during simulation time. This provides a level of confidence to verify the functionality of DUT. Cover group consists cover points (input and output) which monitors the toggling of bits. Cover group also provides code coverage which implies how much of code is being executed.

# Chapter 6

### **Results and Discussion**

This chapter discusses the results of SHA-256 and MD5. IP's were successfully verified using UVM environment as independent IP's and as block level unit. MD5 takes around 900ns for every hash function and SHA-256 takes about 1400ns. Overall 3 testbench's were made and their source code is available in appendix.

### **6.1** Synthesis Report

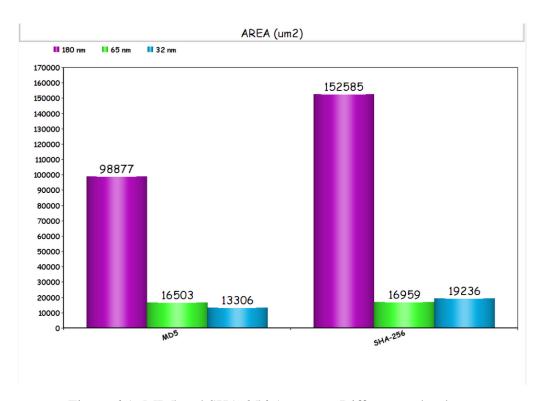

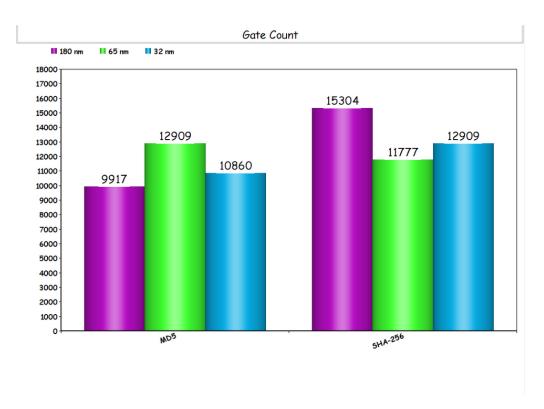

The IP's were synthesized on different technology 180 nm, 65 nm and 32 nm. The results are compared and shown in the table6.16.2.

### **6.2** Simulation Report

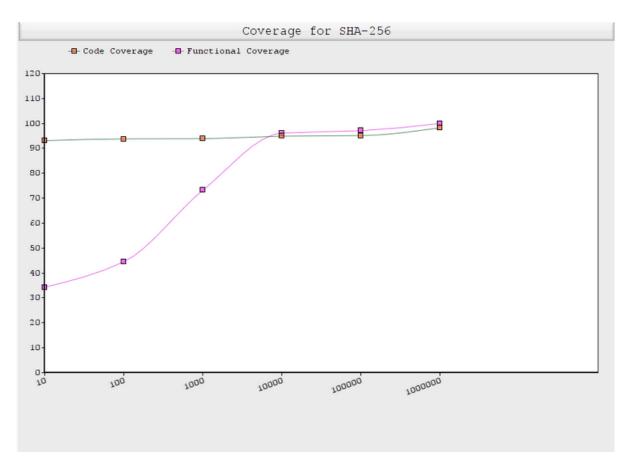

SHA-256 and MD5 was verified in RTL level and Gate level simulation. The correctness of the logic matches in RTL level matches gate level. Gate level simulation is technology dependent and gives the exact timing results. Propagation delay of signals, and setup and hold time issues can be monitored in gate level simulation. The test stimulus was generated for different

36

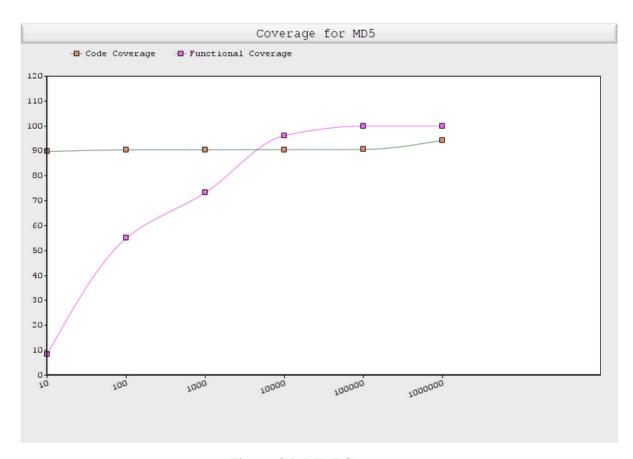

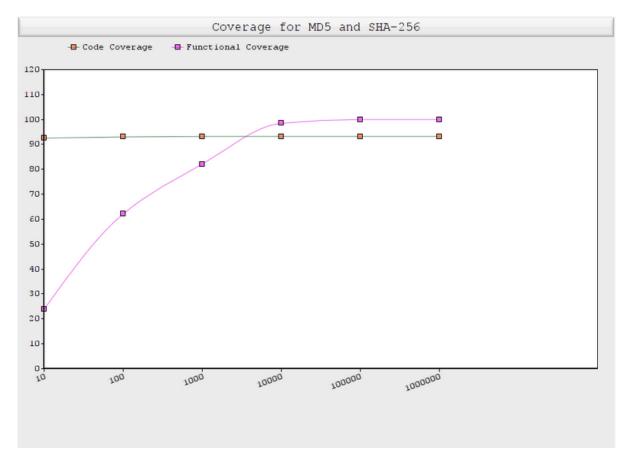

combination of input, which was monitored using coverage. The comparison between number of test cases and coverage is shown in table. Coverage increases as the number of test stimulus increases which is shown in graph. Assertions were monitoring the protocols that DUT needs to maintain at any point of time. Assertion is independent of test cases and is expected to be passing at any point of time. As these assertions do not monitor the output, they cannot verify the correctness of DUT. C model was used to generate expected results, which was used to verify the correctness of device. The IP's works as intended for different combination of stimulus.

Overall time spent in simulation is enormous. For a 32-bit adder in a processor, there are 4.2 billion test cases. Considering all other logic unit, verification of entire processor would cost months of simulation. The motivation behind the block level verification is to increase the simulation throughput. The block level IP verification environment drives both MD5 and SHA-256 parallelly. This method becomes handy when large block of SOC needs to be verified. However, this is limited to the resources available in work station. Here is where UVM becomes flexible as per user needs and stands out on top of verification methodology.

Table 6.1: Synthesis Results

| SHA-256 Core                  | 180 nm | 32 nm | 65 nm |

|-------------------------------|--------|-------|-------|

| Ports                         | 1858   | 1858  | 1858  |

| Nets                          | 7134   | 6802  | 6727  |

| Cells                         | 4763   | 4210  | 4355  |

| Total Area (um <sup>2</sup> ) | 152585 | 16959 | 19623 |

| Gate Count                    | 15304  | 12909 | 11777 |

|                               |        |       |       |

| MD5 Core                      | 180nm  | 32nm  | 65nm  |

| Ports                         | 665    | 661   | 661   |

| Nets                          | 5304   | 5534  | 4889  |

| Cells                         | 4564   | 4562  | 4157  |

| Total Area (um <sup>2</sup> ) | 98877  | 16508 | 13306 |

| Gate Count                    | 9917   | 10860 | 12909 |

Table 6.2: Timing, Power Results

|                             | SHA-256 CORE | MD5 CORE  |  |  |  |

|-----------------------------|--------------|-----------|--|--|--|

| Timing @ 100 MHz            |              |           |  |  |  |

| Required Time               | 0.8          | 19.7      |  |  |  |

| Arrival Time                | - 0.29       | - 3.2     |  |  |  |

| Worst Slack                 | 0.5          | 16.5      |  |  |  |

| Power Consumption @ 100 MHz |              |           |  |  |  |

| Internal Power              | 3.8 mW       | 311.03 uW |  |  |  |

| Switching Power             | 630.2 uW     | 133.8 uW  |  |  |  |

| Total Power                 | 4.43 mW      | 30.7 nW   |  |  |  |

Figure 6.1: MD5 and SHA-256 Area over Different technology

Figure 6.2: MD5 and SHA-256 Gate Count over Different technology

Table 6.3: Coverage across different test cases

| Test Cases | SHA- 256 Core                 |                       |                      |  |  |

|------------|-------------------------------|-----------------------|----------------------|--|--|

|            | Code Coverage %               | Functional Coverage % | Assertion Coverage % |  |  |

| 50         | 93.1                          | 34.3                  | 100                  |  |  |

| 100        | 93.8                          | 44.5                  | 100                  |  |  |

| 1000       | 93.87                         | 73.82                 | 100                  |  |  |

| 10000      | 94.9                          | 96.12                 | 100                  |  |  |

| 100000     | 95.12                         | 97.1                  | 100                  |  |  |

| 1000000    | 98.23                         | 100                   | 100                  |  |  |

|            | MD5 Core                      |                       |                      |  |  |

| 50         | 89.77                         | 8.4                   | 100                  |  |  |

| 100        | 90.4                          | 55                    | 100                  |  |  |

| 1000       | 90.44                         | 73.2                  | 100                  |  |  |

| 10000      | 90.49                         | 96.2                  | 100                  |  |  |

| 100000     | 90.55                         | 100                   | 100                  |  |  |

| 1000000    | 94.2                          | 100                   | 100                  |  |  |

|            | MD5 and SHA-256 Combined Core |                       |                      |  |  |

| 50         | 92.5                          | 23.9                  | 100                  |  |  |

| 100        | 93                            | 62.15                 | 100                  |  |  |

| 1000       | 93.2                          | 82.1                  | 100                  |  |  |

| 10000      | 93.2                          | 98.5                  | 100                  |  |  |

| 100000     | 93.2                          | 100                   | 100                  |  |  |

| 1000000    | 93.2                          | 100                   | 100                  |  |  |

Figure 6.3: SHA-256 Coverage

Figure 6.4: MD5 Coverage

Figure 6.5: MD5 and SHA-256 Coverage

## Chapter 7

## **Conclusion**

MD5 and SHA-256 RTL cores were successfully verified using UVM and SystemVerilog. A reference model in C language was used to generate expected values and imported into the UVM framework. DUT output data was compared with expected model values to verify the correctness of the each core. Assertions were used to verify the protocol over which each DUT communicates. Additional assertions were used to check the DUT misbehavior. This provided a level of confidence and ensured each RTL core functions properly.

The MD5 Core takes 32-bit data which can contain up to 4.2 billion different combination values. Randomizing without any constraints might end up not hitting several possible regions. For this purpose, the randomization is divided in 5 regions (4.2 billion / 5), each covering a region. Each region is embedded in a dedicated sequence and randomized several times to ensure high coverage. This method increases the probability of finding corner cases. Coverage metrics were used to keep a track on randomization. A similar method was followed to verify the SHA-256 core. Both cores achieved 100% functional coverage at 1 million input combinations in every region. Note however code coverage remained close to 95%.

7.1 Future work

### 7.1 Future work

• From code coverage metrics, we can analyze that the code is not compact, therefore certain RTL blocks can be rewritten to make the code more compact.

- MD5 takes around 800 ns and SHA-256 takes 1400 ns for processing one input message.

The RTL could be optimized to improved to reduce these times.

- MD5 and SHA-256 can process only one input at any point of time. Pipelining can be introduced which would allow the cores to take streams of input data.

- The timing on few paths are not very great, therefore certain nets can be remodeled.

- [1] Bart Preneel. CRYPTOGRAPHIC HASH FUNCTIONS: AN OVERVIEW. In *Proceedings of the 6th International Computer Security and Virus Conference (ICSVC 1993)*, volume 9., pages 461 479, 1993. URL: https://www.esat.kuleuven.be/cosic/publications/article-289.pdf.

- [2] K. Jarvinen, M. Tommiska and J. Skytta. Hardware Implementation Analysis of the MD5 Hash Algorithm. *Proceedings of the 38th Annual Hawaii International Conference on System Sciences, Big Island, HI, USA*, 2005.

- [3] IEEE Standard for Universal Verification Methodology Language Reference Manual, 2017.

- [4] K. Salah. A UVM-based smart functional verification platform: Concepts, pros, cons, and opportunities. In 2014 9th International Design and Test Symposium (IDT), pages 94–99, December 2014. doi:10.1109/IDT.2014.7038594.

- [5] J. Bromley. If SystemVerilog is so good, why do we need the UVM? Sharing responsibilities between libraries and the core language. In *Proceedings of the 2013 Forum on specification and Design Languages (FDL)*, pages 1–7, September 2013.

[6] Ray Salemi. *The UVM Primer: A Step-by-Step Introduction to the Universal Verification Methodology*. Boston Light Press, 2013.

- [7] B. Min and G. Choi. RTL functional verification using excitation and observation coverage,. Sixth IEEE International High-Level Design Validation and Test Workshop, Monterey, CA, USA, 2001.

- [8] C. Kuznik and W. Muller. Aspect enhanced functional coverage driven verification in the SystemC HDVL. *International SoC Design Conference*, 2011.

- [9] P. Ma, Q. Zhao, Y. Fan, M. Liu, and K. Li. The design and verification of packet processing engine model using SystemC. In 2011 International Conference on Electronics, Communications and Control (ICECC), pages 1099–1101, September 2011. doi:10.1109/ICECC.2011.6066395.

- [10] P. D. Mulani. SoC Level Verification Using System Verilog,. Second International Conference on Emerging Trends in Engineering & Technology, Nagpur, 2009.

- [11] Jordan Cote Zhijie Shi, ChujiaoMa and Bing Wang. *Hardware Implementation Of Hash Functions*. Springer Science+Business Media, LLC, 2012. doi:10.1007/978-1-4419-8080-9\_2.

- [12] Y. W. Hau M.Khalil, M.Nazrin. Implementation of SHA-2 Hash Function for a Digital Signature System-on-Chip in FPGA. VLSI-eCAD Research Laboratory (VeCAD) Faculty of Electrical Engineering Universiti Teknologi Malaysia (UTM), 2008.

- [13] Dengguo Feng XiaoyunWang and Hongbo Yu Xuejia Lai. Collisions for Hash Functions MD4, MD5, HAVAL-128 and RIPEMD, 2004. URL: http://eprint.iacr.org/2004/199.

[14] D. Lee. Hash Function Vulnerability Index and Hash Chain Attacks. In 2007 3rd IEEE Workshop on Secure Network Protocols, pages 1–6, October 2007. doi:10.1109/ NPSEC.2007.4371616.

- [15] M. Wang and Y. Li. Hash Function with Variable Output Length. *International Conference on Network and Information Systems for Computers, Wuhan*, 2015.

- [16] M. Singh and D. Garg. Choosing Best Hashing Strategies and Hash Functions. In 2009 IEEE International Advance Computing Conference, pages 50–55, March 2009. doi: 10.1109/IADCC.2009.4808979.

- [17] X. Qiuyun, H. Ligang, L. Qiming, G. Shuqin, and W. Jinhui. The Verification of SHA-256 IP using a semi-automatic UVM platform. In 2017 13th IEEE International Conference on Electronic Measurement Instruments (ICEMI), pages 111–115, October 2017. doi:10.1109/ICEMI.2017.8265733.

- [18] W. Ni and J. Zhang. Research of reusability based on UVM verification. *IEEE 11th International Conference on ASIC*, 2015.

- [19] R. Madan, N. Kumar and S. Deb. Pragmatic approaches to implement self-checking mechanism in UVM based TestBench,. *International Conference on Advances in Computer Engineering and Applications, Ghaziabad*, 2015.

- [20] R. P. McEvoy, F. M. Crowe, C. C. Murphy and W. P. Marnane. Optimisation of the SHA-2 family of hash functions on FPGAs. *IEEE Computer Society Annual Symposium on Emerging VLSI Technologies and Architectures (ISVLSI'06), Karlsruhe*, 2006.

- [21] S. binti Suhaili and T. Watanabe. Design of high-throughput SHA-256 hash function based on FPGA. 6th International Conference on Electrical Engineering and Informatics (ICEEI), Langkawi, 2017.

[22] A. T. Hoang, K. Yamazaki and S. Oyanagi. Multi-stage Pipelining MD5 Implementations on FPGA with Data Forwarding. *6th International Symposium on Field-Programmable Custom Computing Machines, Palo Alto, CA*, 2008.

- [23] H. M. Heys J. Deepakumara and R. Venkatesan. FPGA implementation of MD5 hash algorithm. In *Canadian Conference on Electrical and Computer Engineering 2001. Conference Proceedings (Cat. No.01TH8555)*, volume 2, 2001.

- [24] Chris Spear. *SystemVerilog for Verification*. Springer Science+Business Media, LLC, 2012.

- [25] Accellera Systems Initiative (Accellera). *Universal Verification Methodology (UVM) 1.2 User's Guide*, October 2015.

- [26] Verification Guide, 2016. SystemVerilog and UVM Resources. URL: https://www.verificationguide.com/p/home.html.

- [27] SHA 256 Verilog source code. URL: https://github.com/secworks/sha256/tree/master/src/rtl.

- [28] SHA 256 Reference Model in C. URL: https://github.com/B-Con/crypto-algorithms/blob/master/sha256.c.

- [29] MD5 Verilog Source Code. URL: https://github.com/stass/md5\_core.

- [30] MD5 Reference Model in C. URL: https://openwall.info/wiki/people/solar/software/public-domain-source-code/md5.

# **Appendix A**

## **Source Code for MD5**

#### A.1 MD5 Interface

```

interface md5_interface ;

// ports

logic clk ;

logic reset ;

logic rdy_i ;

logic [31:0] msg_i ;

logic [127:0] hash_o ;

logic rdy_o ;

logic busy_o ;

logic [31:0] syn;

```

A.1 MD5 Interface 51

```

//--- Assertion 1: Reset and Rdy signals -----

// Rdy is followed by reset signal

sequence assertreset;

(rdy_o == 1'b1);

endsequence

property assert_reset ;

@(posedge clk)

(reset == 1'b1) \mid -> \#\#3 \ assertreset;

endproperty

assertion_reset : assert property ( assert_reset) else

$display ("Data sending failed" );

//--- Assertion 2: Rdy output and busy signals ----//

// rdy_o is never asserted when busy_o is high

sequence rdybusy;

(rdy_o == 1'b0);

endsequence

property rdy_busy ;

@(posedge clk)

(busy_o == 1'b1)   |-> rdybusy;

endproperty

assertion_rdy_busy : assert property ( rdy_busy) else $display

(" Ready and Busy asserted concurrently");

```

A.1 MD5 Interface 52

```

//--- Assertion 3 : hash_o----//

// Hash_o is never 0 at any point of time

hash0 : assert property (@(posedge clk) ## 1 hash_o != 128'

H0) else $display (" Ready and Busy asserted concurrently"

);

endinterface : md5_interface

```

### A.2 MD5 Sequence and Sequencer

```

class md5_seq_item extends uvm_sequence_item ;

virtual md5_interface vif;

//---properties of sequence ----//

logic [127:0] hash_o;

bit rdy_o;

string modelout;

bit rdy_i;

// upper and lower case with numbers

rand bit [7:0] num;

rand bit [7:0] upper;

rand bit [7:0] lower;

rand bit [31:0] msg1;

rand bit [31:0] msg2;

rand bit [7:0] msg3;

rand bit [7:0] msg4;

rand bit [31:0] msg_i;

bit [31:0] msg;

bit [31:0] sequ;

constraint new_con { msg1[7:0] inside { [48:57], [65:90],

[97:122] }; }

```

```

constraint new_con1 { msg1[15:8] inside { [48:57], [65:90],

[97:122] }; }

constraint new_con2 { msg1[23:16] inside { [48:57], [65:90],

[97:122] }; }

constraint new_con3 { msg1[31:24] inside { [48:57], [65:90],

[97:122] }; }

rand byte unsigned temp [];

constraint str_len {temp.size() == 4; }

constraint temp_str_ascii { foreach (temp[i]) temp[i] inside {

[65:90], [97:122] }; }

// _____ constructor —

function new(string name="");

super.new(name);

endfunction: new

//---utility and macros-

`uvm_object_utils_begin (md5_seq_item)

`uvm_field_int(hash_o, UVM_ALL_ON)

`uvm_field_int(rdy_o, UVM_ALL_ON)

`uvm_field_int(rdy_i, UVM_ALL_ON)

`uvm field int(msg i, UVM ALL ON)

`uvm_object_utils_end

```

```

endclass: md5_seq_item

// ---- sequence1 ----//

class md5_sequence1 extends uvm_sequence #(md5_seq_item);

`uvm_object_utils(md5_sequence1)

//---constructor-

function new(string name="");

super.new(name);

endfunction: new

//---randomize and sending to driver ----

task body();

integer i;

md5_seq_item req;

req = md5_seq_item::type_id::create(.name("req"), .

contxt(get_full_name()));

start_item (req);

assert (req.randomize());

finish_item(req);

endtask : body

endclass: md5_sequence1

```

```

// ---- sequence2 ----//

class md5_sequence2 extends uvm_sequence #(md5_seq_item);

`uvm_object_utils(md5_sequence2)

//---constructor-

function new(string name="");

super.new(name);

endfunction: new

//---randomize and sending to driver ----//

task body();

integer i;

md5_seq_item req;

req = md5_seq_item::type_id::create(.name("req"), .

contxt(get_full_name()));

start_item (req);

assert (req.randomize());

finish_item(req);

endtask : body

endclass : md5_sequence2

// ---- sequence3 ----//

class md5_sequence3 extends uvm_sequence #(md5_seq_item);

```

```

`uvm_object_utils (md5_sequence3)

//---constructor-

function new(string name="");

super.new(name);

endfunction: new

//---randomize and sending to driver ----

task body();

integer i;

md5_seq_item req;

req = md5_seq_item::type_id::create(.name("req"), .

contxt(get_full_name()));

start_item (req);

assert (req.randomize());

finish_item(req);

endtask : body

endclass : md5_sequence3

// ---- sequence4 ----//

class md5_sequence2 extends uvm_sequence #(md5_seq_item);

`uvm_object_utils (md5_sequence4)

```

```

//---constructor-

function new(string name="");

super.new(name);

endfunction: new

//--randomize and sending to driver ---

task body();

integer i;

md5_seq_item req;

req = md5_seq_item::type_id::create(.name("req"), .

contxt(get_full_name()));

start_item (req);

assert (req.randomize());

finish_item(req);

endtask : body

endclass: md5_sequence4

// ----Top level Virtual sequence -----//

class md5_sequence extends uvm_sequence #(md5_seq_item);

`uvm object utils (md5 sequence)

//---constructor

function new(string name="md5_sequence");

```

```

super.new(name);

endfunction: new

md5_sequence1 seq1;

md5_sequence2 seq2;

md5_sequence2 seq3;

md5_sequence2 seq4;

md5 sequence2 seq5;

//--randomize and sending to driver -

task body();

seq1 = md5_sequence1::type_id::create("seq1");

seq2 = md5_sequence2::type_id::create("seq2");

seq3 = md5_sequence3::type_id::create("seq3");

seq4 = md5_sequence4::type_id::create("seq4");

seq5 = md5_sequence5::type_id::create("seq5");

m_sequencer.set_arbitration(UVM_SEQ_ARB_USER);

fork

begin

repeat (4) begin

seq1.start(m_sequencer, this, 100);

end

end

```

```

begin

repeat (4) begin

seq2.start(m_sequencer, this, 200);

end

end

begin

repeat (4) begin

seq3.start(m_sequencer, this, 300);

end

end

begin

repeat (4) begin

seq4.start(m_sequencer, this, 400);

end

end

begin

repeat (4) begin

seq5.start(m_sequencer, this, 500);

end

end

join

endtask : body

endclass : md5_sequence

// ---- sequencer ----//

```

typedef uvm\_sequencer#(md5\_seq\_item) md5\_sequencer;

```

import "DPI-C" context function string string_sv2c (input

string str );

class md5_driver extends uvm_driver #(md5_seq_item);

bit [31:0] infake;

bit [127:0] outfake;

`uvm_component_utils(md5_driver)

// Virtual Interface

//-----

virtual md5_interface vif;

md5_seq_item req ;

//-----

// Functional coverage handler

md5_seq_item req_cg;

//-----

// Functional coverage

//-----

covergroup md5_cg;

msg_in: coverpoint req.msg_i;

msg_in_valid : coverpoint vif.hash_o ;

```

```

cross req.msg_i, vif.hash_o ;

endgroup: md5_cg

//----

// Functional coverage display class

function void display ();

$display ("[%tns] input = %h", $time, req_cg.msg_i);

endfunction: display

//-----

// Constructor

function new (string name, uvm_component parent);

super.new(name, parent);

md5\_cg = new;

endfunction: new

//-----

// build phase

//----

function void build_phase(uvm_phase phase);

super.build_phase(phase);

void '( uvm_resource_db #( virtual md5_interface ) ::

read_by_name

(.scope("ifs"), .name("md5_interface"), .val(vif)));

endfunction: build_phase

// generating random string

```

```

function string get_str ();

string str;

foreach (req.temp[i])

str = { str, string '(req.temp[i]) };

return str;

endfunction

//-----

// run phase

//-----

task run_phase(uvm_phase phase);

drive();

endtask : run_phase

virtual task drive();

string randomi;

integer counter = 0, state = 0;

integer j;

string modelin;

string modelout;

string rtloutstring;

bit [127:0] modeloutb;

string dummy = "hello";

logic [127:0] rtlout;

bit [7:0] check1 = 8'H61;

string check2;

```

```

bit [127:0] checksum = 128'Habcd1234abcd1234abcd1234abcd1234;

// \text{md5\_cg} = \text{new}();

forever begin

if (counter == 0) begin

vif.reset \ll 1;

#10:

vif.reset \le 0;

#10;

vif.syn <= 1;

seq_item_port.get_next_item(req);

state = 1;

end

@(posedge vif.clk)

begin

case (state)

1: begin

vif.syn = 0;

vif.rdy_i = 1'b1;