#### **Rochester Institute of Technology**

### **RIT Digital Institutional Repository**

**Theses**

5-2018

### Design and Verification of a Pipelined Advanced Encryption Standard (AES) Encryption Algorithm with a 256-bit Cipher Key Using the UVM Methodology

Devyani Madhukar Mirajkar dxm4222@rit.edu

Follow this and additional works at: https://repository.rit.edu/theses

#### **Recommended Citation**

Mirajkar, Devyani Madhukar, "Design and Verification of a Pipelined Advanced Encryption Standard (AES) Encryption Algorithm with a 256-bit Cipher Key Using the UVM Methodology" (2018). Thesis. Rochester Institute of Technology. Accessed from

This Master's Project is brought to you for free and open access by the RIT Libraries. For more information, please contact repository@rit.edu.

# DESIGN AND VERIFICATION OF A PIPELINED ADVANCED ENCRYPTION STANDARD (AES) ENCRYPTION ALGORITHM WITH A 256-BIT CIPHER KEY USING THE UVM METHODOLOGY

by Devyani Madhukar Mirajkar

GRADUATE PAPER

Submitted in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE in Electrical Engineering

| Approved by:                                                                                                         |    |

|----------------------------------------------------------------------------------------------------------------------|----|

| Mr. Mark A. Indovina, Lecturer<br>Graduate Research Advisor, Department of Electrical and Microelectronic Engineerin | ng |

| Dr. Sohail A. Dianat, Professor  Department Head, Department of Electrical and Microelectronic Engineering           |    |

DEPARTMENT OF ELECTRICAL AND MICROELECTRONIC ENGINEERING

KATE GLEASON COLLEGE OF ENGINEERING

ROCHESTER INSTITUTE OF TECHNOLOGY

ROCHESTER, NEW YORK

MAY, 2018

#### **Declaration**

I hereby declare that except where specific reference is made to the work of others, that all content of this Graduate Paper are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other University. This Graduate Project is the result of my own work and includes nothing which is the outcome of work done in collaboration, except where specifically indicated in the text.

Devyani Madhukar Mirajkar May, 2018

### Acknowledgements

"No endeavor achieves success without the advice and co-operation of others."

I would like to thank my advisor, Prof. Mark A.Indovina, for his invaluable guidance, support, encouragement and also for his cooperation all throughout the semester. It is due to his enduring efforts, patience and enthusiasm, which has given a sense of direction and purposefulness to this Graduate Research Project and ultimately made it a success.

#### **Abstract**

Encryption is the process of altering information to make it unreadable by anyone except those having the key that allows them to change information back to the original readable form. Encryption is important because it allows you to securely protect the data that you don't want anyone else to have access to. Today, the Advanced Encryption Standard (AES) is the most widely adopted encryption method. Till date there are no cryptanalytic attacks discovered against AES. Hence the verification of the hardware implementation of the AES Core is of utmost importance. In this research paper, the design and verification of a pipelined AES hardware module using a 256-bit cipher key is discussed in detail. The verification environment is developed using the Universal Verification Methodology (UVM) and SystemVerilog. The verification environment will validate the implementation of the AES Encryption Algorithm by comparing the outputs of the hardware design Design Under Test and a reference model developed in C.

# **Contents**

| Co | onten   | CS CONTRACTOR OF THE PROPERTY | •   |

|----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Li | st of l | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | vii |

| Li | st of T | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X   |

| 1  | Intr    | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   |

|    | 1.1     | Research Goals And Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6   |

|    | 1.2     | Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6   |

| 2  | Bibl    | iographical Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8   |

| 3  | Bloc    | ek Cipher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12  |

|    | 3.1     | Block Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12  |

|    | 3.2     | Different Block Cipher Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13  |

|    | 3.3     | Block Cipher Padding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14  |

| 4  | Adv     | anced Encryption Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16  |

|    | 4.1     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16  |

|    | 4.2     | Inputs, Outputs and the State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17  |

|    | 4.3     | Cipher Transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21  |

Contents

|    |        | 4.3.1 SubBytes ( ) Transformation                          | 21         |

|----|--------|------------------------------------------------------------|------------|

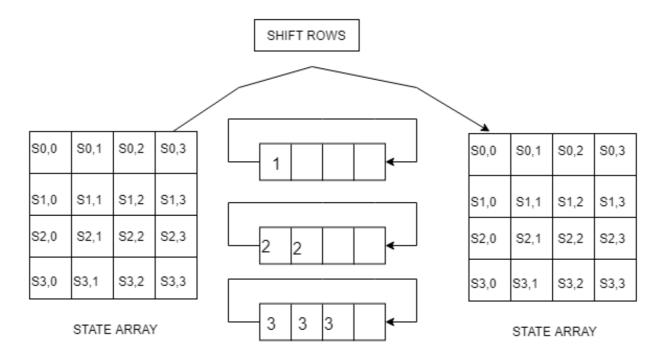

|    |        | 4.3.2 ShiftRows () Transformation                          | 23         |

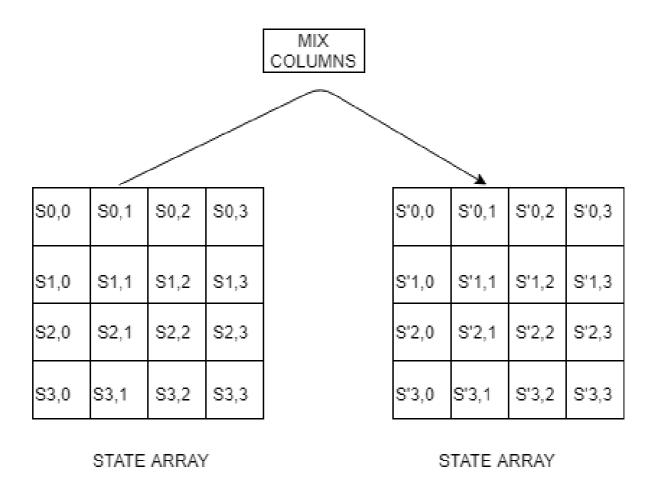

|    |        | 4.3.3 MixColumns ( ) Transformation                        | 24         |

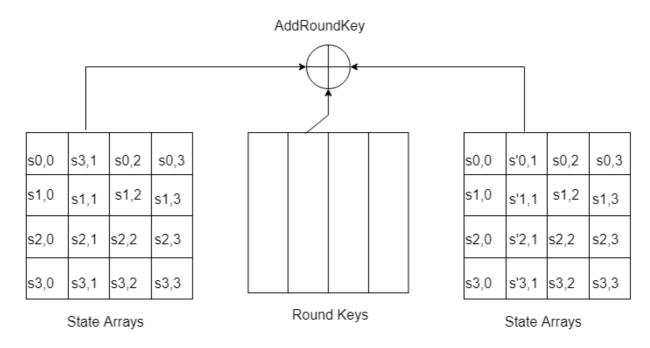

|    |        | 4.3.4 AddRoundKey ( ) Transformation                       | 24         |

|    | 4.4    | AES Key Expansion                                          | 26         |

| 5  | Bloc   | k Cipher Modes of Operation                                | <b>27</b>  |

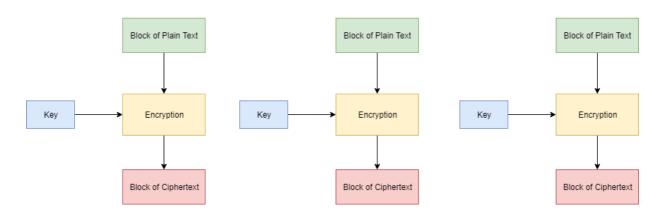

|    | 5.1    | ECB (Electronic Codebook) Mode                             | 28         |

|    | 5.2    | CBC (Cipher-Block Chaining) Mode                           | 28         |

|    | 5.3    | PCBC (Propagating or Plaintext Cipher-Block Chaining) Mode | 29         |

|    | 5.4    | CFB (Cipher Feedback) Mode                                 | <b>3</b> 0 |

|    | 5.5    | OFB (Output Feedback) Mode                                 | <b>3</b> 0 |

|    | 5.6    | CTR (Counter) Mode                                         | 31         |

| 6  | Desi   | gn and Test Methodology                                    | 33         |

|    | 6.1    | Design Implementation                                      | 33         |

|    | 6.2    | Test Methodology                                           | 36         |

| 7  | Resu   | ult and Discussion                                         | <b>40</b>  |

| 8  | Con    | clusion                                                    | 45         |

|    | 8.1    | Future Work                                                | 45         |

| Re | eferen | ces                                                        | <b>47</b>  |

| Ι  | Sour   | rce Code                                                   | 51         |

|    | I.1    | C - Model                                                  | 51         |

|    | 12     | PTI and Tastbanch                                          | 72         |

|          | •    |

|----------|------|

| Contents | VII  |

| Contents | Y 11 |

| I.3  | Interface       |

|------|-----------------|

| I.4  | Driver          |

| I.5  | Monitor         |

| I.6  | Environment     |

| I.7  | Reference Model |

| I.8  | Packet          |

| I.9  | Sequencer       |

| I.10 | Top             |

| I.11 | Test            |

# **List of Figures**

| 1.1 | Cryptosystem Block Diagram                | 1  |

|-----|-------------------------------------------|----|

| 1.2 | Flow of Encryption and Decryption Process | 2  |

| 3.1 | Block Cipher Scheme                       | 13 |

| 4.1 | AES Architecture                          | 18 |

| 4.2 | AES Encryption Process                    | 19 |

| 4.3 | State Population and Results              | 20 |

| 4.4 | SubBytes Transformation                   | 22 |

| 4.5 | ShiftRows Transformation                  | 23 |

| 4.6 | Matrix Multiplication Representation      | 24 |

| 4.7 | MixColumn Transformations                 | 25 |

| 4.8 | AddRoundKey Transformation                | 26 |

| 5.1 | Encryption using ECB mode                 | 28 |

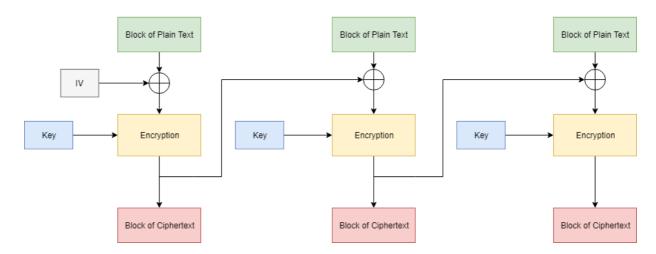

| 5.2 | Encryption using CBC mode                 | 29 |

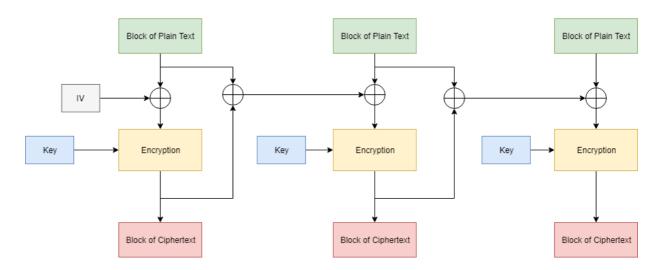

| 5.3 | Encryption using PCBC mode                | 30 |

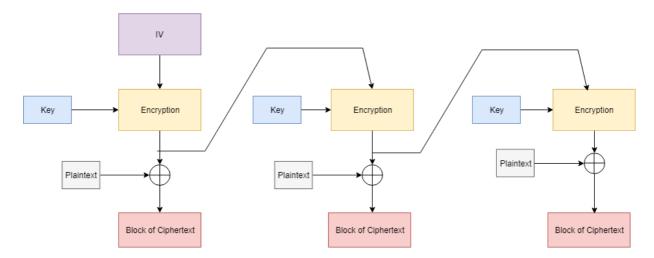

| 5.4 | Encryption using CFB mode                 | 31 |

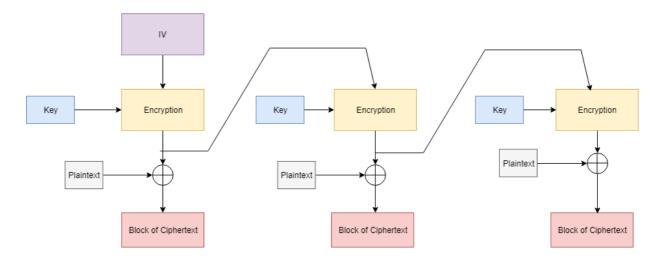

| 5 5 | Encryption using OEP mode                 | 22 |

|                 | •  |

|-----------------|----|

| List of Figures | 17 |

| List of Figures | IA |

| $\mathcal{L}$   |    |

| 5.6 | Encryption using CTR mode          | 32        |

|-----|------------------------------------|-----------|

| 6.1 | Pipelined Cipher                   | 35        |

| 6.2 | UVM Testbench                      | 37        |

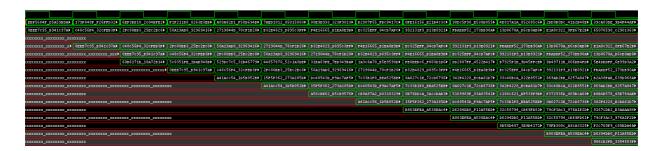

| 7.1 | Pipelined Flow                     | 10        |

| 7.2 | DUT and Model Comparison           | <b>‡1</b> |

| 7.3 | Traditional Testbench Code         | 12        |

| 7.4 | Output at time 9995ns              | 13        |

| 7.5 | State and Key for Output at 9995ns | 13        |

| 7.6 | State and Key for Output at 9695ns | 13        |

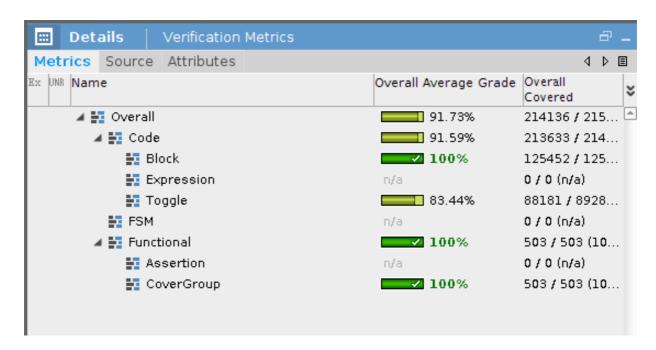

| 7.7 | Coverage Metrics                   | 14        |

# **List of Tables**

| 4.1 | AES Variations                                         | 17 |

|-----|--------------------------------------------------------|----|

| 7.1 | Area, Power, Timing and DFT Coverage of AES Encryption | 43 |

# **Chapter 1**

# Introduction

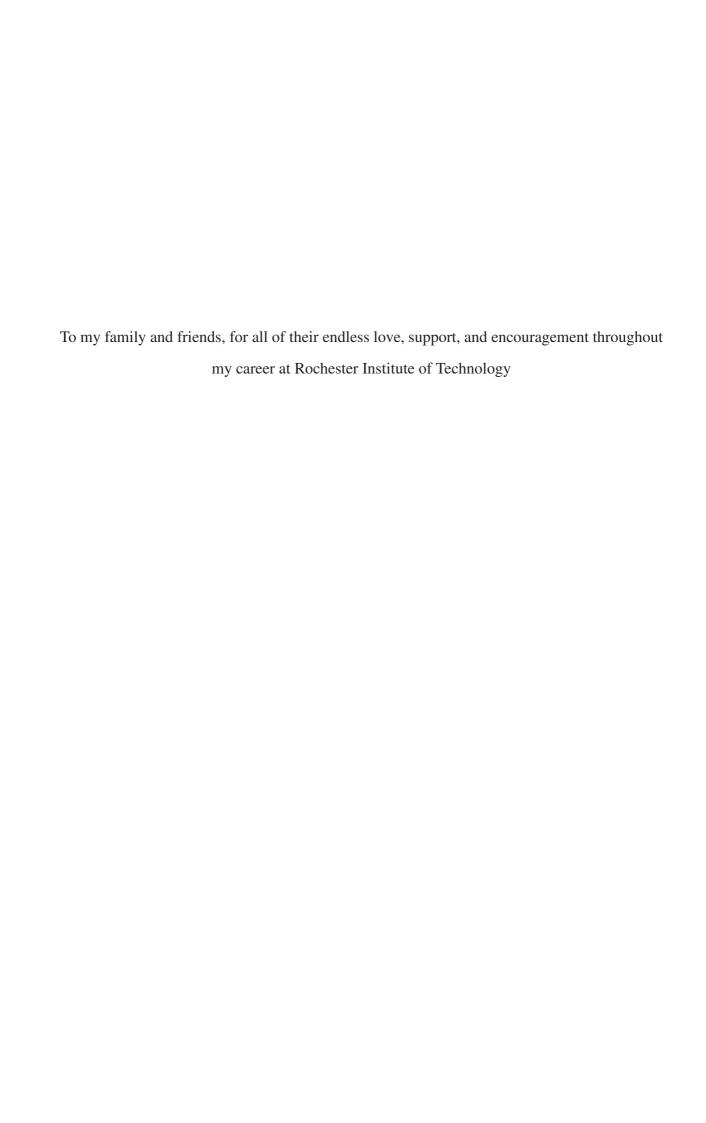

The study of Cryptosystems is known as Cryptology. It is divided into two subsystems:

- 1. Cryptography

- 2. Cryptanalysis

Figure 1.1: Cryptosystem Block Diagram

Figure 1.1 shows the Cryptosystem block diagram. Cryptography is the process of masking

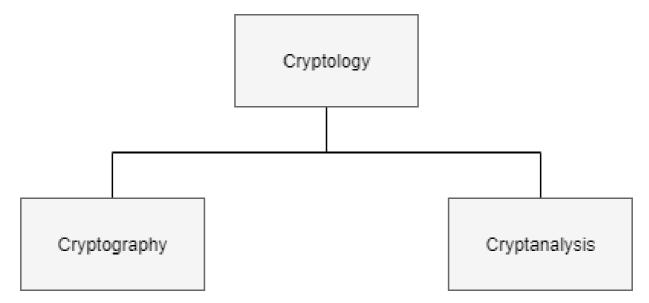

messages so as to keep it confidential for information security. The word Cryptography is derived by combining the two greek words namely *Krpto* meaning "Hidden" and *Graphene* meaning "Writing". These concealed messages can be accessed only by the authorized people. It fortifies the digital data. Cryptography is implemented with the help of mathematical algorithms which helps in storing and transmitting the data in a particular format so that the people who has the key to access the data can only get the information. Electronic Commerce, Secured Military Communication, Computer Passwords etc are some of its applications. Plain text, Cipher text, Algorithm, Key, Encryption, and Decryption are the most common terms used in Cryptography. 'Plain text' is the original text or message which is transmitted to the authorized recipients, which is presented in a sealed format. 'Cipher text' is nothing but the unintelligible text, which cannot be decoded. The plain text gets converted to a cipher text with the help of mathematical computations which are defined in an 'Algorithm'. The transmitter and the receiver may have same or different 'Key' to encrypt or decrypt the messages. The process of breaking this 'Cipher text' is known as Cryptanalysis. Figure 1.2 shows the flow of Encryption and Decryption Process.

Figure 1.2: Flow of Encryption and Decryption Process

The main purpose of Cryptography is to serve the following information security services.

The four cryptographic concerns are listed as follows:

- 1. **Confidentiality** This service hiddes the information from an unauthorized person. It is basically concerned with the privacy and secrecy of data. It is a security service that keeps the information secured from an unauthorized person. It is sometimes referred to as privacy or secrecy. This can be achieved either through cryptographic algorithms or else by physically securing the data. It is one of the basic information security service provided by Cryptography.

- 2. **DataIntegrity** Data Integrity security service recognizes any alteration to the given data. The data might get changed or altered by an unlicensed person. The data may get modified by an unauthorized entity deliberately or may be by chance. It basically checks whether the data is unimpaired from the last time when it was created, transmitted and stored by a licensed person. It cannot restrain the data from getting modified, but it gives a way for identifying whether the data has been damaged in an unlicensed manner.

- 3. **Authentication** Authentication identifies the source who is sending the data. The data which is sent by the source is validated and verified first and then this information is given to the receiver. It basically confirms that the message which has arrived at the receiver's end has come from the authorized sender and the data is unaltered. It also provides information with respect to the creation and transmission of data in terms of data and time.

- 4. **Non**—**repudiation** This service guarantees that an individual or person cannot decline the possession of a foregoing activity. It guarantees that the sender of the data cannot contradict the creation or transmission of the given data to the receiver. This service is favorable in those circumstances where there are chances of disagreement with respect to exchange of data. For example, a handwriting expert may be used by a legal service as a means of non-repudiation of signatures.

Three types of cryptographic techniques used in general. They are:

- 1. Symmetric-key cryptography

- 2. Hash functions

- 3. Public-key cryptography

- Symmetric-key Cryptography: Here the symmetric key refers to a secret key. The sender and the receiver shares the same key. The sender encrypts the plain text into the cipher text by using this secret key and forwards the text to the receiver. The receiver on reception of data uses the same key to decrypt the cipher text to the original text.

- Public-Key Cryptography: This technique has two keys, namely public and private key. The public key is the one which is used by the sender to encrypt the data, which may be freely circulated, whereas the private key associated with it is a secret key. Encryption uses public key whereas decryption process uses private key.

- Hash Functions: No key is used in this algorithm. A fixed-length hash value is evaluated as

per the plain text that makes it impossible for the contents of the plain text to be retrieved.

Hash functions are also used by operating systems to encrypt passwords.

All the features of human life are driven by communication and information. Hence, it is necessary to protect useful information from malicious activities such as attacks. Cryptographic Attacks are of two types, namely, Passive and Active Attack. This classification is done on the basis of the type of attacker. The main aim of the Passive Attack is to acquire unauthorized access to information. It basically involves stealing of information. It is very difficult to identify Passive attacks. Obstructing encrypted information and trying to break the encryption is one of the example of passive attack. Active information alters the text by performing some process on the information. This processing can be done by deleting the data, initiating unauthorized transmission of information, changing the information in an illegal activity etc.

Breaking the Cryptosystem is the main aim of the attacker and somehow retrieve the original text from the encrypted text. So as to get the original text, the attacker just needs to obtain decryption key. As soon as the key is known to the attacker, the cryptosystem is considered to be broken or cracked. They are different types of attacks which are used to break the system. They are: Ciphertext Only Attacks (COA), Known Plaintext Attack (KPA), Chosen Plaintext Attack (CPA), Brute Force Attack (BFA), Dictionary Attack (DA), Timing Attacks, Power Analysis Attack, Faulty Analysis Attack, etc.

Cryptography involves the study of secret communication. This study is implemented with the help of mathematical algorithms which is termed as 'Encryption' to encode the information and 'Decryption' to retrieve the original text from the encoded one. The different types of Encryption include Data Encryption Standard (DES), Triple DES, RSA, Blowfish, Twofish and Advanced Encryption Standard (AES). AES is the most widely accepted encryption standard and is approved by the US Government to secure classified data. AES has three different key lengths i.e, 128-bit, 192-bit or 256-bit key, making it more stronger than the 56-bit key of DES. AES Encryption is preferred over the other encryption standards because it is more secure, faster from hardware and software implementation point of view and also it supports larger key sizes.

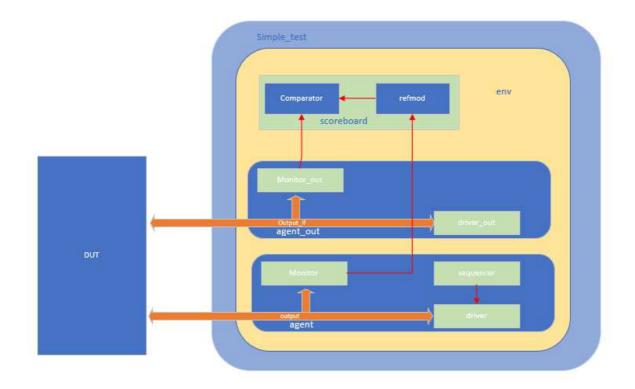

This paper gives the details regarding the Design and Verification of AES Encryption using 256-bit Cipher key using SystemVerilog and UVM methodology. UVM along with the SV brings a lot of automation, maintainability, and re-usability to the verification process. Hence, the AES encryption module is verified using UVM and SV. The verification is carried out using hardware implementation along with a C-model so as to compare the results from the Design Under Test (DUT) which is AES Encryption module and Software C-model. The UVM Verification Environment consists of different reusable components, commonly known as Universal Verification Components. Configuration, Encapsulation and High Re-usability are some of the pros of using these components.

#### 1.1 Research Goals And Contributions

The main aim of this research paper is to build a completely working modular testbench with the help of C-model and Randomization Technique. The main contribution towards this project is that, a layered testbench is developed using the reusable components like agent, driver, monitor, sequencer, etc, in SystemVerilog and UVM methodology. The research goals include:

- Understanding the Encryption Algorithm and trying to implement that using 256- bit Cipher key.

- To analyze Area and Power Optimization of 256 bit key size and comparing them with the other key lengths.

- To check whether original text is being retrieved with the help of C-model.

### 1.2 Organization

The structure of the thesis is as follows:

- Chapter 2: This chapter consists of Research Work related to AES Encryption and Decryption. It also discusses few techniques related to Key Module Generation, SBox Implementation, Area and Power Optimization.

- Chapter 3: This chapter briefly describes the Block Cipher Schemes.

- Chapter 4: Advanced Encryption Standard Algorithm is briefly discussed in this chapter.

- Chapter 5: This chapter outlines the Block Cipher Modes of Operation.

- Chapter 6: Design and Verification Methodology using the testbench components are discussed in this chapter.

1.2 Organization 7

- Chapter 7: Results are discussed in this chapter.

- Chapter 8: The conclusion and possible future work are briefly discussed in this chapter.

# Chapter 2

# **Bibliographical Research**

Design and Verification of a given hardware module is very important as the efficiency of a system is the major concern now-a-days. This chapter discusses the previous work related to the Design and Implementation of AES Encryption and Decryption process and the improvements made in the AES hardware implementation so as to improve power, area, efficiency, etc of the system [1].

Pipelined hardware implementation for the round keys can also be done in a parallel way while performing the encryption process. Parallel implementation helps in reducing the delay of each encryption round as well the delay of the input plain text [2]. The various steps involved in the encryption process and its implementation are validated on FPGA. The time for converting the plain text into cipher text was 200ns and device utilization is within 50% [3]. So as to achieve high throughput and a cost effective AES module, a new module was designed for the Key Expansion process which is known as 'on-the-fly' key expansion structure. The throughput achieved was 1.16Gbps with the cost of only 19476 which is equivalent to NAND2 gates [4].

Some AES applications require varible key size, so for such applications a novel architecture is proposed in the paper [5]. The proposed design integrates encryption/decryption key genera-

tion in one single module for different key sizes. The datapath for encryption and decryption is also integrated. Thus the circuit area gets optimized. Security of the data and its confidentiality plays an important role in Cryptography. Hence in [6] a design is proposed in which data is encrypted using AES and then uploaded on a cloud. The proposed model uses Short Message Service (SMS) alert mechanism for avoiding unauthorized access to user data. Even the security and compression of the encrypted text can be achieved by using Arithmetic Coding along with AES Algorithm which is discussed in [7]. The process is very simple, it encodes the data then performs the AES Encryption and then at the receiver's end it decodes the data. This process is carried out at the same time. With the help of Matlab, the data is encoded, encrypted, decrypted and decoded.

The implementation of the AES Algorithm can have different architectures namely, Pipelined, Parallel, Rolled, Unrolled, etc. Rolled Architecture is discussed in [8]. The keys are stretched only once and stored in a memory while the encryption process is carried out. With this architecture, low power consumption was achieved of about 22.85mW. In [9], an efficient algorithm for key pool generation by using Sudoku puzzle solving mechanism is being discussed. It creates a pool of key for individual user. This key pool is shared only to the authorized people. It chooses the keys randomly from the key pool while the encryption process is initiated. White-box implementation is discussed in [10]. The authors have designed a toolbox which is more secure and helpful for AES encryption process. Various mathematical Equations are illustrated in [10] so as to give the details of the tool box implementation. An eight stage Parallel processing method is used in SubByte transformation S-box and an eight stage parallel computation is applied in MixColumn transformation round [11]. The architecture of this implementation is studied in [11].

To aim real life applications, high speed and cost effective AES implementation is very much important. ASIC and FPGA are the two best platforms where the AES algorithm can verified and

validated efficiently. Memory modules such as Dual Port RAMs are used to store various transformations used in AES algorithm and also the clock plays a vital role in reducing the execution time for conversion of data to the encrypted one [12]. Throughput and area of 128, 192 and 256-bits AES have been measured in [13]. Results show that the key size is linearly increasing with the throughput where as it is exponentially increasing with the area of the system. Low Power Techniques can be studied in [14]. With a improved S-Box architecture, power optimization can be easily obtained in AES algorithm. Cryptographic Algorithms are more prone to attacks. Because of this, the original text which has to be transmitted to the receiver in encrypted format becomes insecure. Fault-resistant implementation of AES is of utmost importance. In [15] a new design is proposed that restricts the fault attacks on these cryptographic algorithms by verifying differential bytes of input and output in the encryption process and the key expansion process, respectively.

A new method is invented for performing the encryption process on an image and the details regarding the steps for the image to get converted to an encrypted image are being discussed in [16]. The speed of operation, efficiency, security and frequency of this new technique is also compared. Similarly, a pipelined implementation for the image encryption and decryption can be studied from [17]. This AES architecture increases the throughput of the system thereby reducing the latency and improving the security and data rate. In [18], a 'look-ahead' technique is proposed so as to improve the speed of operation of AES Key Generator Module due which the last round key can be available first. An efficient parallel architecture is designed in [19] for a crypto chip. It achieves a high throughput of 29.77 Gbps in encryption.

The Dual stage Architecture for AES algorithm is proposed in [20]. The power consumption and critical path delay using the proposed architecture gives high performance. Direct Optimized Routing (DOR) Scheme uses eleven clock cycles for encryption process whereas the Dual Stage Scheme takes just six clocks to perform the operation. In [21], terms and transformations related

to cryptography and encryption are examined and analyzed. AES processor to generate cryptographically secured information can be studied in [22]. The processor designed is resistant to all cryptanalytical attacks and thus keeps the information secured. It removes the mathematical equations by optimizing the AES algorithm. So far the various design implementations very discussed. Even the designed module needs to be tested and verified. Verification using SystemVerilog and UVM is more efficient compared to the traditional one as it has various add-on features in its verification environment. SystemVerilog describes the basic language constructs, features and use in detail. It includes several techniques and examples on how to build a basic layered test bench using Object Oriented Programming (OOP). SystemVerilog incorporates OOP, dynamic threads, and inter-process communication [23]. UVM testbench architecture and classes are inherited from other methodologies that have proven effective for verification of digital designs [24]. In [24], AES IP verification is carried out using UVM methodology. It is verified using automatic testcase generation. Thus better results can be gained through automatic testcase generation. AES Algorithm is designed and verified using SystemVerilog [25]. Even in [25], the authors have made a comparison between the hardware and software implementation of the AES Algorithm. The results proved in [25] shows that the hardware model is sixty times faster than the software model when processing the AES operation.

# Chapter 3

# **Block Cipher**

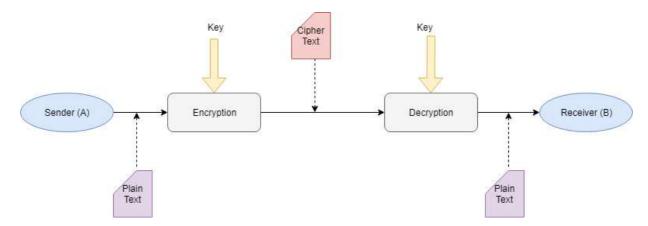

The Encryption process is carried out by taking a block of Plaintext bits and converting that into a block of Ciphetext bits using the Encryption Key. Both the blocks of plain text and ciphertext are of same size. Block length size is normally fixed. Block size does not directly affect the strength of encryption process. Cipher strength depends up on the key size. The Block Cipher Scheme can be seen in figure 3.1

#### 3.1 Block Size

Following points must be considered while selecting the block size.

- Prevent using smaller block size For example if the size of the block is n-bits, then the possible plain text combinations are going to be '2n'. 'Dictionary Attack' is initiated by the attacker when the attacker recognizes the plain text blocks respective to the cipher text blocks which were previously sent. The attacker builds a dictionary plain text and cipher text pairs by and send those pairs through encryption key.

- Larger block size must be ignored If the size of the blocks are larger enough, then the

Figure 3.1: Block Cipher Scheme

cipher is unproductive to manage. In such cases, plain texts must get padded before getting encrypted.

Multiples of 8 bit – As the data handling capacity of a CPU is a multiple of 8, the block size/length which are multiples of 8 are preferred as it becomes more convenient from implementation point of view.

### 3.2 Different Block Cipher Schemes

There is a vast number of block ciphers schemes that are in use. Many of them are publically known. Most popular and prominent block ciphers are listed below.

- Digital Encryption Standard (DES) It is a symmetric-key algorithm which is used for Encrytion. Now-a-days, DES is not widely used as its block cipher identified as broken due to small key length.

- Triple DES Triple DES is an advancement over DES algorithm. It is a symmetric-key algorithm and was also widely used once upon a time. Triple DES has three individual

keys with 56 bits each.

- Advanced Encryption Standard (AES) It is the most widely used Encryption standard today, and is more secured as compared to other block cipher schemes.

- RSA RSA is a public-key encryption algorithm. This scheme passes the encrypted data

to the web. For encrypting the data, it uses pair of keys and hence, it is termed as a

asymmetric algorithm.

- IDEA In this cipher scheme the block and key length are fixed. The block length is of 64 bits and the key length is 128 bits.

- Blowfish Blowfish cipher scheme was developed as a substitute for DES. It is also a symmetric scheme in which the original text gets divided into blocks of 64 bits by the cipher and the encryption is done independently.

- Blowfish is known for both its tremendous speed and overall effectiveness as many claim that it has never been defeated.

- Twofish In this cipher scheme the block size is of fixed length i.e, 128 bits and key length is of variable size. It is the advanced version of Blowfish Algorithm.

- Serpent The speed of encryption using this scheme is slower but it is more secure as compared to others. This scheme has a fixed block length of 128 bits and key sizes of 128, 192, and 256 bits respectively.

### 3.3 Block Cipher Padding

Blocks that have fixed length let's say 32-bits or 64-bits are operated by the block ciphers. Plain texts must not always be a multiple of the block length. If the size of the plain text is 128-bits

**15**

then two blocks of 64 bits are generated, so in this case block cipher padding is not required. But if the plain text length is of 160-bits, then two blocks of 64-bits are generated with the third block remaining with 32 bits. In this case, the third block will need padding and hence, the block will be padded up with unnecessary information which will be equal to the block size i.e, 64-bits. Adding redundant information to the block is known as 'Padding'. Padding makes the system inoperative and uncertain.

# **Chapter 4**

# **Advanced Encryption Standard**

#### 4.1 Overview

This chapter briefly discusses the Federal Information Processing Standards (FIPS-197) document which was passed by the National Institute of Standards and Technology (NIST). This document gives the details of the Advanced Encryption Standard (AES). All the mathematical equations related to the different AES transformations are being discussed in this chapter using the FIPS-197 document.

The AES is a subset of the Rijndael algorithm. The Rijndael algorithm is preferred as it gives better results with respect to security, performance, efficiency and simplicity. AES is a symmetric cipher algorithm. In such case, a single key is used for both encrypting and decrypting the data unlike the asymmetric ones in which there are two types of keys used namely, public and private key for encrypting and decrypting the data respectively[26].

This algorithm processes only on fixed size of the input blocks. It supports block length of 128 bits and cipher keys with lengths of 128, 192 or 256 bits for the encryption process. Rijndael scheme supported block lengths and cipher key lengths of different sizes but the NIST did

Table 4.1: AES Variations

| AES Version | Key Length (Nk words) | Block Size (Nb words) | No of Rounds (Nr rounds) |

|-------------|-----------------------|-----------------------|--------------------------|

| AES-128     | 4                     | 4                     | 10                       |

| AES-192     | 6                     | 4                     | 12                       |

| AES-256     | 8                     | 4                     | 14                       |

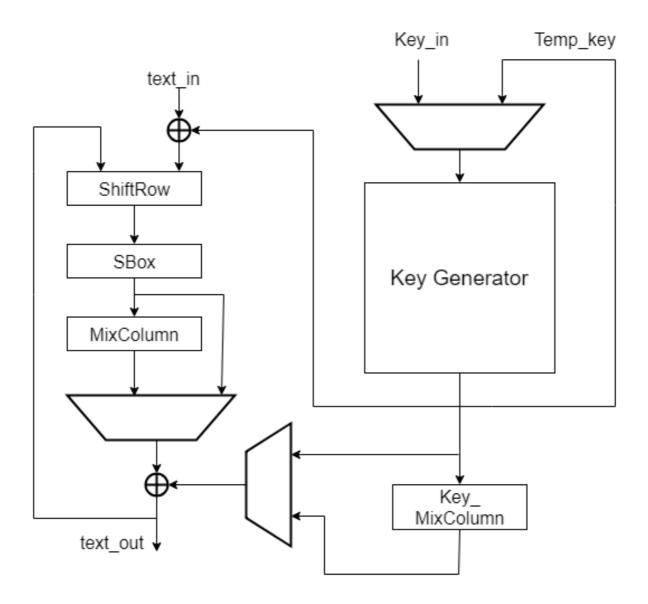

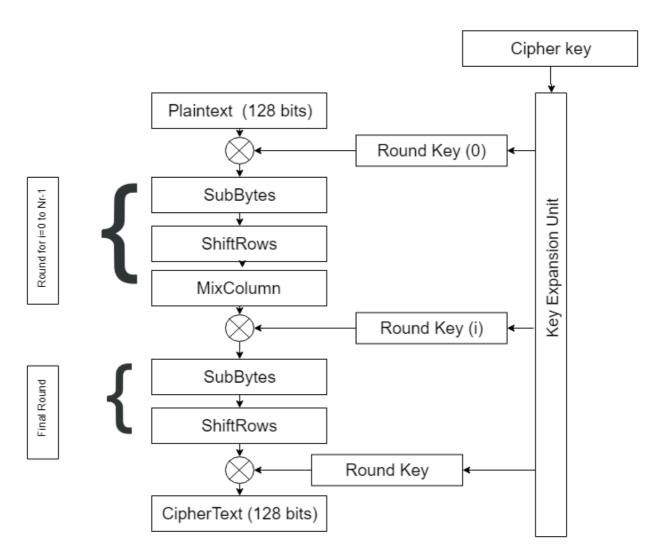

not allow the features in AES algorithm[26]. The AES architecture is shown in figure 4.1

### 4.2 Inputs, Outputs and the State

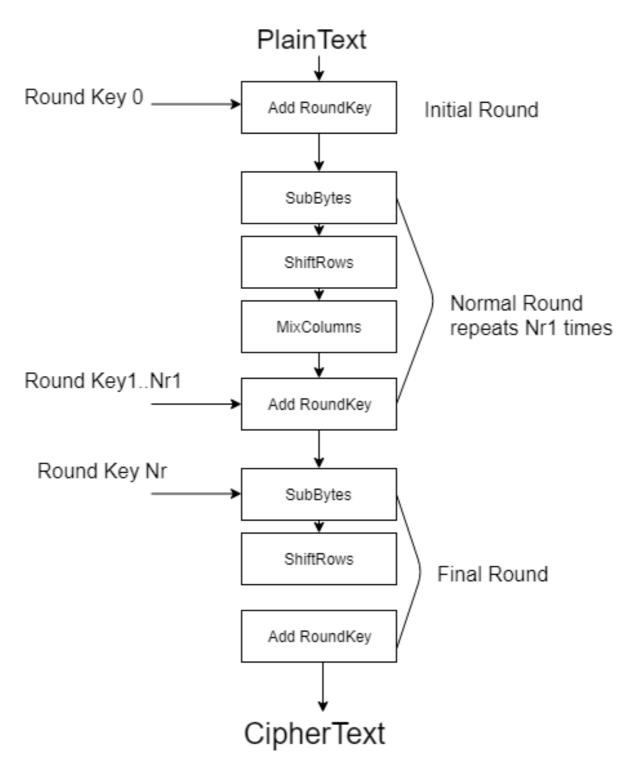

AES algorithm have blocks of 128 bits of input plain text and output ciphertext. It has cipher key input is a series of 128, 192 or 256 bits. In other words the length of the cipher key, Nk, is either 4, 6 or 8 words which represent the number of columns in the cipher key[26]. The AES algorithm is classified into three versions based on the cipher key length. The number of rounds of encryption depends on the cipher key size[26]. The AES Encryption process is illustrated in the figure 4.2

The AES versions varying with key length, block size and number of rounds is tabulated in 4.1.

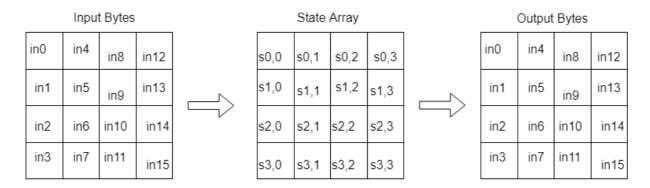

A byte is capable of handling the operation of the AES algorithm. Therefore, the plain text, ciphertext and the cipher key are ordered and processed as arrays of bytes. For an input, an output or a cipher key is denoted by a, the bytes in the following array are referenced as  $a_n$ , where n ranges as follows depending on the block length and key length[26]:

- Block length = 128 bits,  $0 \le n \le 16$

- Key length = 128 bits,  $0 \le n \le 16$

- Key length = 192 bits,  $0 \le n \le 24$

- Key length = 256 bits,  $0 \le n \le 24$

Figure 4.1: AES Architecture

Figure 4.2: AES Encryption Process

Figure 4.3: State Population and Results

The respresentation of the byte values is done by concatenating their individual bit values between braces in the order {b7, b6, b5, b4, b3, b2, b1, b0}. These bytes are considered as finite field elements using a polynomial representation[26]:

$$b_7x^7 + b_6x^6 + b_5x^5 + b_4x^4 + b_3x^3 + b_2x^2 + b_1x^1 + b_0x = \sum b_ix^i$$

; where i ranges from 0 to 7 For example, {10001001} (or {85} in hexadecimal) identifies the polynomial  $x^7 + x^3 + 1$ [26].

Two dimensional array of 4x4 bytes are used for processing the AES algorithm. This two dimensional array is called as State, and any individual byte within the State is referred to as  $s_{r,c}$  where letter 'r' represent the row and letter 'c' denotes the column. The state is filled with the plain text at the start of the encryption process. Then the cipher performs a set of substitutions and permutations on the State[26]. After the cipher operations are processed on the State, the final value of the state is replicated to the ciphertext output as shown in the following figure 4.3.

The input array is replicated into the State at the start of the cipher, according the following scheme[26]:

$$s[r,c] = in[r+4c] for 0 \le r < 4 and 0 \le c < 4,$$

and at the end of the cipher the State is replicated into the output array as shown below[26]:

$$out[r+4c] = s[r,c] \ for \ 0 \le r < 4 \ and \ 0 \le c < 4$$

### 4.3 Cipher Transformation

Either the individual bytes of the State or an entire row/column is operated by the Cipher key. At the beginning of the cipher, the input is replicated into the State as discussed in Section 4.2. Then, an initial Round Key addition is performed on the State. Round keys are generated from the cipher key with the help of the Key Expansion module. The key expansion module produces a series of round keys for each round of transformations that are performed on the State[26].

The different transformations performed on the state are same for all the AES versions but the number of the rounds are different depending on the cipher key length. The final round in all AES versions performs one less transformation on the State and hence it is slightly different from the first Nr -1 rounds. Each round of AES cipher except the final round consists of all the following transformation[26]:

- SubBytes()

- ShiftRows()

- MixColumns()

- AddRoundKey()

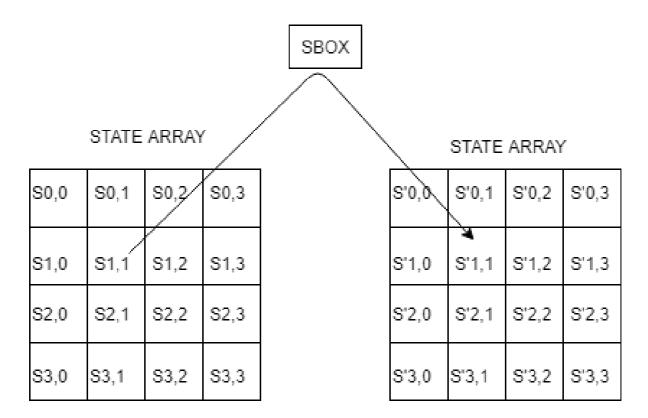

#### 4.3.1 SubBytes () Transformation

The 16 input bytes are substituted with the help of a S-Box table for a given design. The resultant is a matrix consiting of four rows and four columns. SubBytes Transformation is shown in figure 4.4.

Figure 4.4: SubBytes Transformation

Figure 4.5: ShiftRows Transformation

#### 4.3.2 ShiftRows () Transformation

Each of the four rows of the matrix is shifted to the left. If there are any missing entries, then they are re-inserted on the right side of row. Shift is carried out as follows –

- First row is not shifted.

- Second row is shifted one position to the left.

- Third row is shifted two positions to the left.

- Fourth row is shifted three positions to the left.

- The resultant is a new matrix consisting of the same 16 bytes but shifted with respect to each other.

The ShiftRows transformation is shown in figure 4.5

$$R = MC(SR(SB\ (State))) = \begin{bmatrix} `02' & `03' & `01' & `01' \\ `01' & `02' & `03' & `01' \\ `01' & `01' & `02' & `03' \\ `03' & `01' & `01' & `02' \end{bmatrix} \otimes \begin{bmatrix} SB(d_{15}) & SB(d_{11}) & SB(d_{7}) & SB(d_{3}) \\ SB(d_{10}) & SB(d_{6}) & SB(d_{2}) & SB(d_{14}) \\ SB(d_{5}) & SB(d_{1}) & SB(d_{13}) & SB(d_{9}) \\ SB(d_{0}) & SB(d_{12}) & SB(d_{8}) & SB(d_{4}) \end{bmatrix}$$

Figure 4.6: Matrix Multiplication Representation

#### 4.3.3 MixColumns () Transformation

State Columns are operated by the Mix Column transformation. Each column is equivalent to a finite field GF ( $2^8$ ). Every column is multiplied by modulo  $x^4+1$  with a fixed four-term polynomial  $a(x) = \{03\}x^3 + \{01\}x^2 + \{01\}x + \{02\}$  over the GF( $2^8$ )[26]. The MixColumns transformation can be expressed as a matrix multiplication as shown below in figure 4.6:

The MixColumns transformation is shown in figure 4.7.

Each column of four bytes is now transformed using a special mathematical function as mentioned above.

### 4.3.4 AddRoundKey ( ) Transformation

The round key values are added to the State by simply using the XOR operation in the AddRoundKey transformation[26]. The Key Expansion module generates blocks of Nb words which is present in every round key. The round key values are added to the columns of the state in the following way[26]:

$$[s'_{0,c}, s'_{1,c}, s'_{2,c}, s'_{3,c},] = [s_{0,c}, s_{1,c}, s_{2,c}, s_{3,c}] \oplus [W_{round+Nb+c}] \text{ for } 0 \le c \le Nb$$

The 16 bytes of the matrix are now considered as 128 bits and are XORed to the 128 bits of the round key. If this is the last round then the output is the ciphertext. Otherwise, the resulting 128 bits are interpreted as 16 bytes and we begin another similar round. AddRoundKey Transformation is shown in figure 4.4.

Figure 4.7: MixColumn Transformations

Figure 4.8: AddRoundKey Transformation

#### 4.4 AES Key Expansion

Every encryption round required four words of round keys. Thus in all 4\*(Nr + 1) round keys are considered for the first AddRoundKey transformation. All the round keys are obtained from the cipher key itself[26].

There is no limitation on the cipher key selection as per the FIPS-197 document. The Key Expansion module expands the cipher key into the round keys. The SubWord() function is same as the SubByte transformation as it uses the S-Box to substitute each of the four bytes in a word[26]. The RotWord() function takes a word [a0,a1,a2,a3] as input and perform a cyclic shift and returns the word [a1,a2,a3,a0][26]. The round constant word array, Rcon[i], contains a 32 bit value given by  $[\{02\}^{i-1},\{00\},\{00\},\{00\}]$  [26]. The KeyExpansion module for the AES256 where Nk=8 is slightly different as an additional SubWord function is applied to the previous round key, w[i-1], prior to the XOR with w[i- Nk][26].

# **Chapter 5**

# **Block Cipher Modes of Operation**

Block cipher modes of operation permits the ciphers to encrypt the large blocks of data. It is a setup method in which the data gets encrypted and even it does not have to adjust with the security issues. Same key (shared key) is used for encrypting as well decrypting the data. Usage of same key is not actually advisable but using an algorithm for uniform data inputs, uniform ciphertext results can be obtained at the output.

Usage of shared key can help the attacker by getting the information regarding the segregation of texts due to which the attacker can able to crack the cipher and retrieve the original text. To avoid such situation, one can manipulate the ciphertext ouptut. This achieved by combining the plain text with respective ciphertexts and the resultant is used as the input cipher for the next blocks. Thus same blocks of ciphertexts are ignored from getting generated from same input plain texts. This methodology is known as Block Cipher Modes of Operation. Different types of Block Cipher Modes of Operation are discussed below in detail.

Figure 5.1: Encryption using ECB mode

## **5.1** ECB (Electronic Codebook) Mode

In this mode of operation, encryption is done by processing the plain texts individually. Even the decryption process is carried out in the same way. Hence, it is feasible to encrypt many threads at the same time. The ciphertext is not hazy in this mode and hence the message is not considered to be secured as it can get easily cracked[27]. ECB is the most easy mode of operation. Encryption process using ECB is shown in figure 5.1

The encrypted text must be equal to the multiple of single block size. Hence, sometimes the texts are stretched by adding extra one bit to it and by padding zeros to the rest of the block. The ECB mode ciphers are more susceptible to attacks.

### 5.2 CBC (Cipher-Block Chaining) Mode

In this mode, the encryption process is carried out by XORing the plain text and the initialization vector and with the help of encryption algorithm, ciphertext is generated. This ciphertext is fed as an input to the next block of encryption. Hence, every succeeding ciphertext block depends on the previous one. The initialization vector is of the same size as that of the plain text. This mode came into operation in the year 1976[27].

Figure 5.2: Encryption using CBC mode

Only one thread can be processed at a time during encryption. This mode is used in many applications. Encryption process using CBC is shown in figure 5.2

# 5.3 PCBC (Propagating or Plaintext Cipher-Block Chaining)Mode

PCBC mode is same as the CBC mode. Before performing the encryption process, this mode combines the bits from the previous and the present plain text blocks. If one output ciphertext is impaired, then the next plain text block and all the other following blocks will get impaired. Due to this the ciphertext will not get decrypted properly.

In this mode also only one thread can be processed at a time during encryption. Encryption process using PCBC is shown in figure 5.3

Figure 5.3: Encryption using PCBC mode

### 5.4 CFB (Cipher Feedback) Mode

The CFB mode is identical to the CBC mode. In this mode encryption is done taking the ciphertext data from the previous cycle and then feed the output to the plain text block. This mode is not vulnerable to attacks. Same encryption algorithm is used at the receiving end for decrypting the data.

If one output ciphertext is impaired, then the next plain text block and all the other following blocks will get impaired. Due to this the ciphertext will not get decrypted properly. Only one thread can be processed at a time during encryption[27]. Encryption process using CFB mode is shown in figure 5.4

## 5.5 OFB (Output Feedback) Mode

Output Feedback mode creates random bits (keystream bits) for encrypting the data. As the random bits are generated, the operation of block cipher is identical to the operation of stream cipher. As the random bits of data is generated continuously, single thread processing can be

Figure 5.4: Encryption using CFB mode

only done during encryption.

The disadvantage of OFB mode is that it continuously encrypts the initialization vector due to which the plain text will not get encrypted properly[27]. Encryption process using OFB mode is shown in figure 5.5

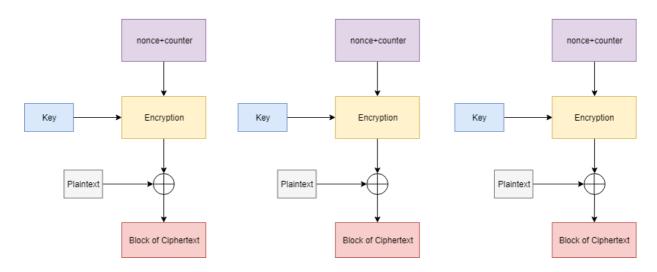

## 5.6 CTR (Counter) Mode

CTR mode also creates random bits (keystream bits) for encrypting the data like the OFB mode. As the random bits are generated, the operation of block cipher is identical to the operation of stream cipher. 'nonce' means the number which is distinct. The values from the counter are combined with the nonce which gives the encrypted text as output. The nonce is equivalent to initialization vectors used in the previous modes.

Multiple threads can be processed simultaneously. It is the most widely used block cipher mode[27]. The CTR mode is also known as the Segment Integer Counter mode (SIC).

Figure 5.5: Encryption using OFB mode

Figure 5.6: Encryption using CTR mode

# Chapter 6

# **Design and Test Methodology**

The Advanced Encryption Standard is introduced to secure the electronic data. The AES-256 pipelined cipher module uses AES algorithm which is a symmetric block cipher to encrypt the plain text data. Encryption converts data to an unintelligible form called ciphertext. Encryption is performed using 256 bits of cryptographic keys. The hardware module is pipelined specially so as to perform the round transformation. As it is a pipelined design, power optimization can be achieved and high throughput can also be gained This module is optimized for speed as it pipeline hardware to perform repeated sequence called round. The pipelined Cipher is shown in figure 6.1

#### **6.1** Design Implementation

- The Design for Test (DUT) is designed by using one clock, asynchronous reset, inputs valid signal, outputs valid signal.

- Sub Bytes: As discussed earlier, it uses SBox Look-up Table (LUT) to substitute every byte in the 128 bit plain text data.

- Shift Rows: This module is used to arrange data in the state array and shifting rows of this array.

- Mix Columns: This Module is used to perform Mix Columns Transformation as explained in the chapter four.

- Add Round Key: This module is used for xoring input data and round key generated from the key expansion module.

- Round: This module connects SubBytes-ShiftRows-MixColumns- AddRoundKey modules

- Round Key Gen: This module is used to handle the operation of round key generation from input. The key generation stages must be balanced with the 4 round stages (SuBytes-ShiftRows-MixColumns- AddRoundKey) in order to let the round key and the data meet at the AddRound Key module Round key generation includes RotWord, SubBytes, Xor operations using RCON which are specified in the FIPS 197 document.

- Key Expansion: The key Expansion Module is used to generate round key from cipher key using Pipelined architecture. For AES-256, number of rounds required is fourteen, so fourteen round key generation module will be instantiated.

- Top Pipelined Cipher: It is the top module of the design which forms rounds and connects Key Expansion module using the pipelined architecture. It instantiates Key Expansion module which will provide every round with round key as per the discussed algorithm. First cipher key will be xored with plain text and then by instantiating all rounds. After that, connect them with key expansion module, this is the final round and it does not contain mixcolumns as per the FIPS 197 document. As the final round has only three stages a delay register should be introduced to get balanced with key expansion module.

Figure 6.1: Pipelined Cipher

•

## 6.2 Test Methodology

The Universal Verification Methodology (UVM) is the widely used in today's era for the verification of VLSI circuits. The UVM class library helps in implementing the layered testbench architecture. All the components of the UVM testbench are obtained from an existing UVM class.

UVM has different simulation phases that are arranged in terms of steps of execution. They are implemented in testbench as methods. The important UVM phases are:

- build\_phase- This method is used for creating and configuring the testbench.

- connect\_phase- the different sub components in a class are combined using the connect\_phase method.

- run\_phase- Simulation is carried out using this method.

- report\_phase- The results that are generated from the simulation are displayed using this method.

UVM macros are used to execute some methods inside the UVM classes and variables. Those macros are discussed as follows:

- uvm\_component\_utils: A new class type is filed when registers a new class type when the class derives from the class uvm\_component.

- uvm\_object\_utils: It is same as the uvm\_component\_utils, but the class is obtained from the class uvm\_object.

Figure 6.2: UVM Testbench

- uvm\_field\_int: The different functions like copy(), compare() and print() can be used using this macro.