#### **Rochester Institute of Technology**

### **RIT Digital Institutional Repository**

**Theses**

12-2017

### Configurable Random Instruction Generator for RISC Processors

Krunal Mange kxm3978@rit.edu

Follow this and additional works at: https://repository.rit.edu/theses

#### **Recommended Citation**

Mange, Krunal, "Configurable Random Instruction Generator for RISC Processors" (2017). Thesis. Rochester Institute of Technology. Accessed from

This Master's Project is brought to you for free and open access by the RIT Libraries. For more information, please contact repository@rit.edu.

#### CONFIGURABLE RANDOM INSTRUCTION GENERATOR FOR RISC PROCESSORS

by

#### Krunal Mange

GRADUATE PAPER

Submitted in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE in Electrical Engineering

| Approved by:                                                                                               |

|------------------------------------------------------------------------------------------------------------|

|                                                                                                            |

| Mr. Mark A. Indovina, Lecturer                                                                             |

| Graduate Research Advisor, Department of Electrical and Microelectronic Engineering                        |

| Dr. Sohail A. Dianat, Professor                                                                            |

| Dr. Sohail A. Dianat, Professor  Department Head, Department of Electrical and Microelectronic Engineering |

DEPARTMENT OF ELECTRICAL AND MICROELECTRONIC ENGINEERING

KATE GLEASON COLLEGE OF ENGINEERING

ROCHESTER INSTITUTE OF TECHNOLOGY

ROCHESTER, NEW YORK

DECEMBER 2017

### **Declaration**

I hereby declare that except where specific reference is made to the work of others, that all content of this Graduate Paper are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other University. This Graduate Project is the result of my own work and includes nothing which is the outcome of work done in collaboration, except where specifically indicated in the text.

Krunal Mange

Dec, 2017

### Acknowledgements

I would like to thank my advisor, Professor Mark Indovina, for his support, guidance, feedback, and encouragement which helped in the successful completion of my graduate research. Special thanks to my colleagues Namratha Pashupathy Manjula Devi and Thiago Pinheiro Felix da Silva e Lima for their work, corrections, comments and their active participation in this work. Finally, thanks to Dr. Dorin Patru for providing access to student implementations of the various RISC processors discussed in this paper.

#### **Abstract**

Processors have evolved and grown more complex to serve enormous computational needs. Even though modern-day processors share same dna with processors half century ago, verifying them today is the huge wall to scale. Verification dominates production cycle even with advances both in software (programming as well as CAD tools) and manufacturing (fabrication) as there are too many test scenarios to cover. Testing complex devices like processors with manual-testing alone in certainty missing the dead lines. Automatic verification is a great way to overcome hurdles of manual testing viz. speed, manpower, and ultimately cost. The work described in this paper targets verification of processors which have in-order instruction execution. Verification is done using SystemVerilog testbench which compares output of device under test to the output of SystemC model, when random instructions are applied.

# **Contents**

| Co | ontent           | ts                           | V   |

|----|------------------|------------------------------|-----|

| Li | st of I          | Figures                      | ix  |

| Li | List of Tables x |                              |     |

| Fo | rwar             | <b>d</b>                     | xvi |

| 1  | Intr             | oduction                     | 1   |

|    | 1.1              | Research Goals               | 2   |

|    | 1.2              | Contributions                | 2   |

|    | 1.3              | Organization                 | 3   |

| 2  | Bibl             | iographical Research         | 5   |

| 3  | Test             | Environment                  | 9   |

|    | 3.1              | Random Instruction Generator | 11  |

|    | 3.2              | Model                        | 12  |

|    | 3.3              | Test-bench                   | 12  |

|    | 3 4              | Report Database Generator    | 13  |

Contents vi

| 4 | Proc | cessor Architecture                   | 14 |

|---|------|---------------------------------------|----|

|   | 4.1  | Overview                              | 14 |

|   | 4.2  | Registers                             | 16 |

|   | 4.3  | Arithmetic & Logic Unit (ALU)         | 16 |

|   | 4.4  | Memory Unit                           | 17 |

|   | 4.5  | Instruction Set                       | 18 |

|   |      | 4.5.1 Manipulation Instructions       | 20 |

|   |      | 4.5.2 Data Transfer Instructions      | 20 |

|   |      | 4.5.3 Branch Instructions             | 21 |

|   | 4.6  | Processor Operation                   | 22 |

|   |      | 4.6.1 Pipeline Theory                 | 23 |

| 5 | Con  | figuration File                       | 27 |

| 6 | Ran  | dom Instruction Generator             | 31 |

|   | 6.1  | Random Instruction Generator Overview | 31 |

|   | 6.2  | 'extract' Function                    | 34 |

|   | 6.3  | 'memory_set' Function                 | 35 |

|   | 6.4  | 'filler' Function                     | 36 |

|   | 6.5  | 'gen' Function                        | 36 |

|   |      | 6.5.1 'manipulation_gen' Function     | 38 |

|   |      | 6.5.2 'data_transfer' Function        | 39 |

|   |      | 6.5.3 'branch' Function               | 40 |

|   | 6.6  | 'write_out' Function                  | 41 |

|   | 6.7  | 'reg out' Function                    | 42 |

| 7  | Resu  | ults                       | 43  |

|----|-------|----------------------------|-----|

|    | 7.1   | Mode 'a'                   | 45  |

|    |       | 7.1.1 Mode 'a' - Test T1   | 46  |

|    |       | 7.1.2 Mode 'a' - Test T2   | 46  |

|    | 7.2   | Mode 'm'                   | 46  |

|    |       | 7.2.1 Mode 'm' - Test T1   | 48  |

|    |       | 7.2.2 Mode 'm' - Test T2   | 48  |

|    | 7.3   | Mode 'mb'                  | 50  |

|    |       | 7.3.1 Mode 'mb' - Test T1  | 52  |

|    |       | 7.3.2 Mode 'mb' - Test T2  | 52  |

|    | 7.4   | Mode 'md'                  | 54  |

|    |       | 7.4.1 Mode 'md' - Test T1  | 54  |

|    |       | 7.4.2 Mode 'md' - Test T2  | 56  |

| 8  | Cone  | clusion                    | 64  |

|    | 8.1   | Future work                | 64  |

| Re | feren | aces                       | 66  |

| I  | RIS   | C Processor Instructions   | I-1 |

|    | I.1   | Manipulation Instructions  | I-1 |

|    | I.2   | Data Transfer Instructions | I-6 |

|    | I.3   | Branch Instructions        | I-9 |

| II | Conf  | figuration File I          | I-1 |

| Ш  | Sour  | rce Code                   | I-1 |

|    | III.1 | Random Instruction Generator | III-1       |

|----|-------|------------------------------|-------------|

|    | III.2 | Extract function             | III-48      |

| IV | Matl  | ab Source Code               | IV-1        |

|    | IV.1  | Errors for tests-Graph1      | IV-1        |

|    | IV.2  | Total Error count-Graph2     | IV-2        |

| V  | Simu  | ulation graphs               | V-1         |

|    | V.1   | Processor axt                | <b>V</b> -1 |

|    | V.2   | Processor dnm                | V-17        |

|    | V.3   | Processor <i>nxp</i>         | V-33        |

|    | V.4   | Processor tfl                | V-49        |

|    | V.5   | Processor sxs                | V-65        |

|    | V.6   | Processor vxk                | V-81        |

# **List of Figures**

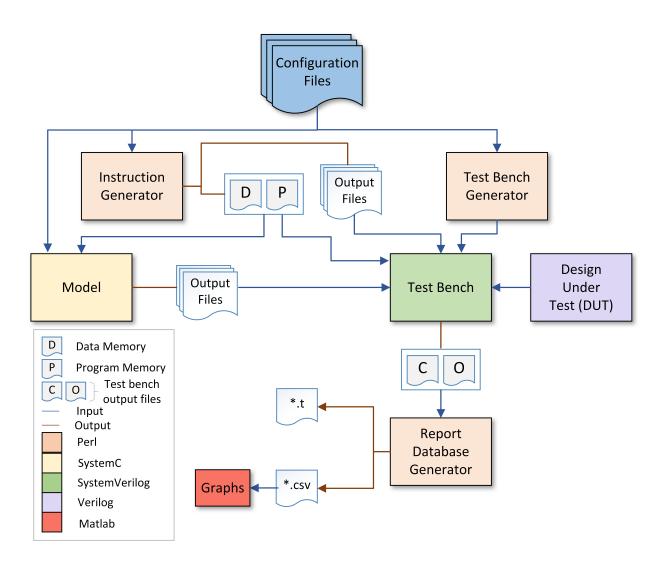

| 3.1 | System Block Diagram                                                             | 10 |

|-----|----------------------------------------------------------------------------------|----|

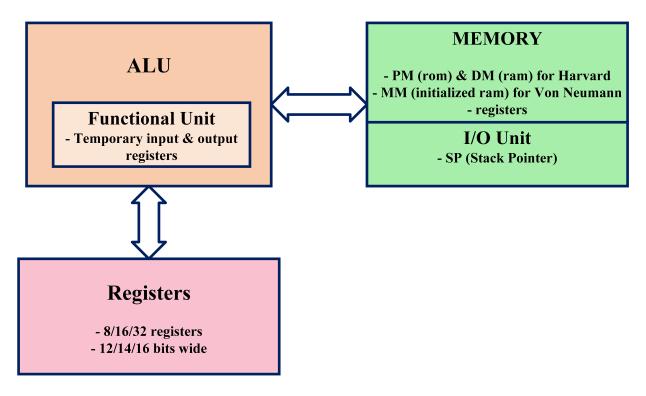

| 4.1 | Processor Architecture Overview                                                  | 15 |

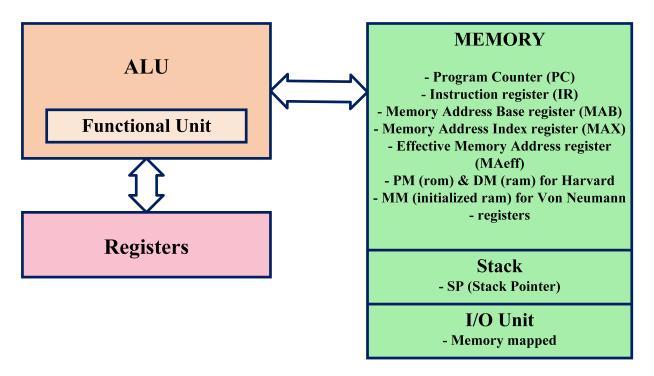

| 4.2 | Memory organization                                                              | 18 |

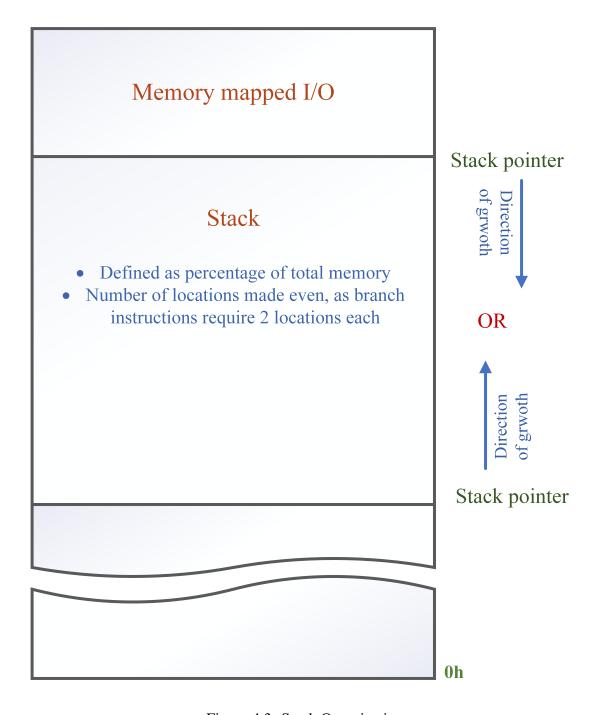

| 4.3 | Stack Organization                                                               | 19 |

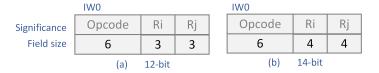

| 4.4 | Instruction word format for manipulation instructions (a) 12-bit and (b) 14-bit  |    |

|     | processor [1]                                                                    | 20 |

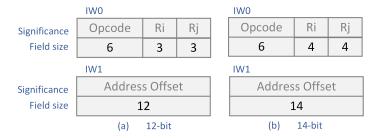

| 4.5 | Instruction word format for data transfer instructions (a) 12-bit and (b) 14-bit |    |

|     | processor [1]                                                                    | 21 |

| 4.6 | Instruction word format for JUMP and CALL (a) 12-bit and (b) 14-bit processor    |    |

|     | [1]                                                                              | 22 |

| 4.7 | Instruction word format for RET (a) 12-bit and (b) 14-bit processor [1]          | 22 |

| 4.8 | Sample example for pipeline                                                      | 25 |

| 4.9 | Pipeline stages                                                                  | 26 |

| 6.1 | Command to generate random instructions                                          | 27 |

| 0.1 | Command to generate random instructions                                          | 32 |

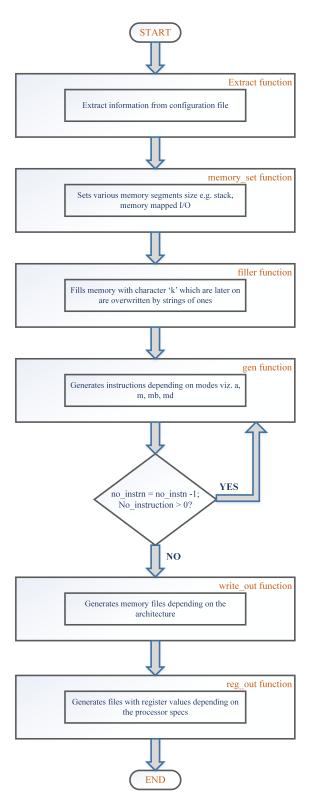

| 6.2 | Flowchart for instruction generator                                              | 33 |

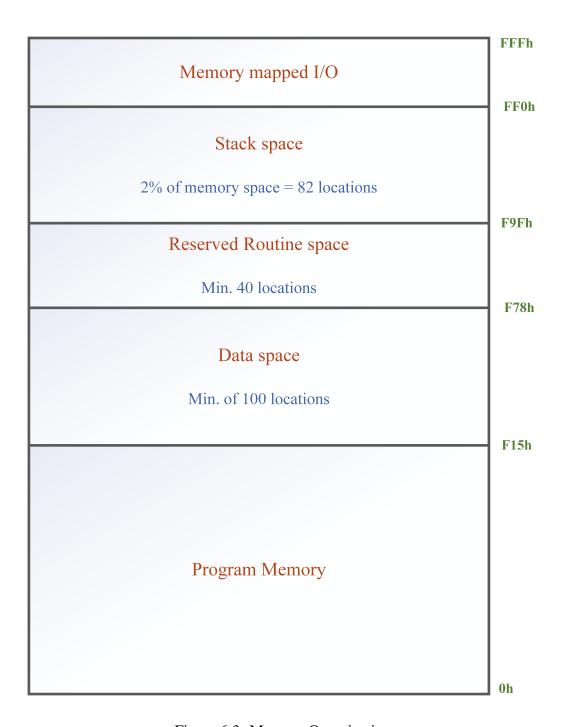

| 6.3 | Memory Organization                                                              | 37 |

List of Figures

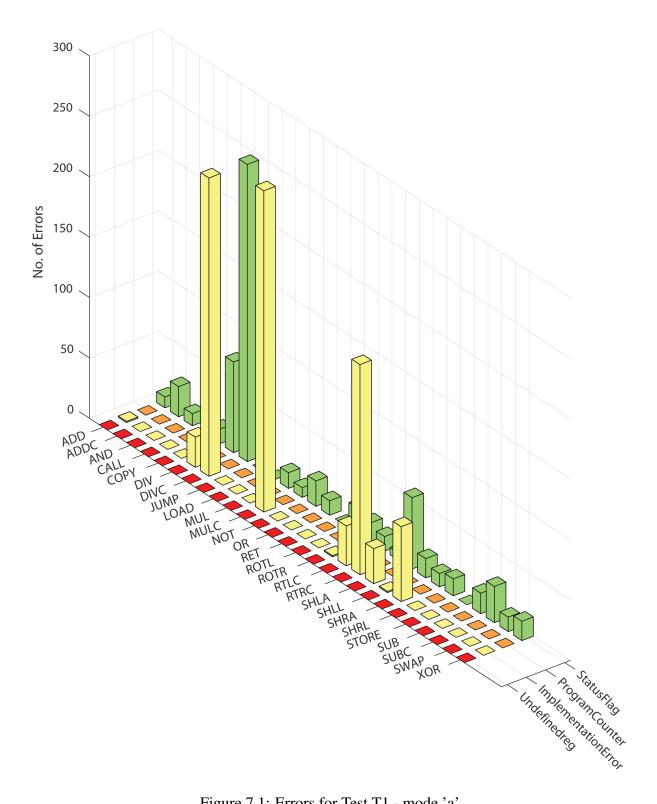

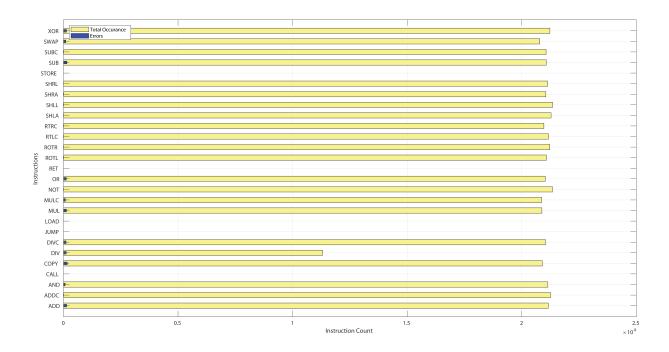

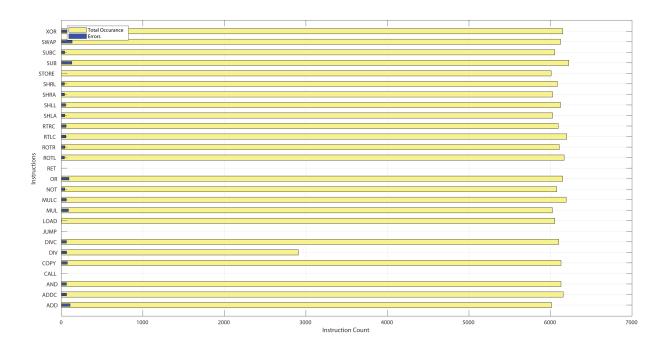

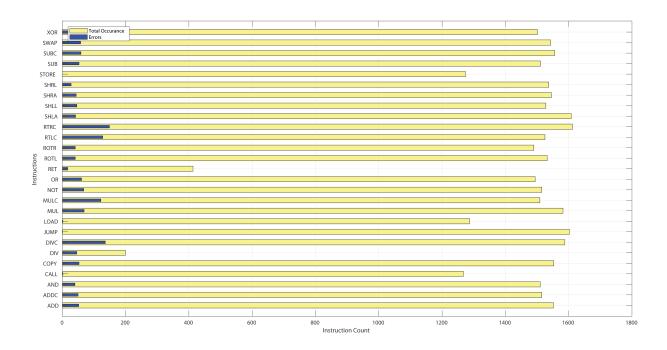

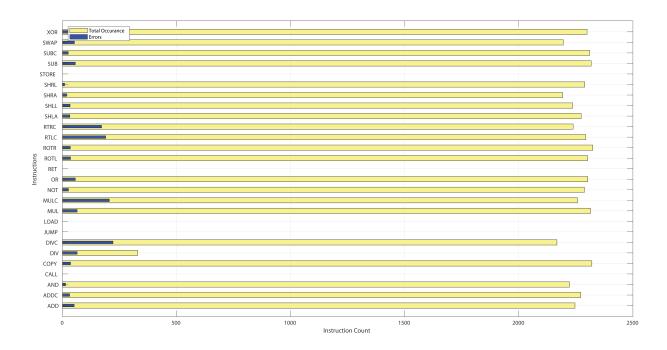

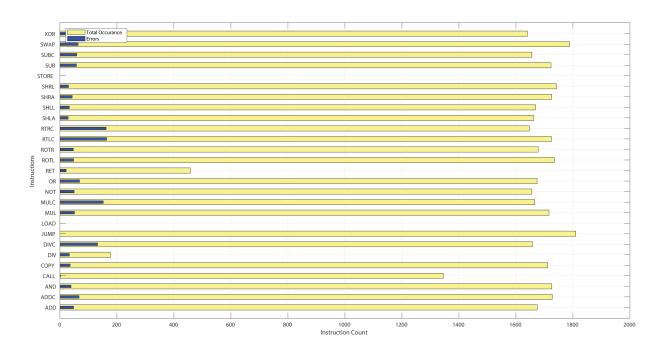

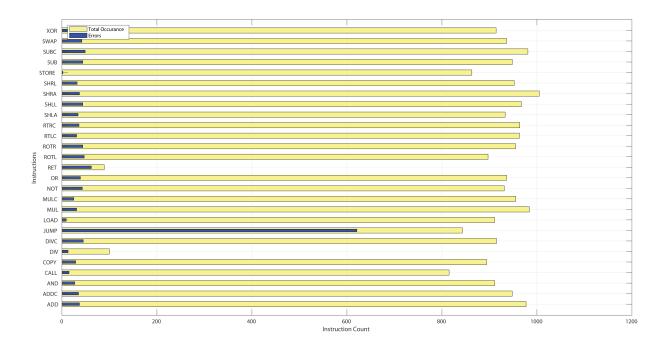

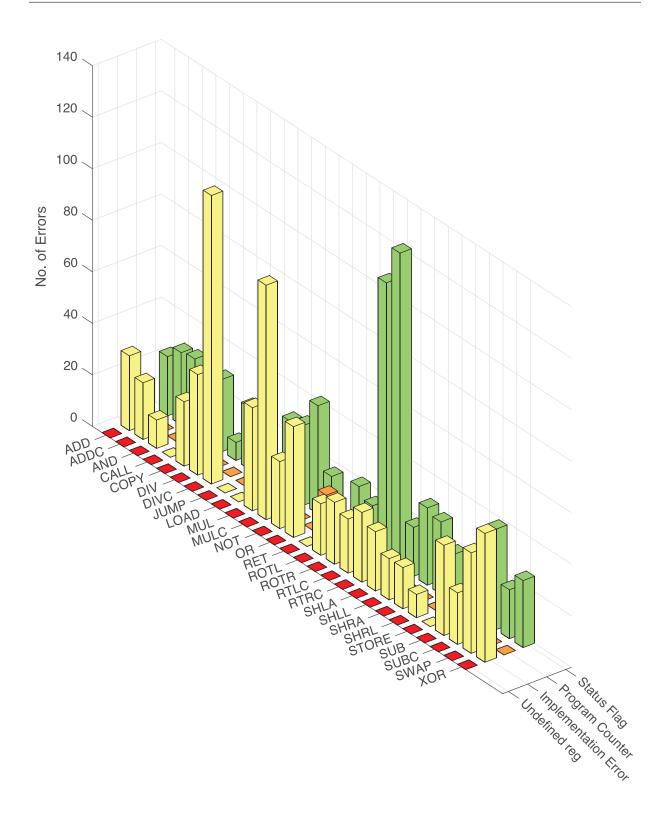

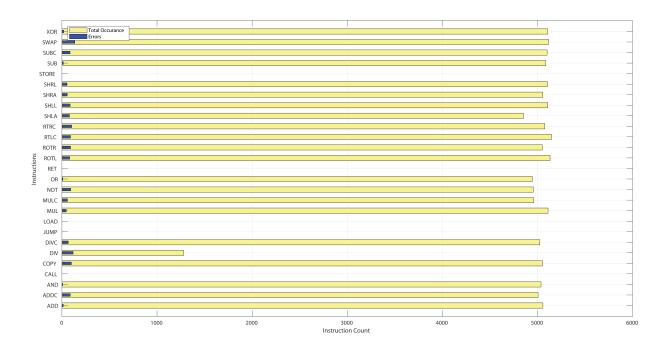

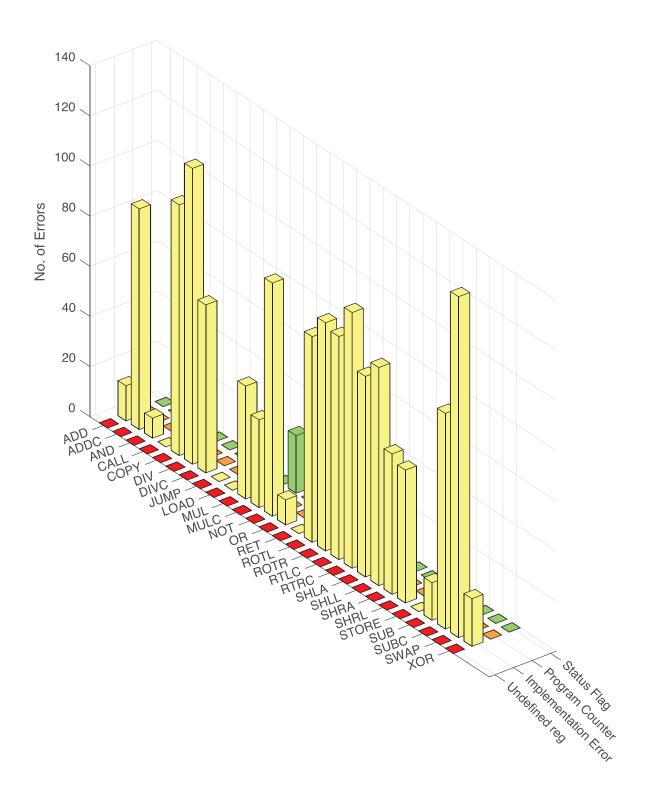

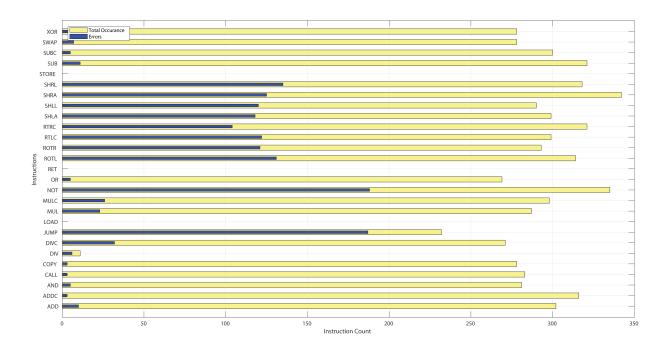

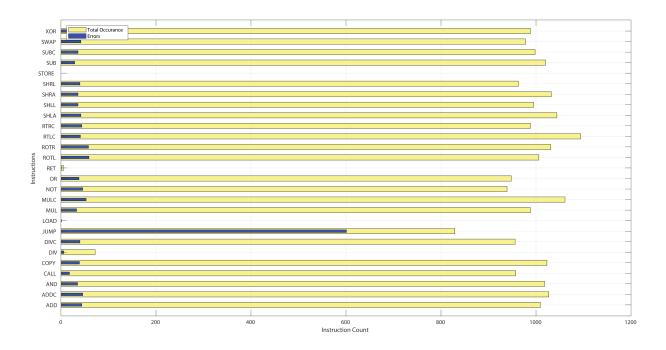

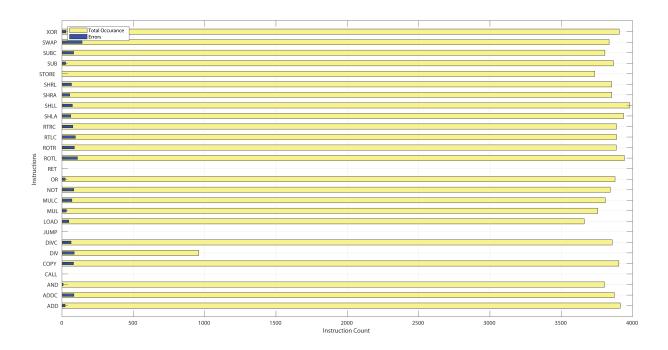

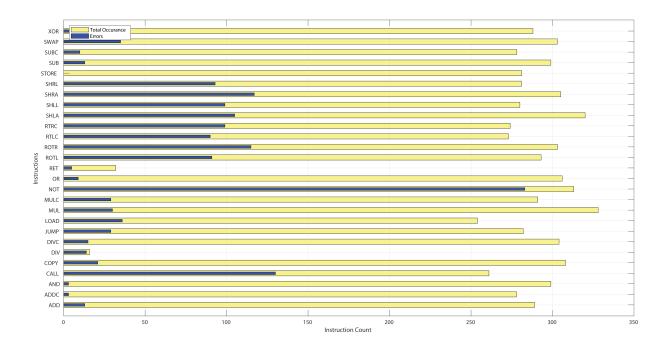

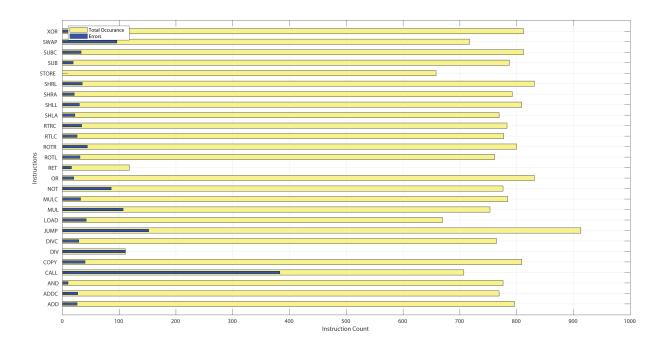

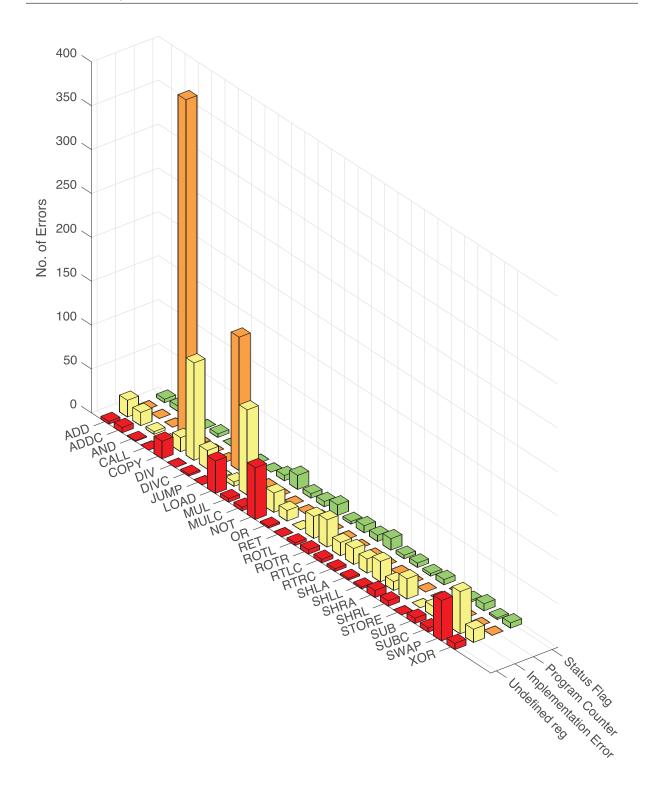

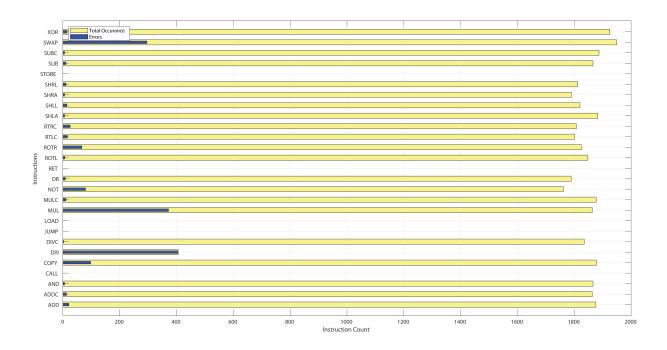

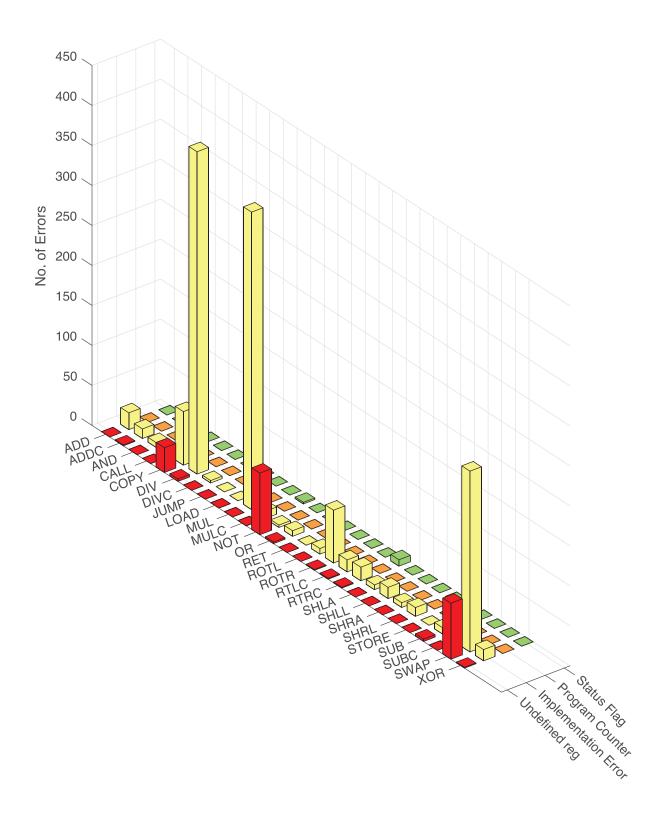

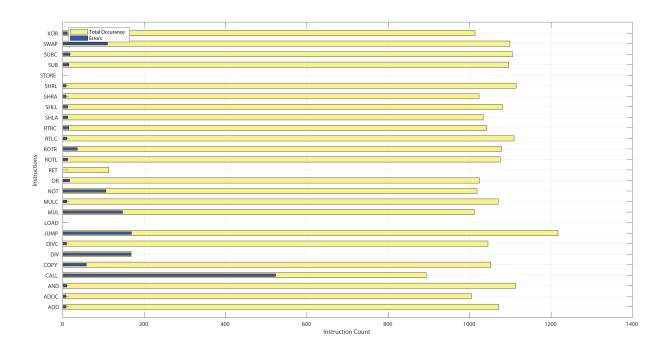

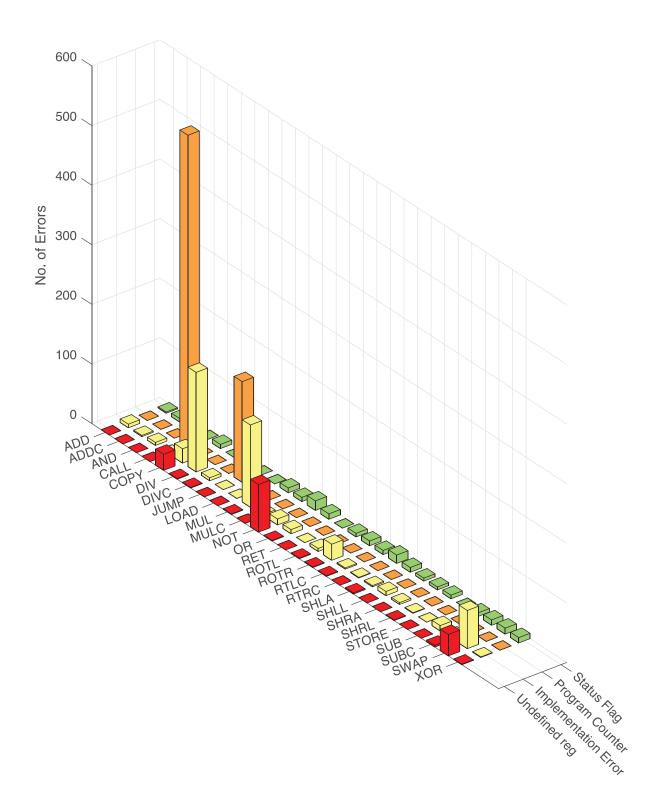

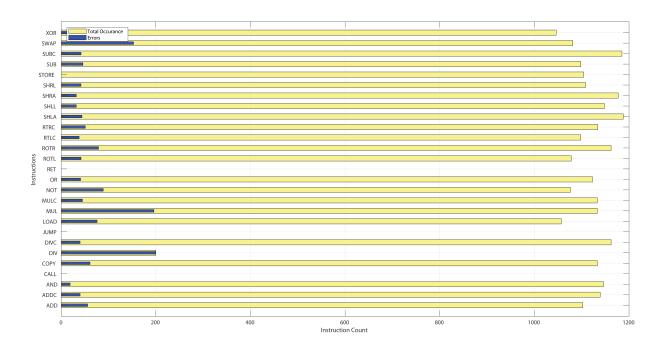

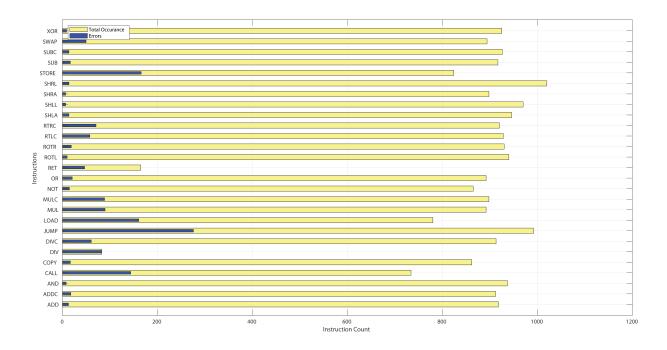

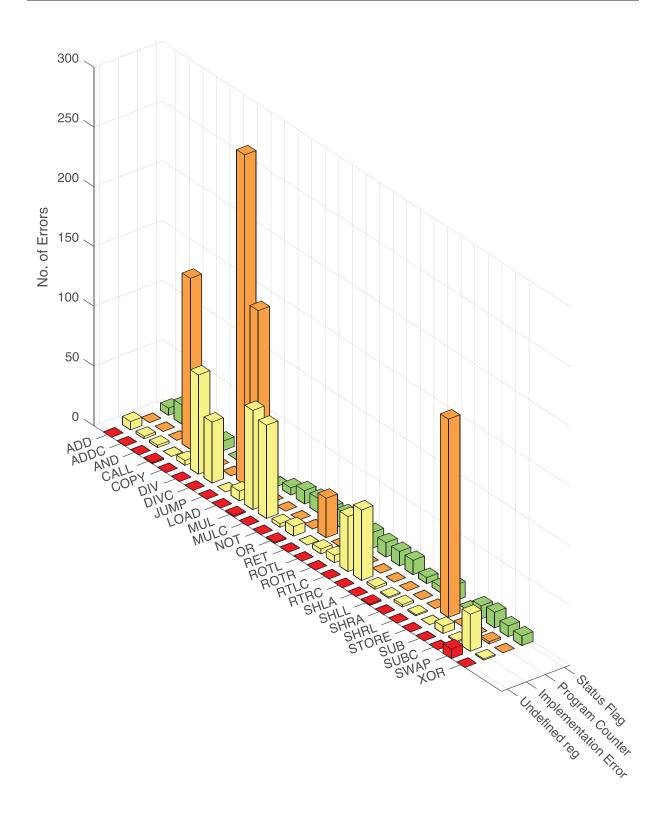

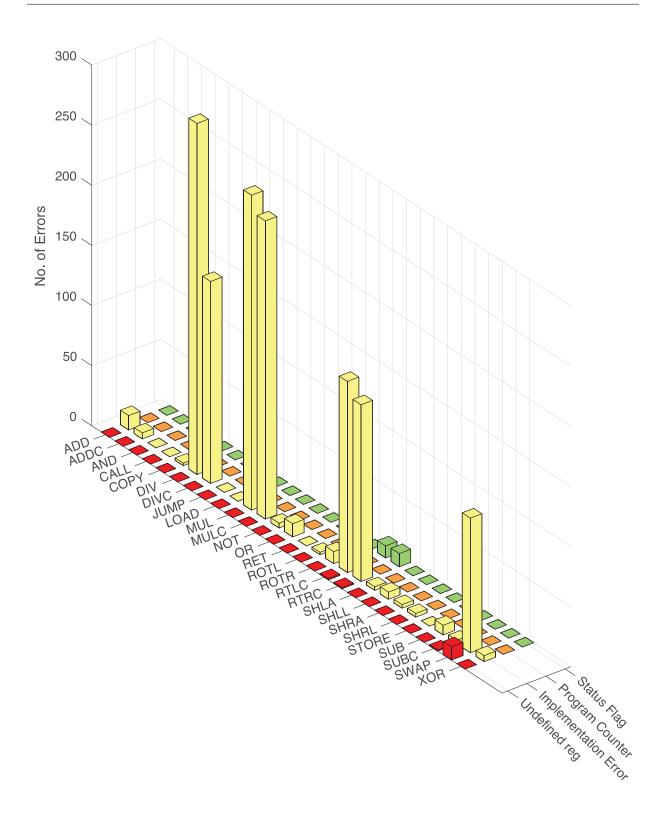

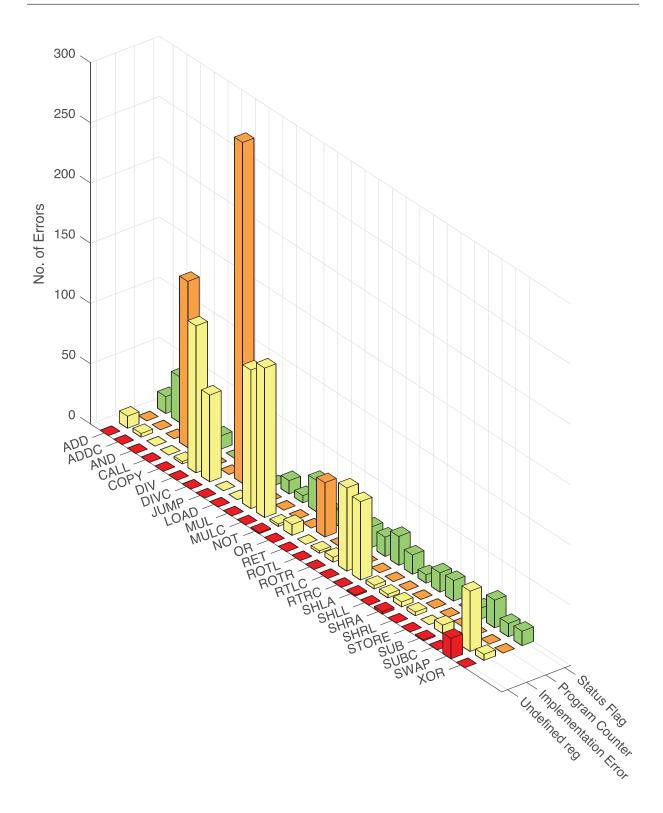

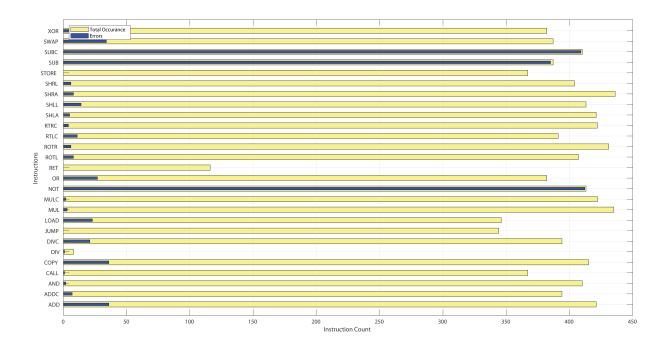

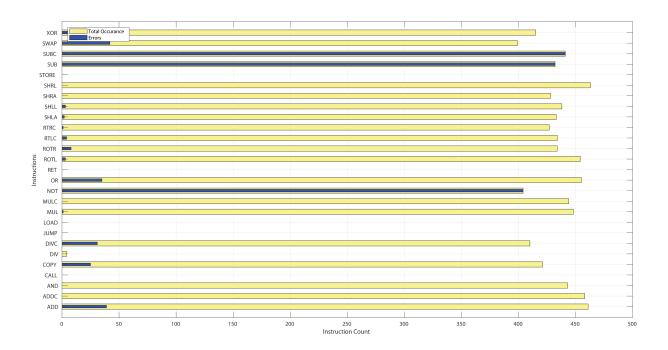

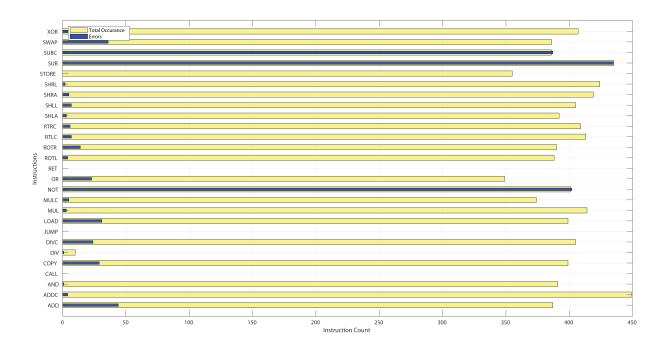

| 7.1  | Errors for Test T1 - mode 'a'                                                | 47  |

|------|------------------------------------------------------------------------------|-----|

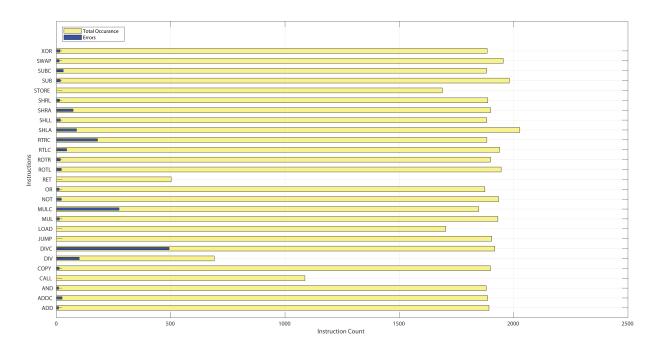

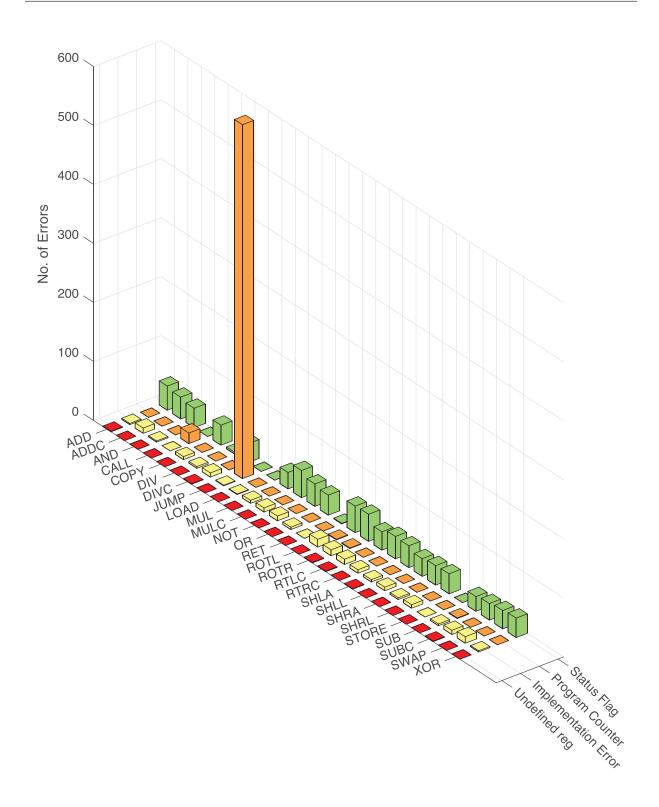

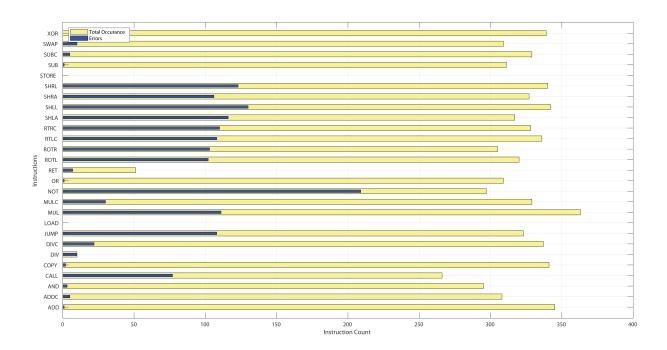

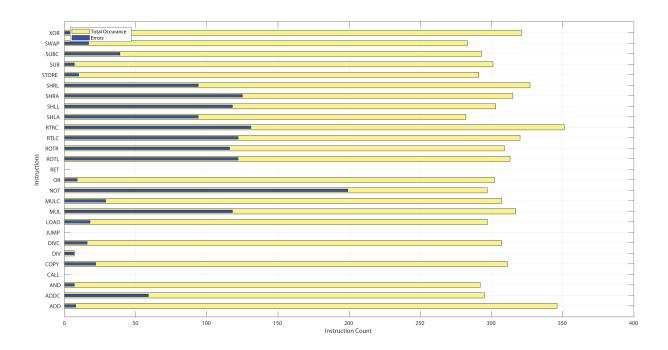

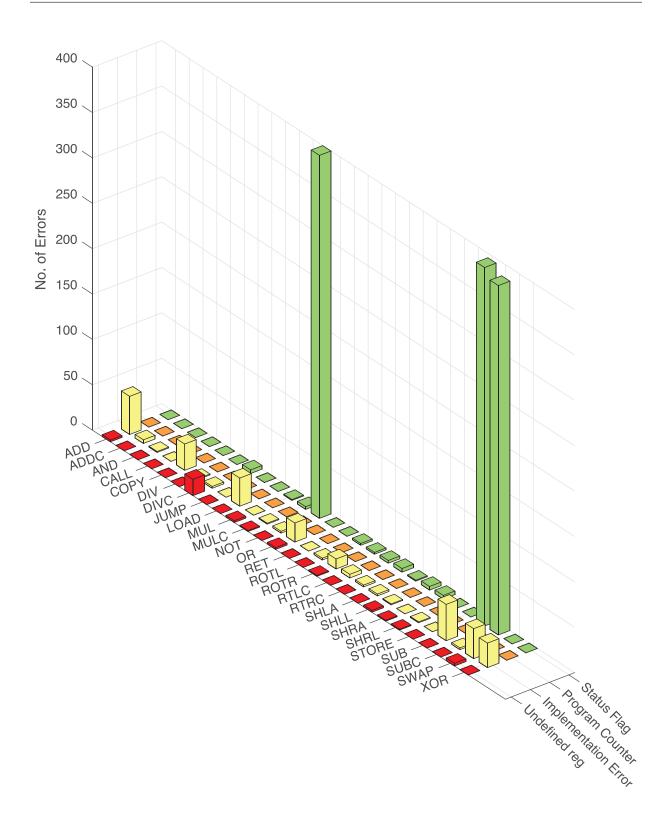

| 7.2  | Total error count for Test T1 - mode 'a'                                     | 48  |

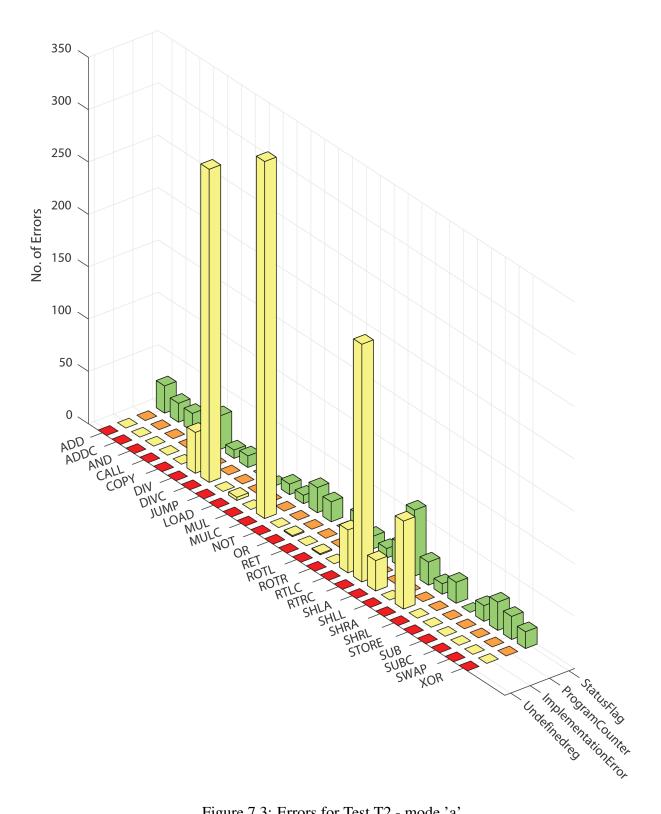

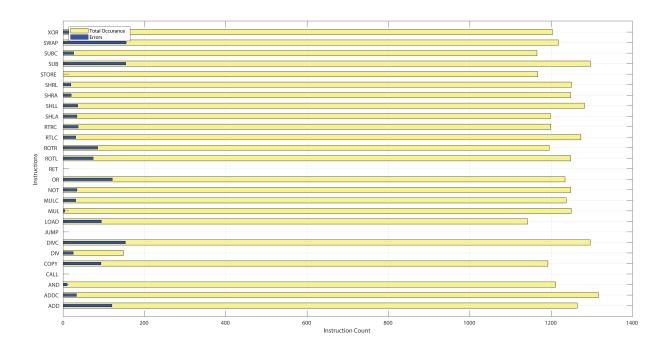

| 7.3  | Errors for Test T2 - mode 'a'                                                | 49  |

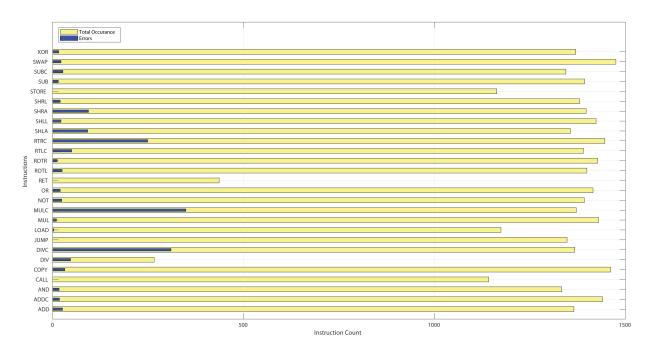

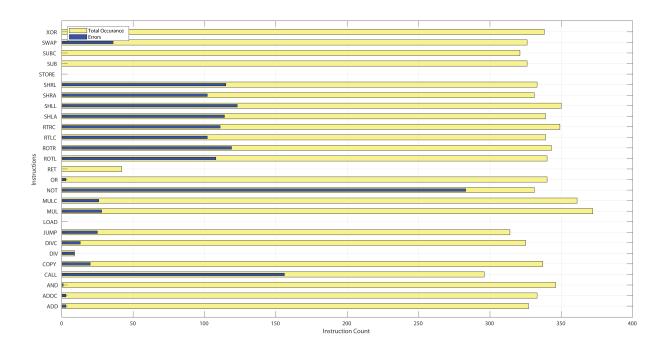

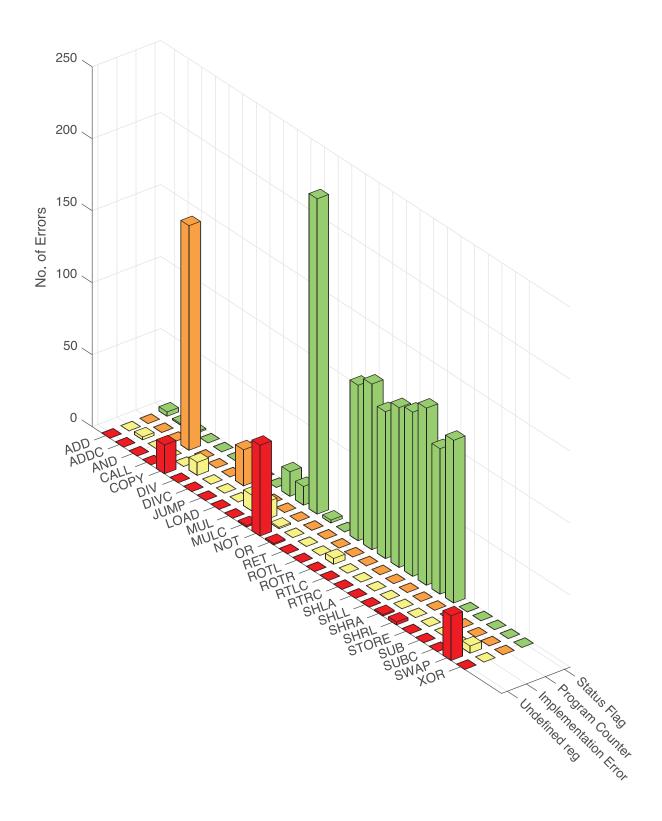

| 7.4  | Total error count for Test T2 - mode 'a'                                     | 50  |

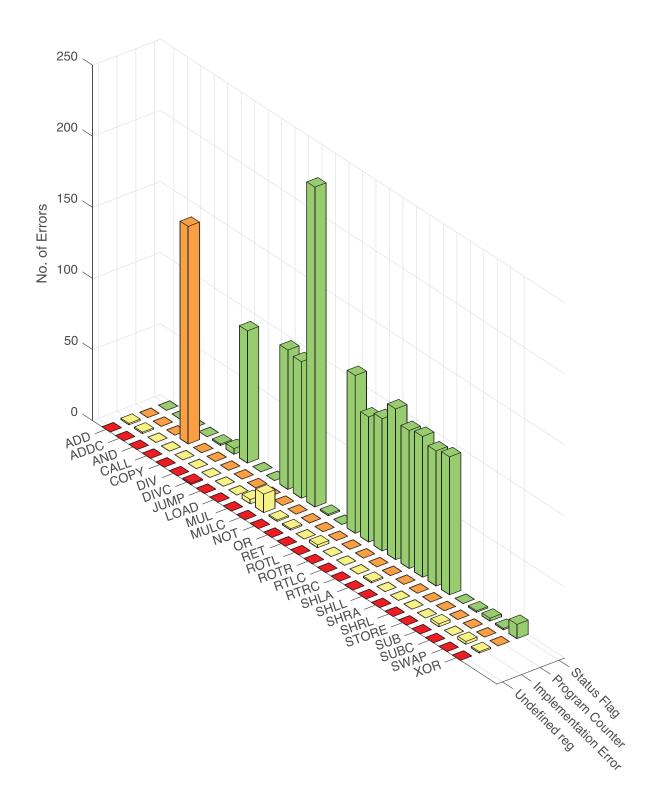

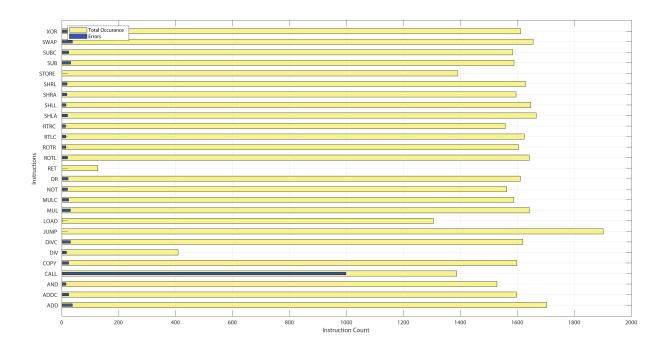

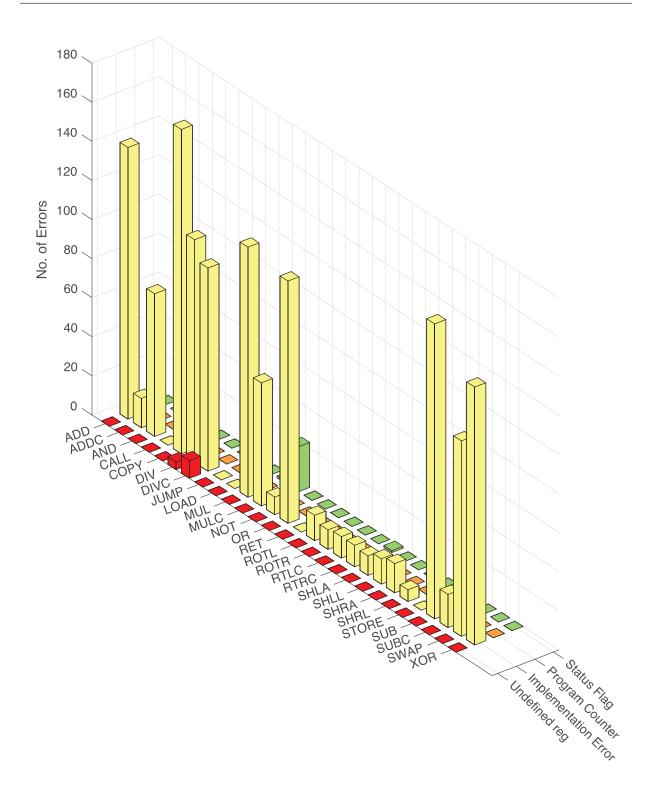

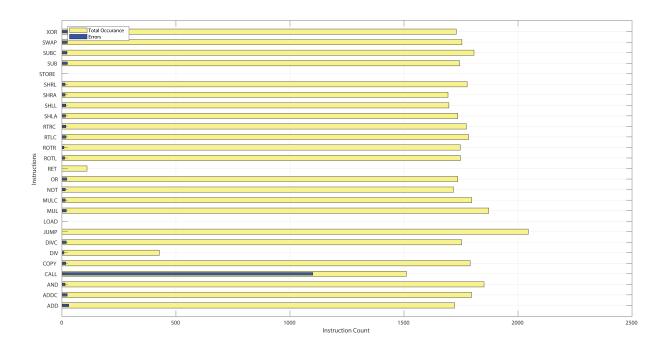

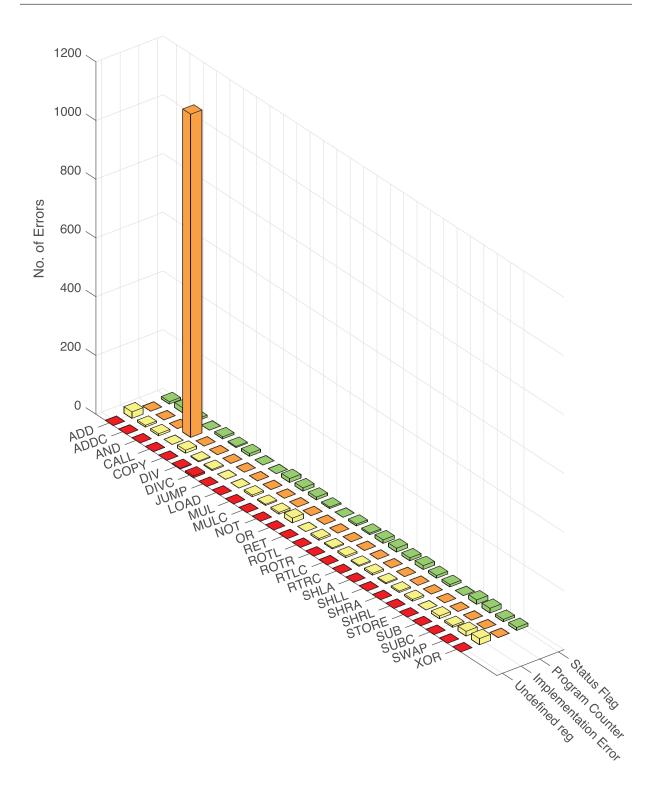

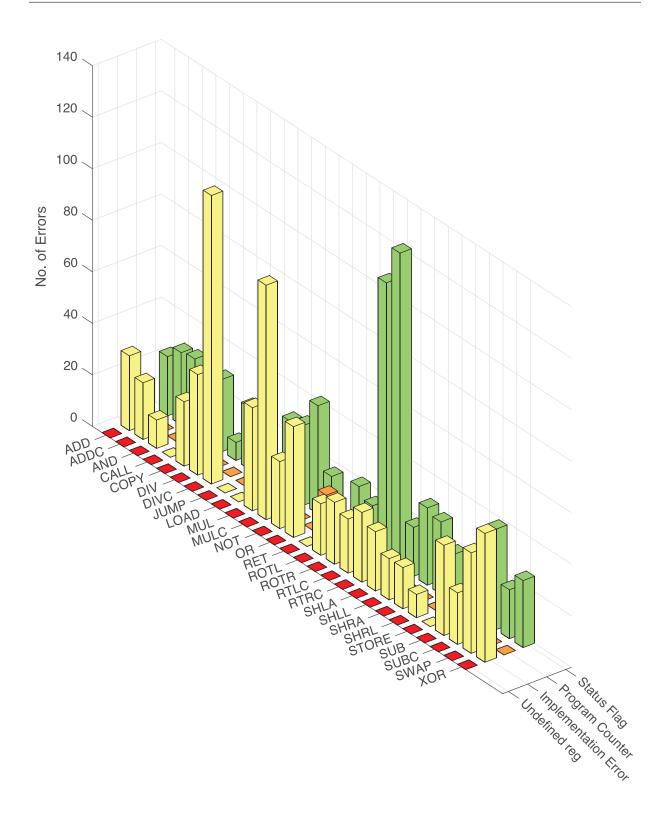

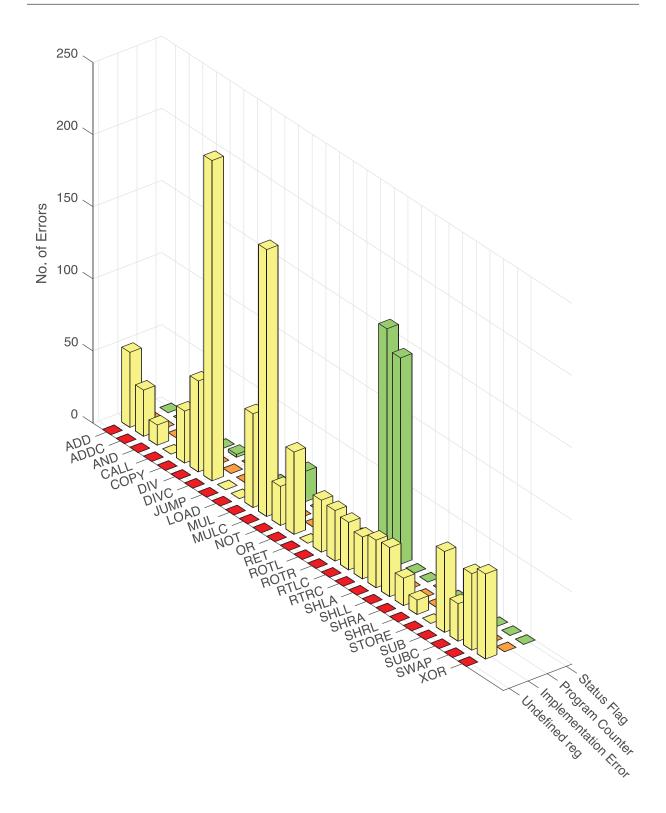

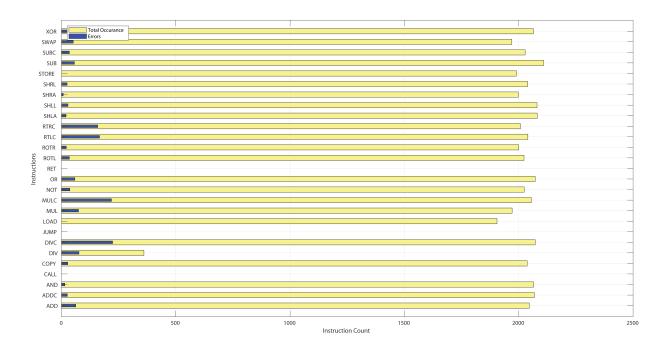

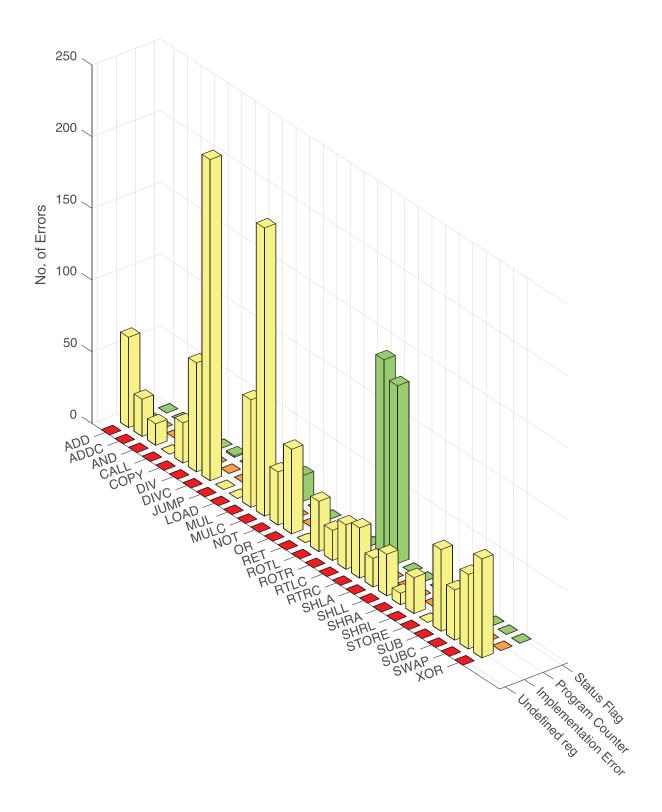

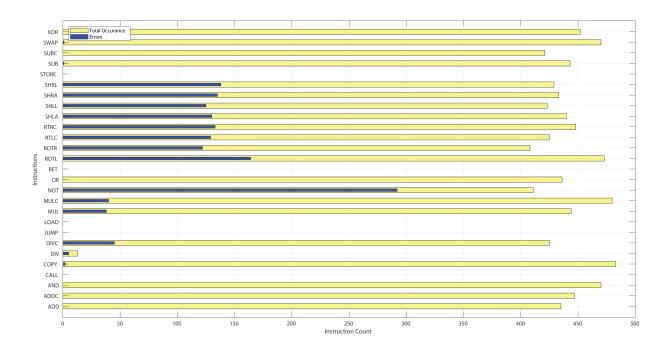

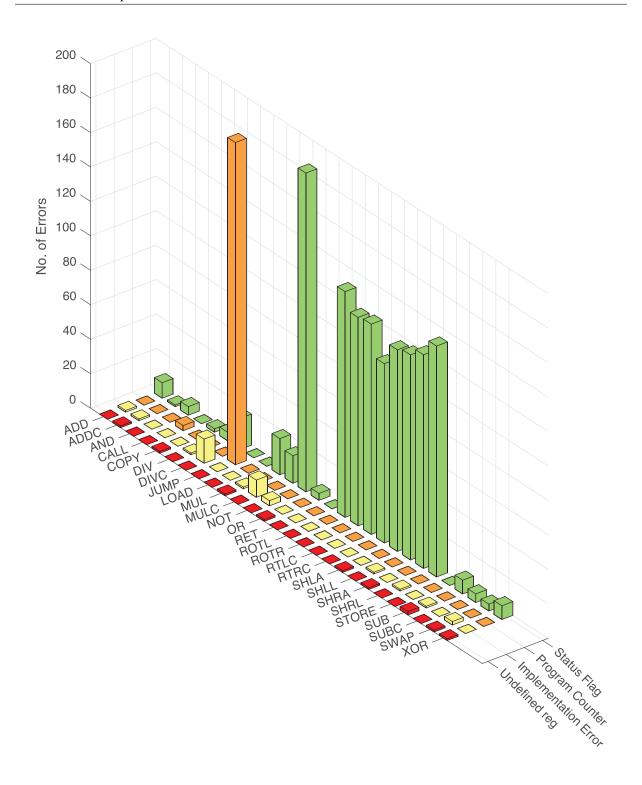

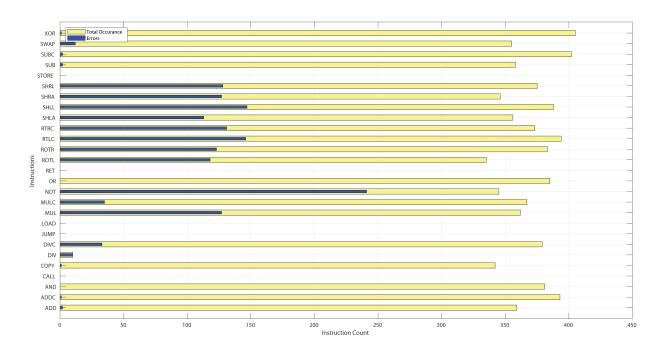

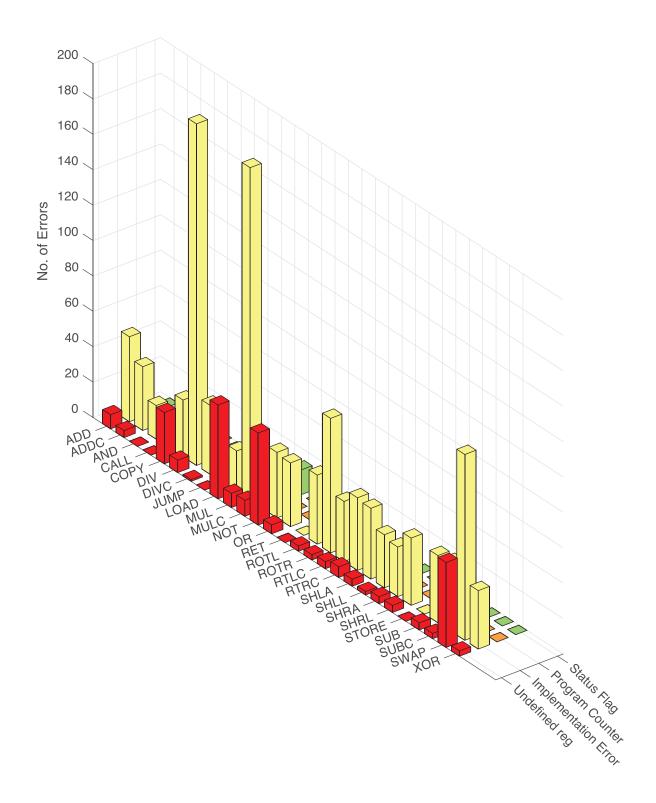

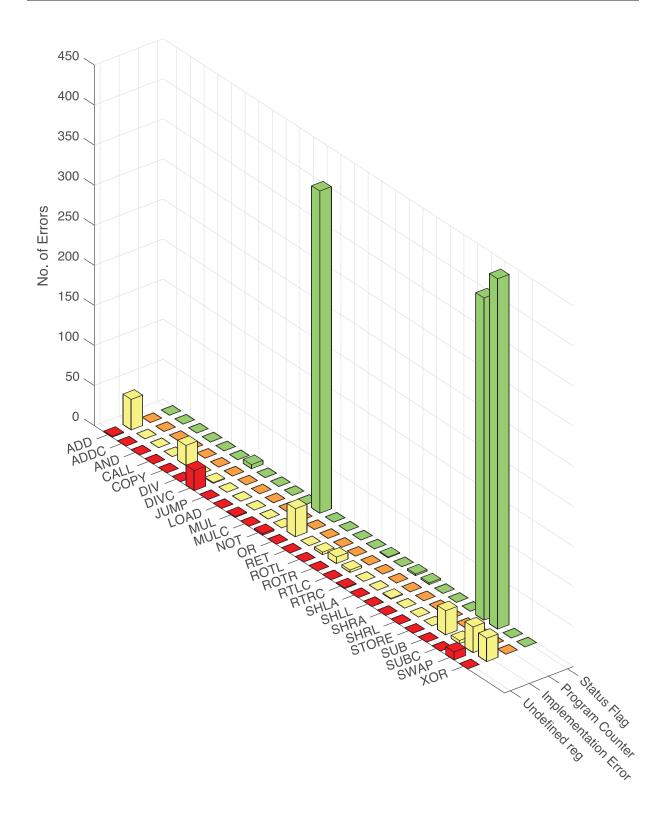

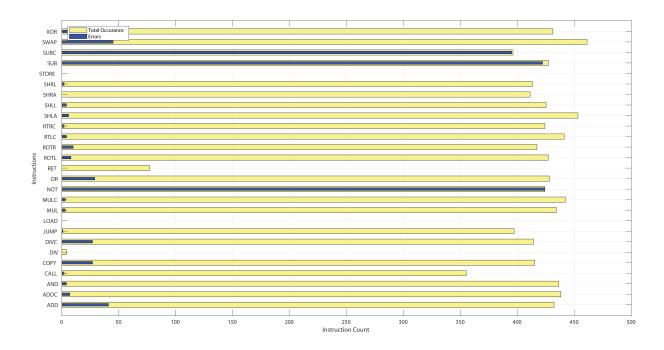

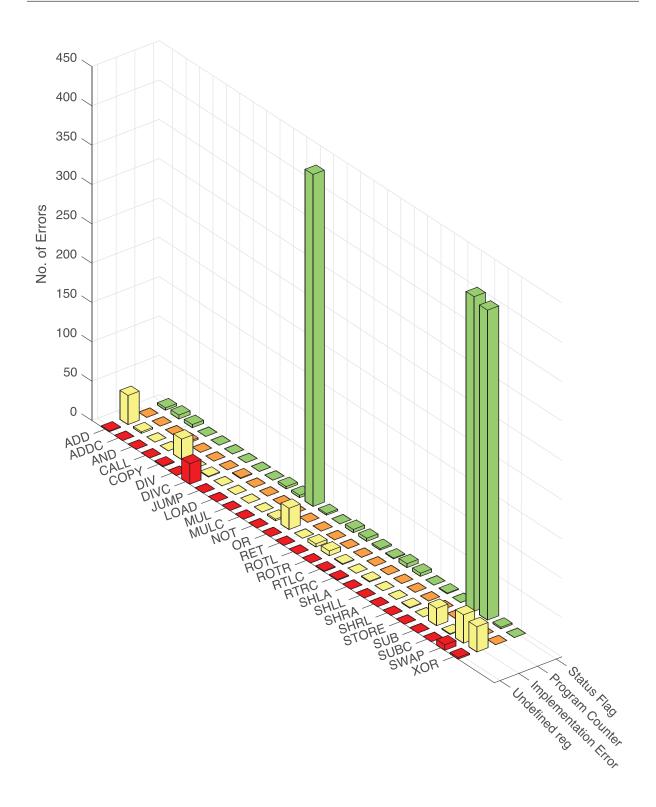

| 7.5  | Errors for Test T1 - mode 'm'                                                | 51  |

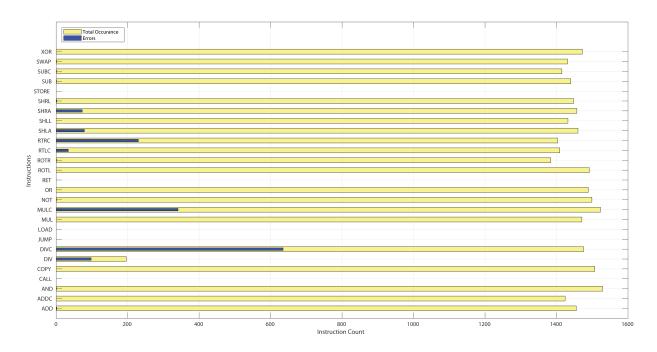

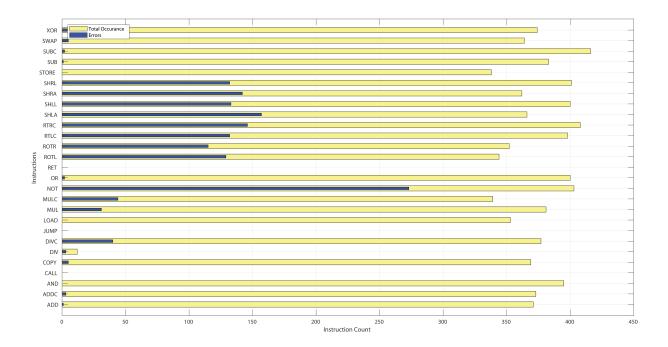

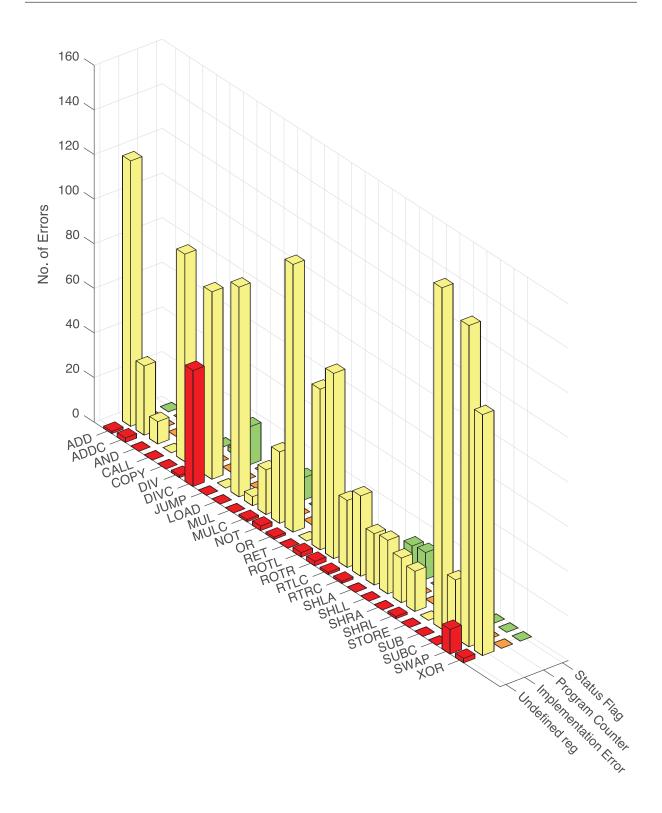

| 7.6  | Total error count for Test T1 - mode 'm'                                     | 52  |

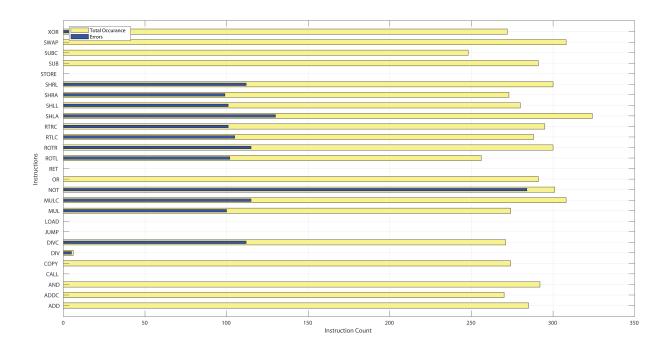

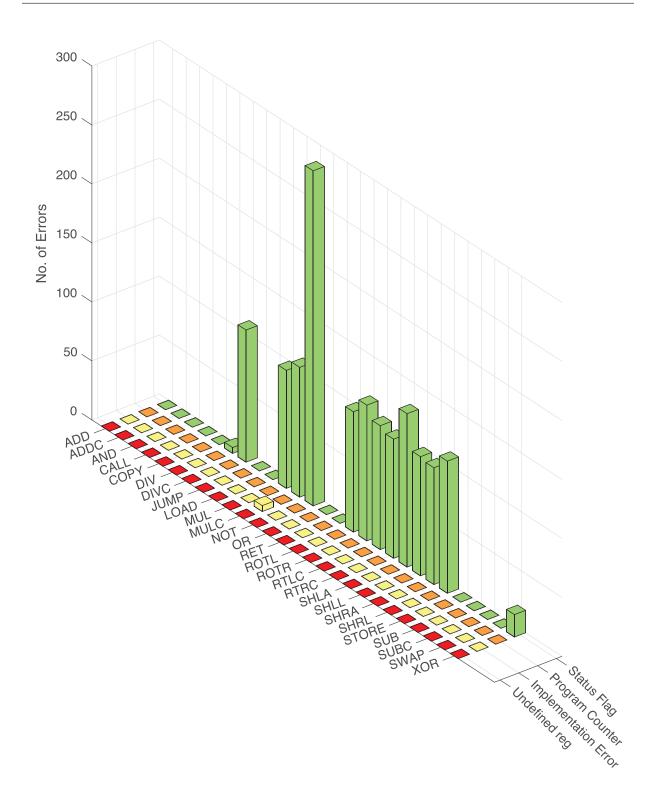

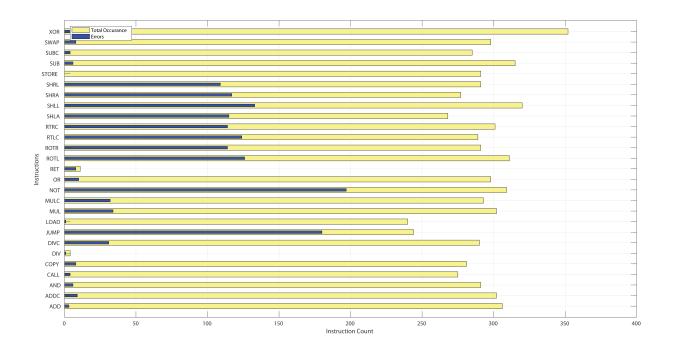

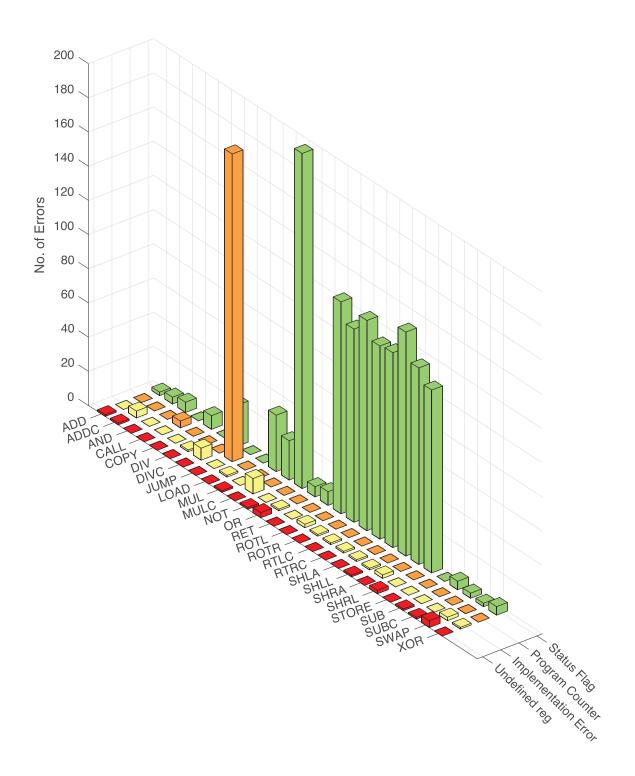

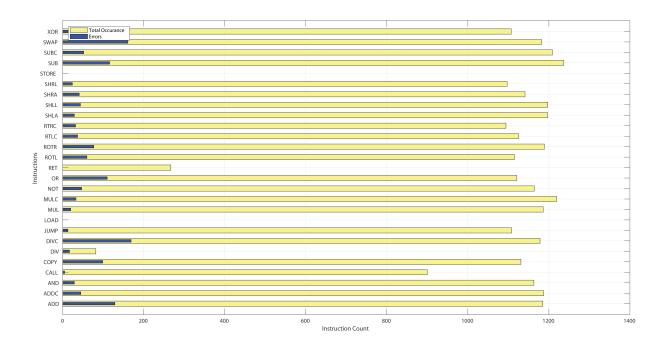

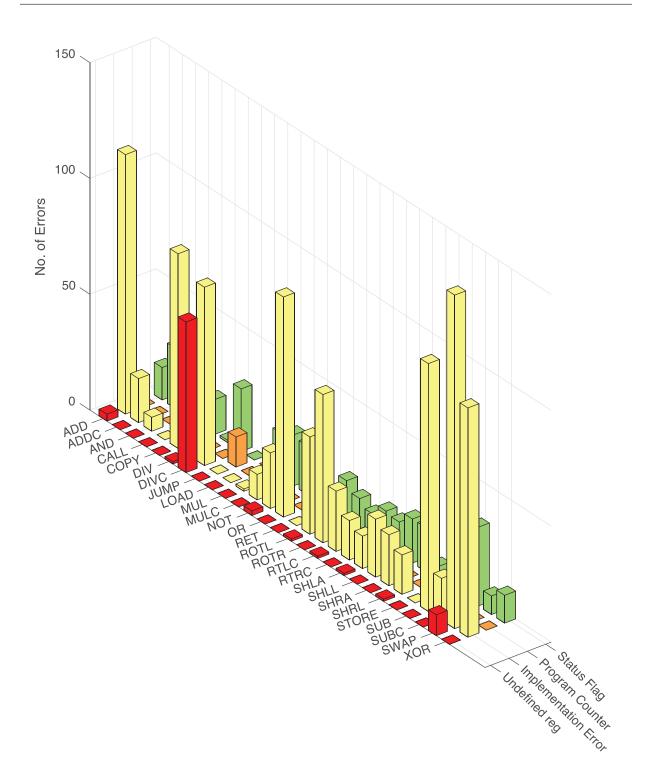

| 7.7  | Errors for Test T2 - mode 'm'                                                | 53  |

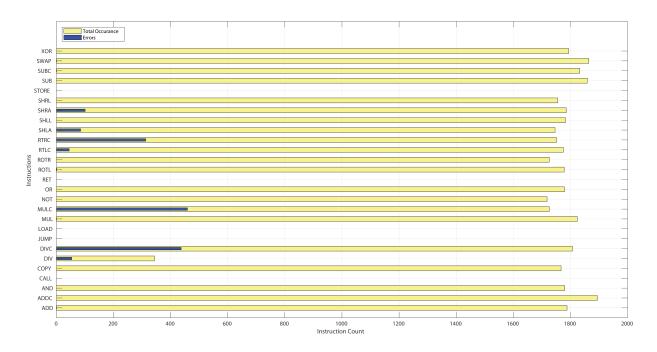

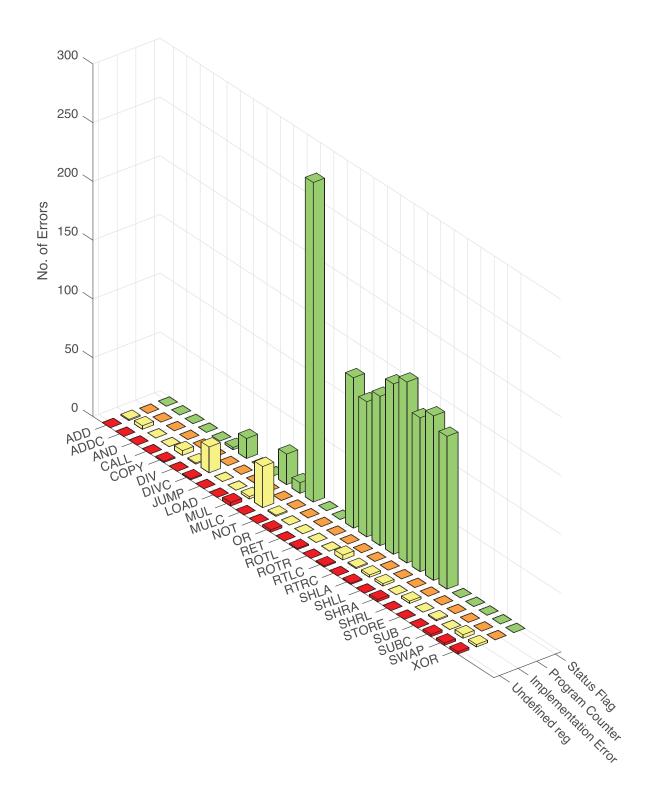

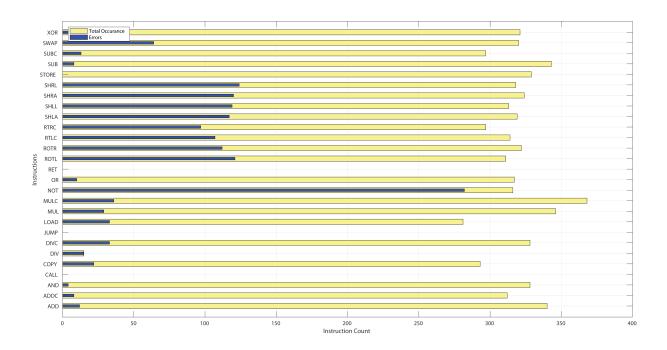

| 7.8  | Total error count for Test T2 - mode 'm'                                     | 54  |

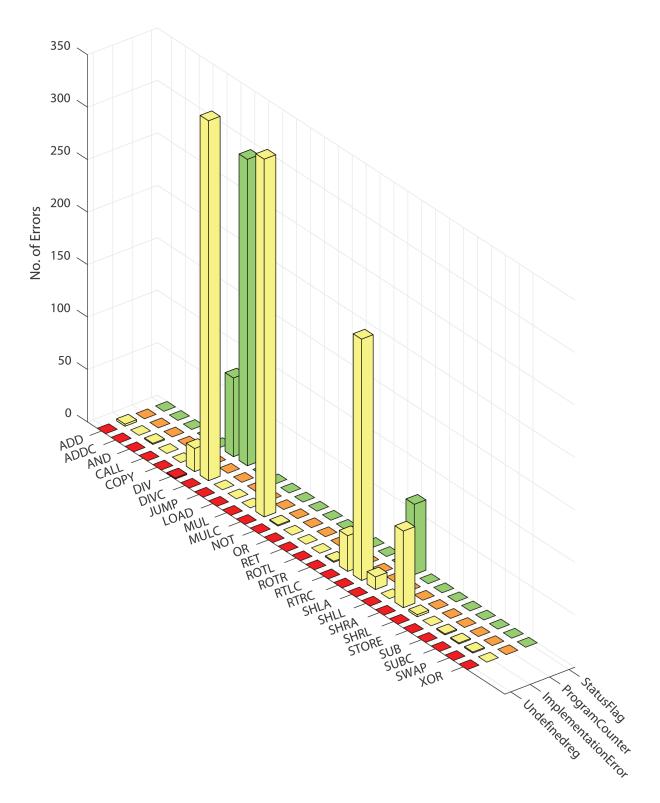

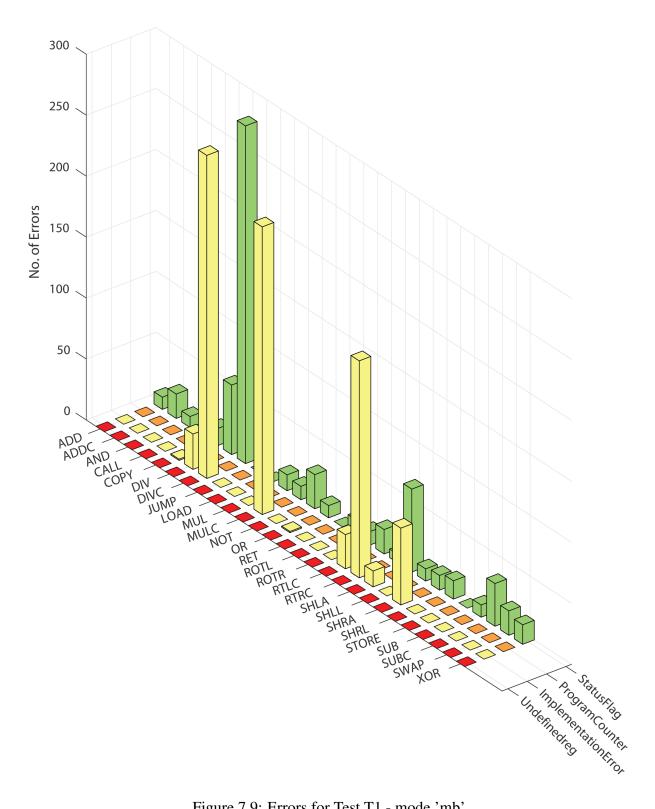

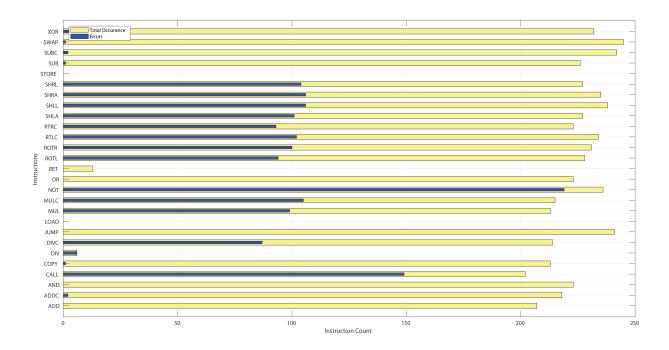

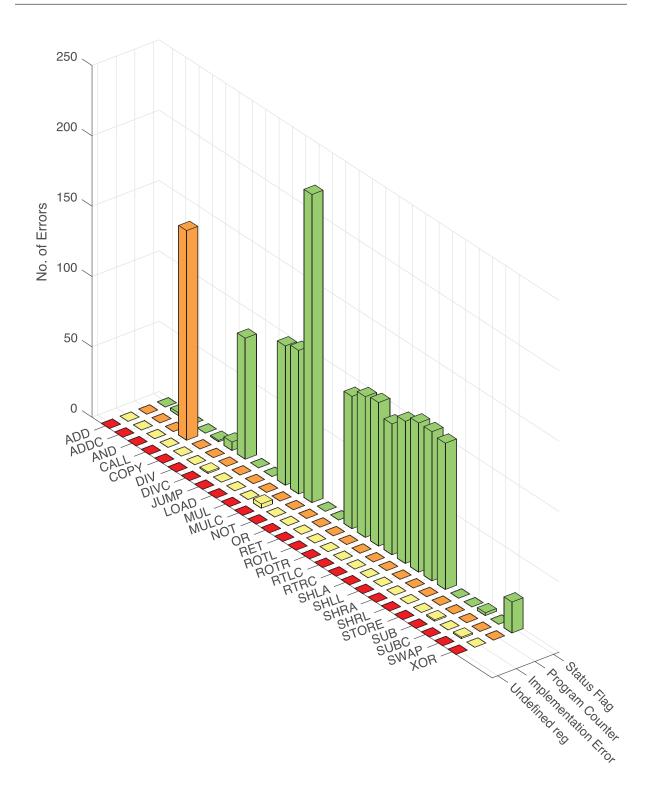

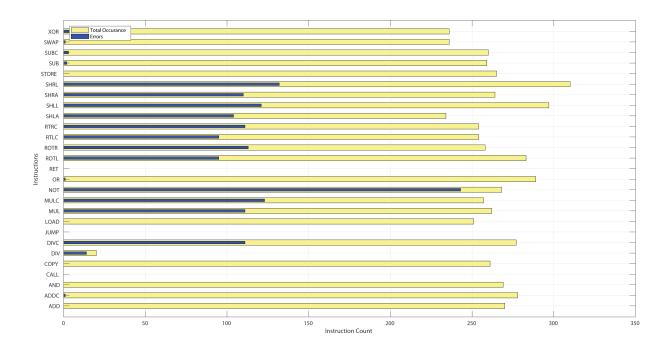

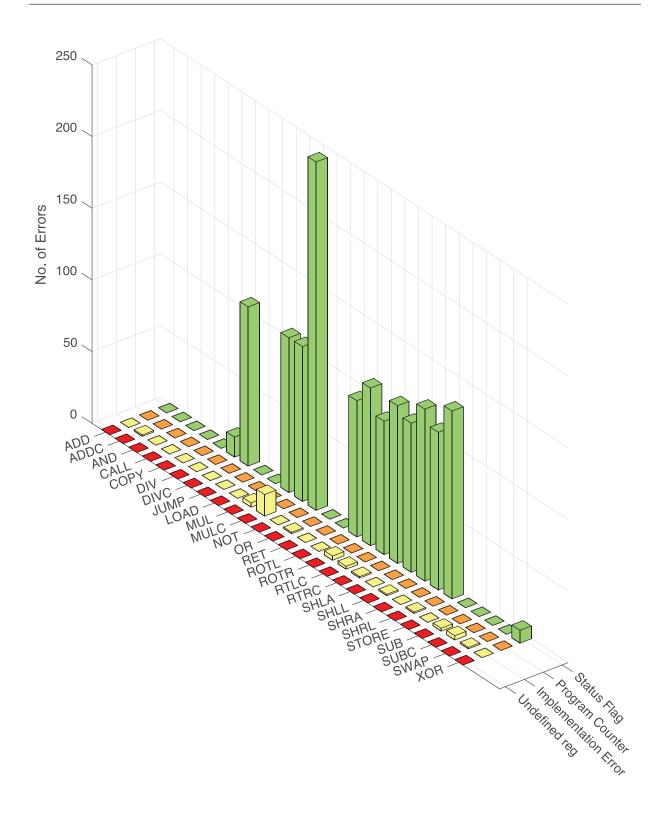

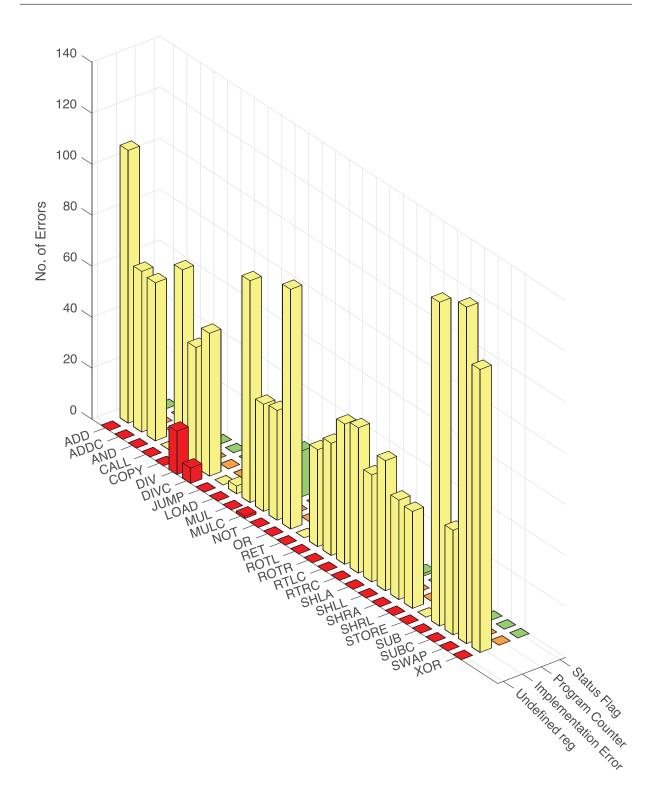

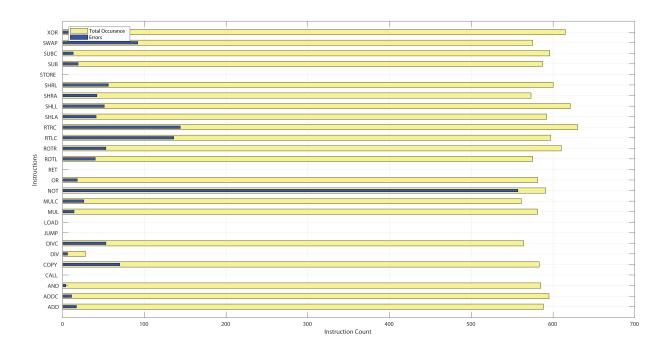

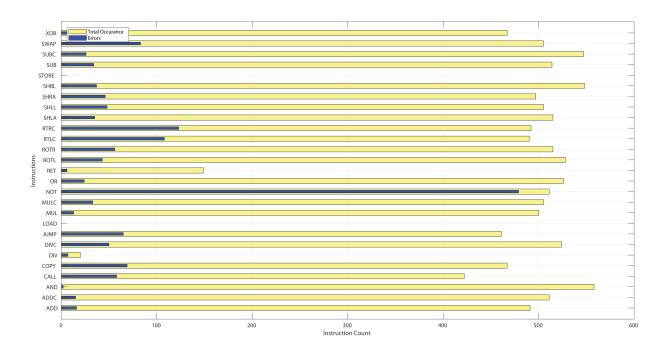

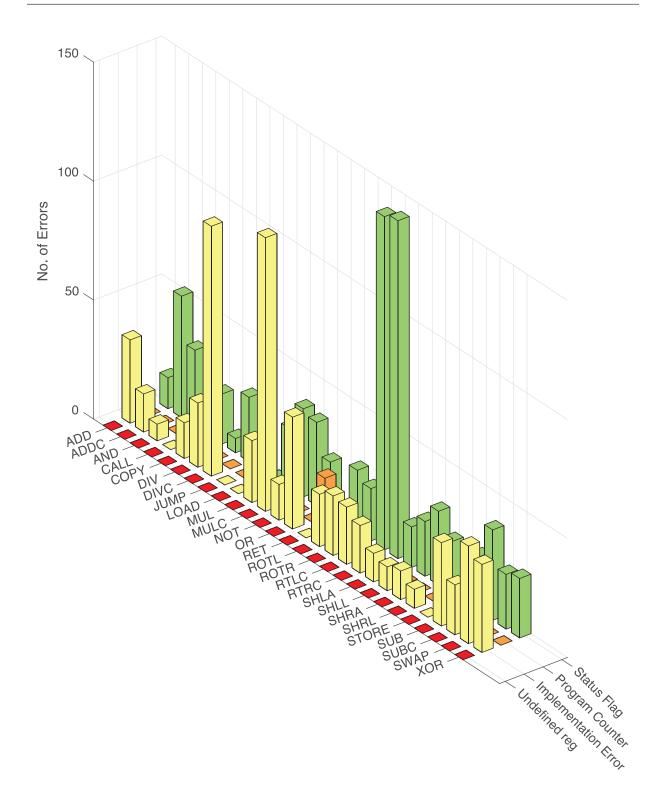

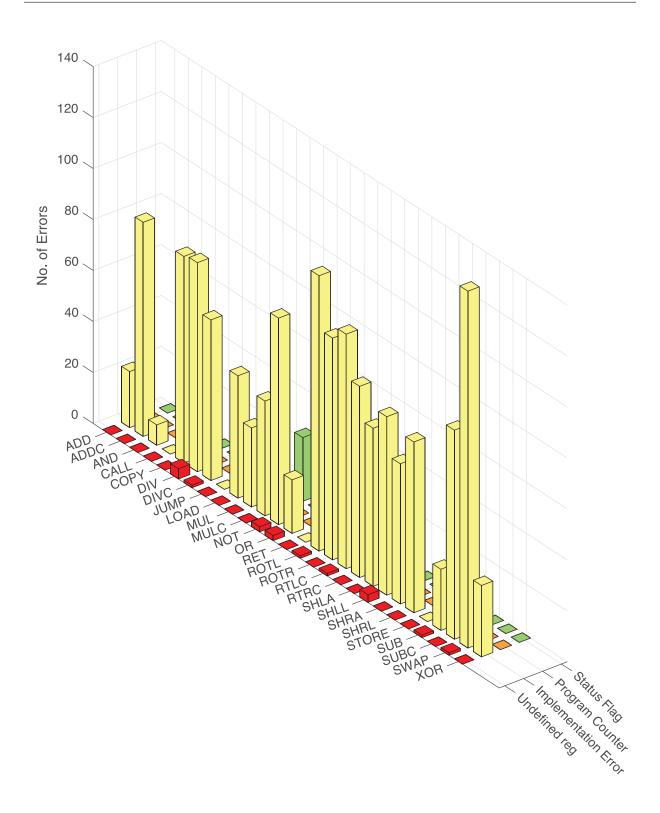

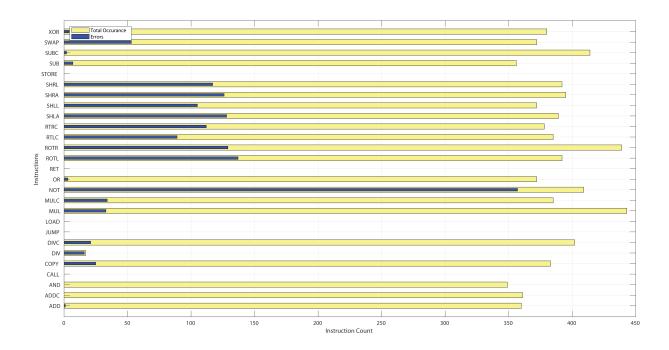

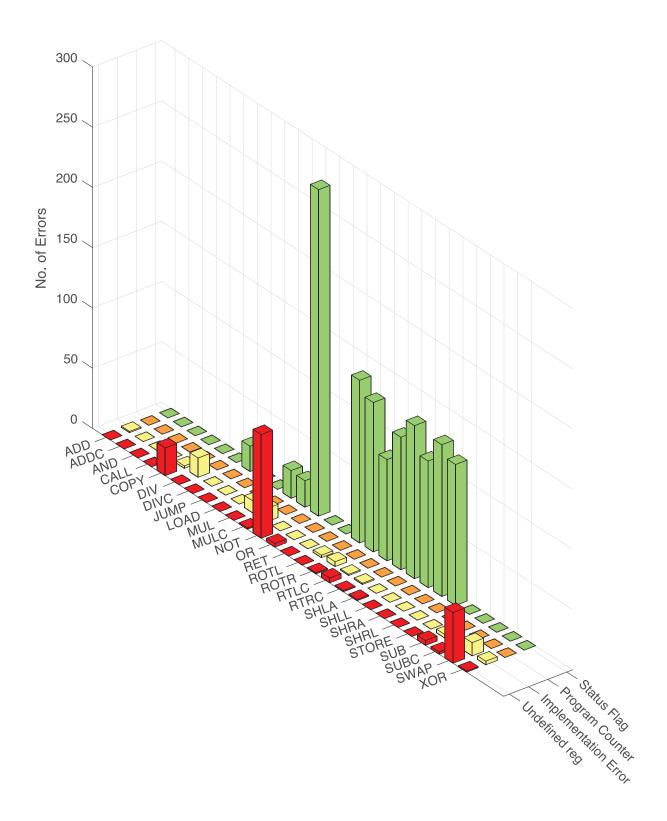

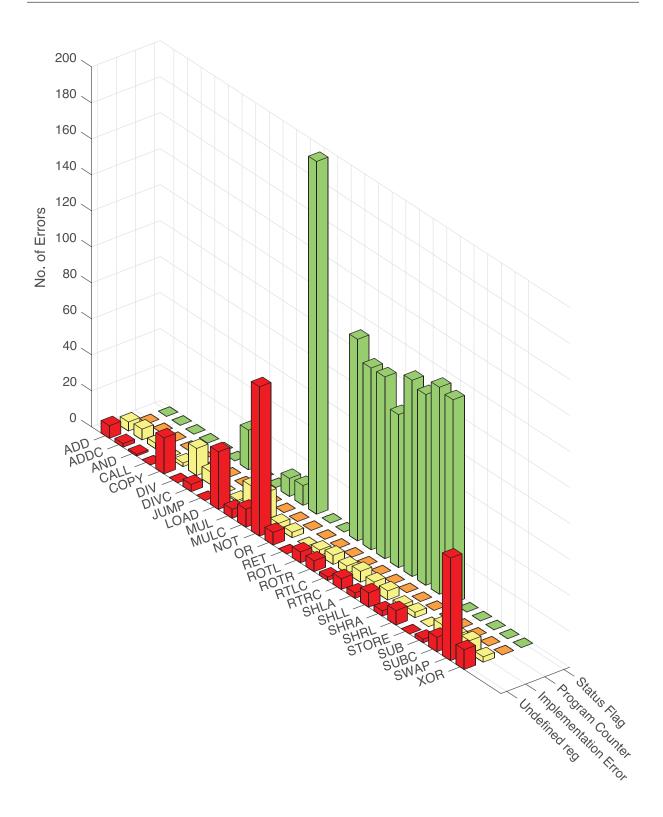

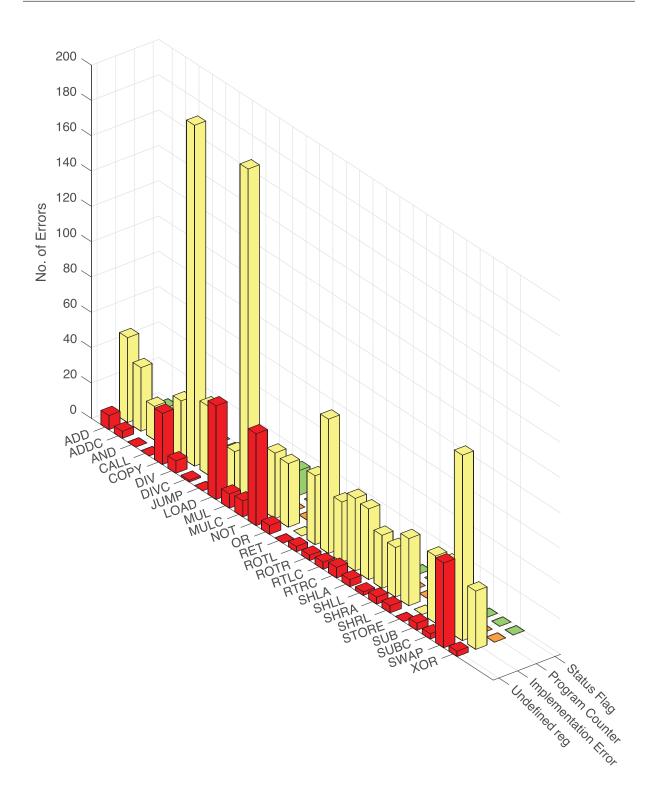

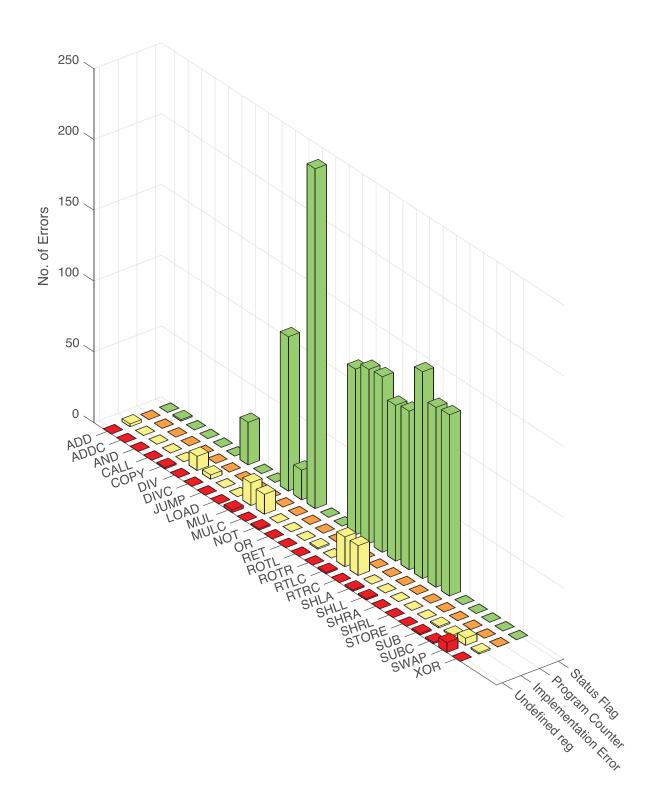

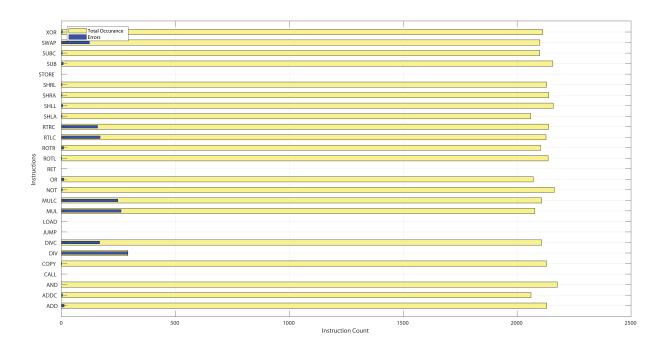

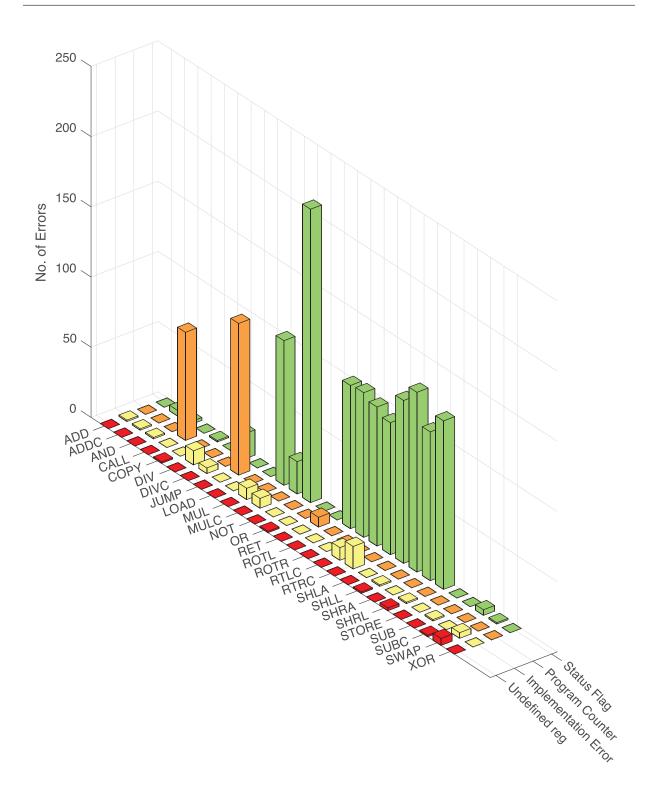

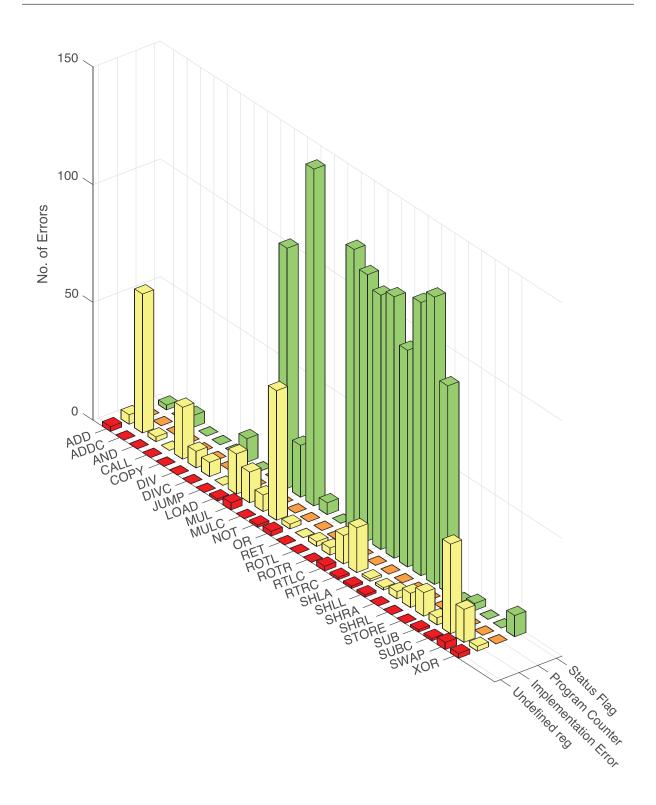

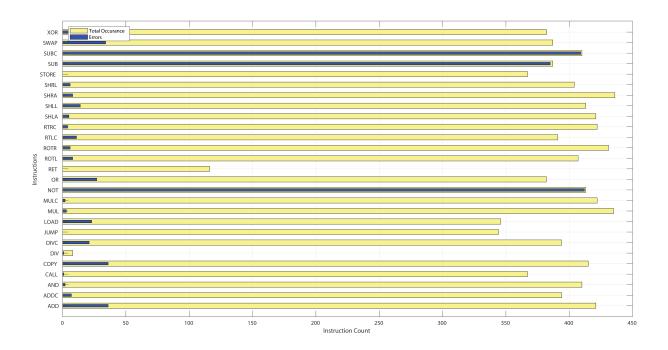

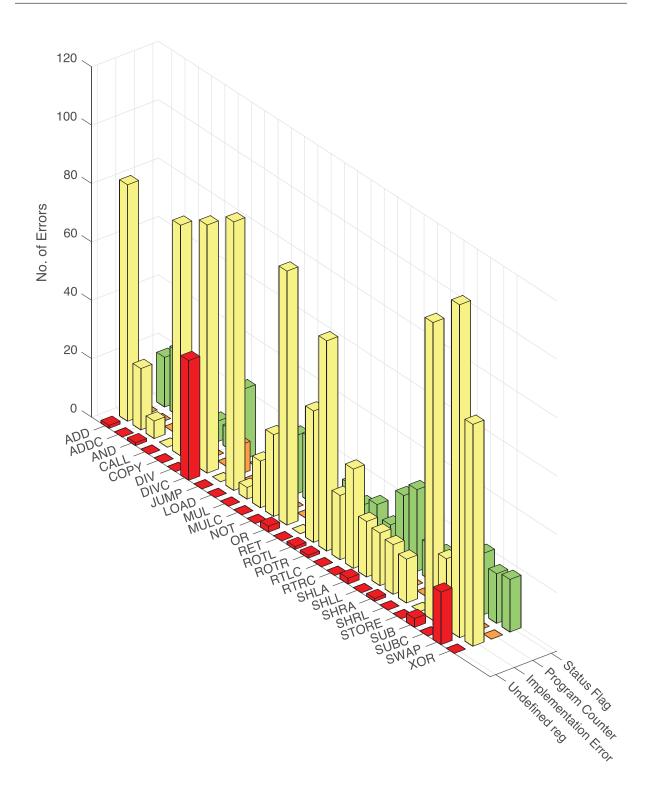

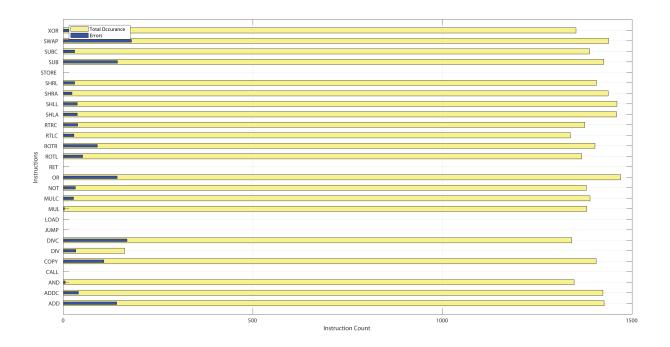

| 7.9  | Errors for Test T1 - mode 'mb'                                               | 55  |

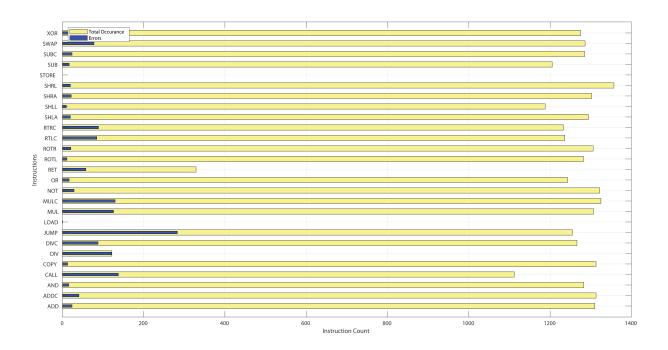

| 7.10 | Total error count for Test T1 - mode 'mb'                                    | 56  |

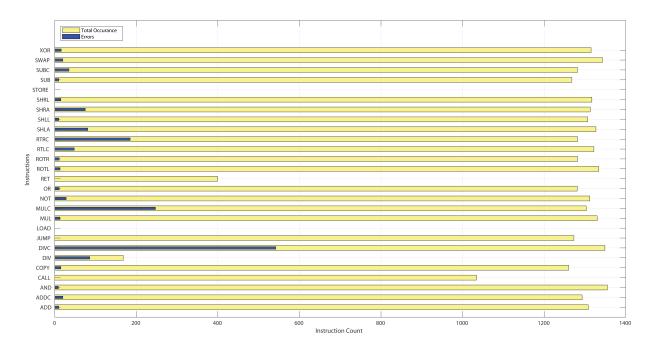

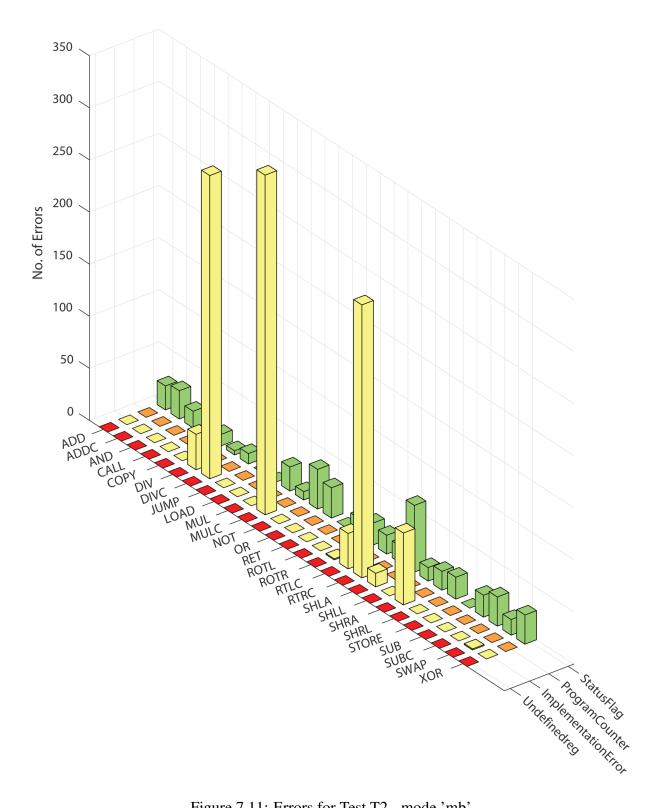

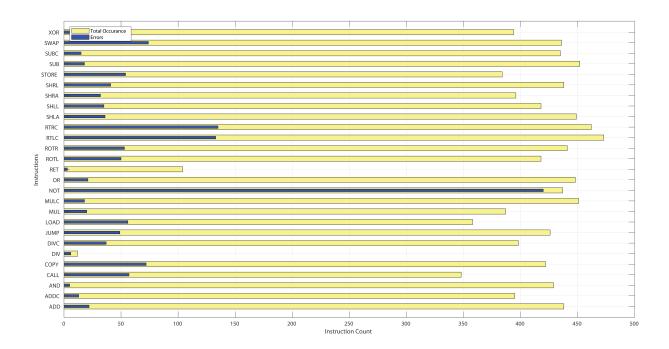

| 7.11 | Errors for Test T2 - mode 'mb'                                               | 57  |

| 7.12 | Total error count for Test T2 - mode 'mb'                                    | 58  |

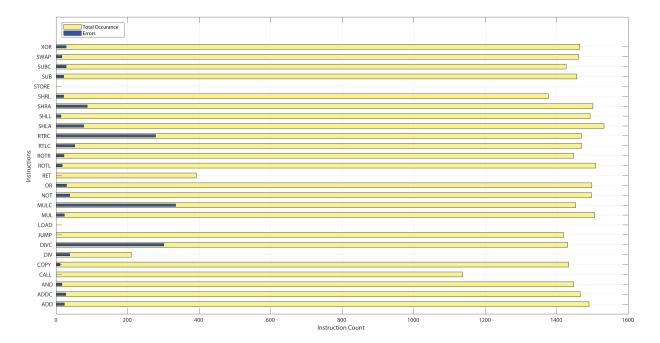

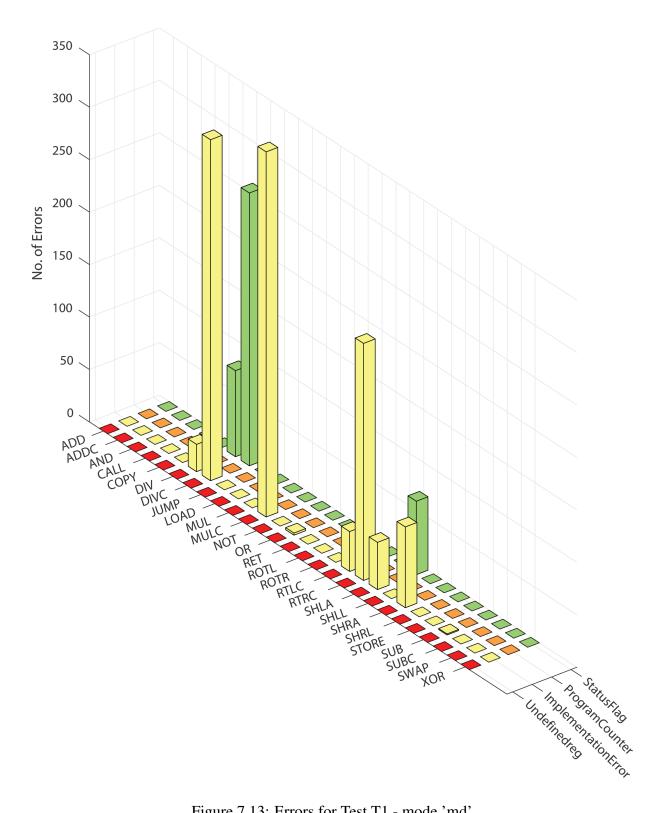

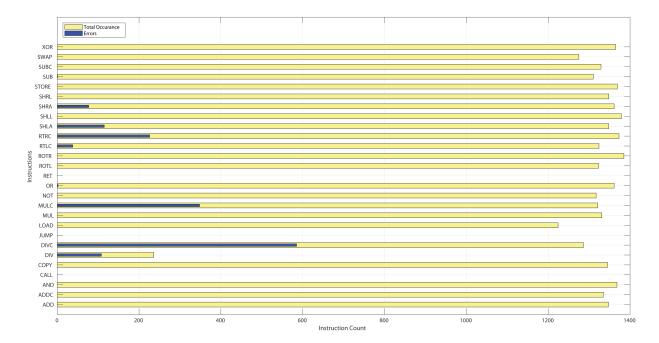

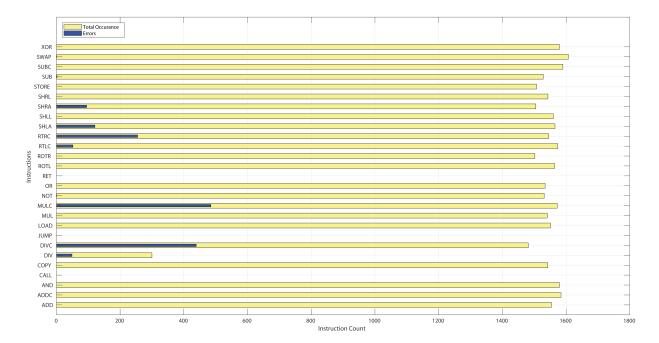

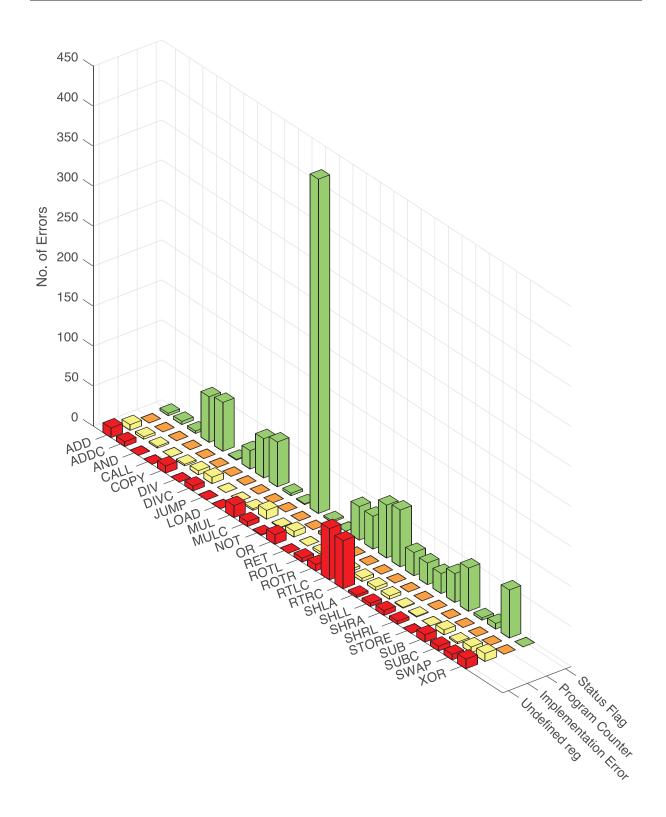

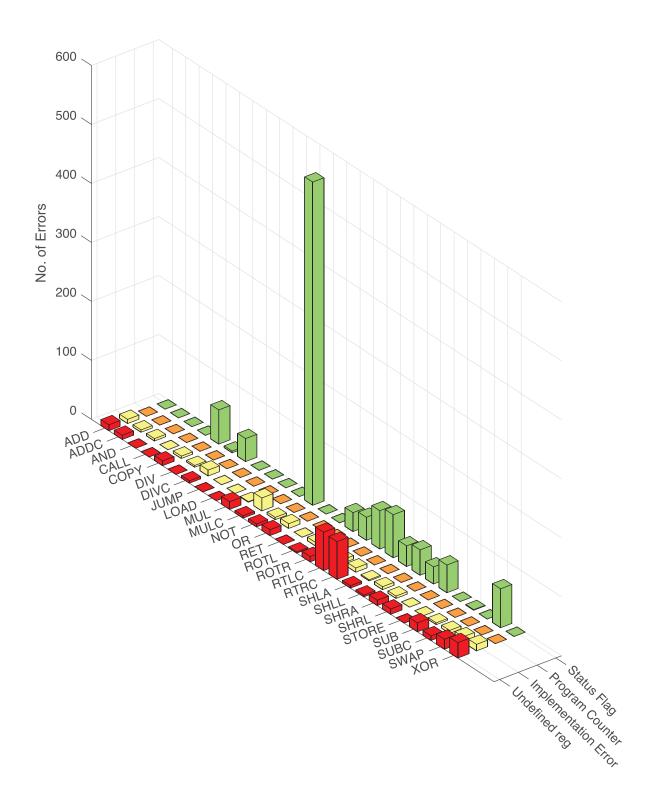

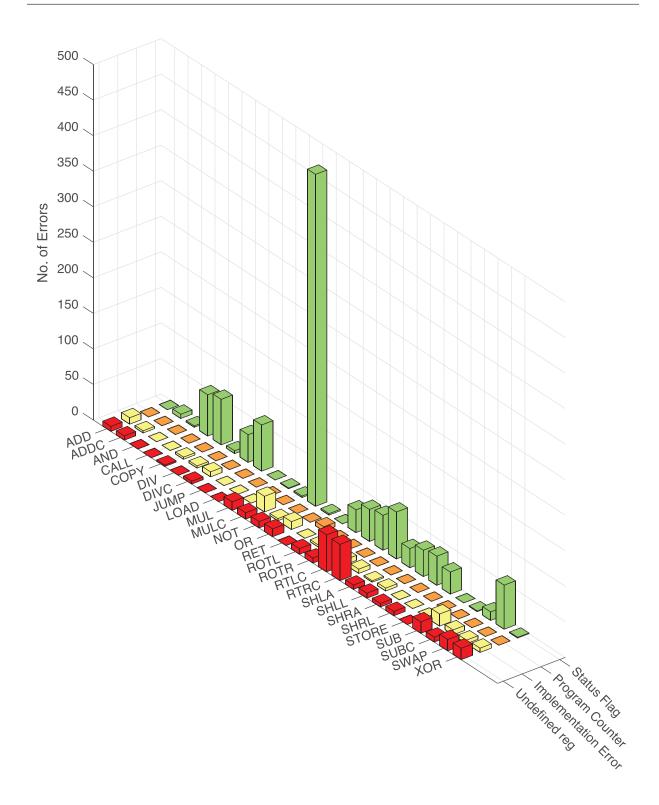

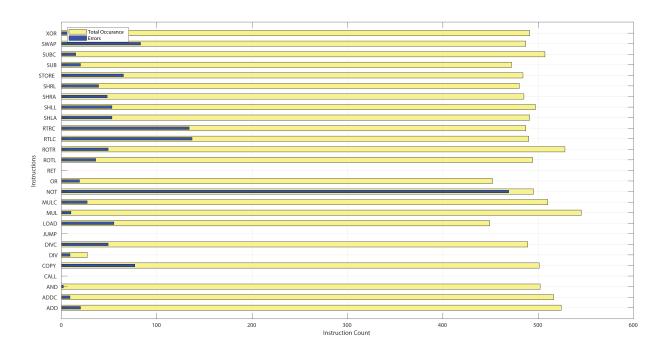

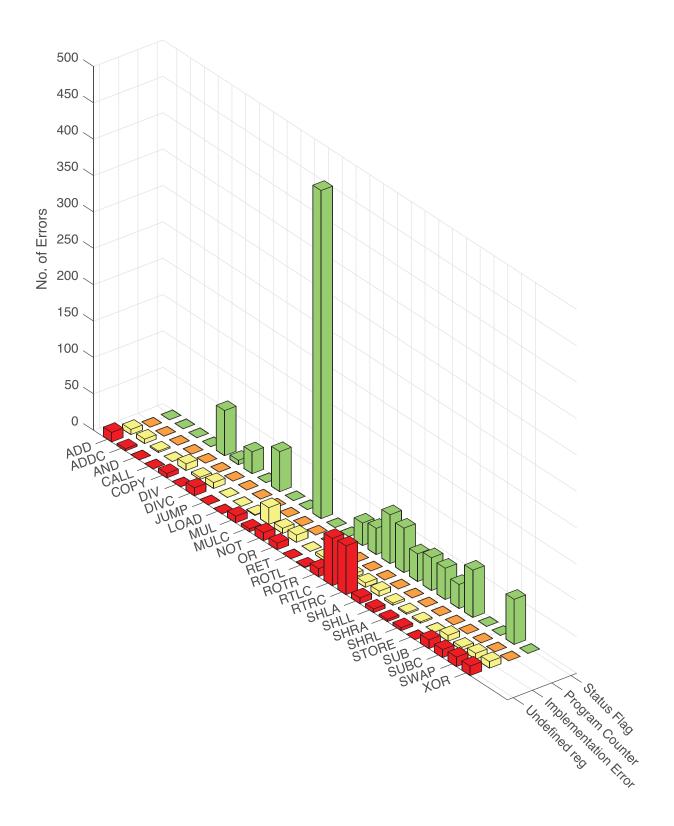

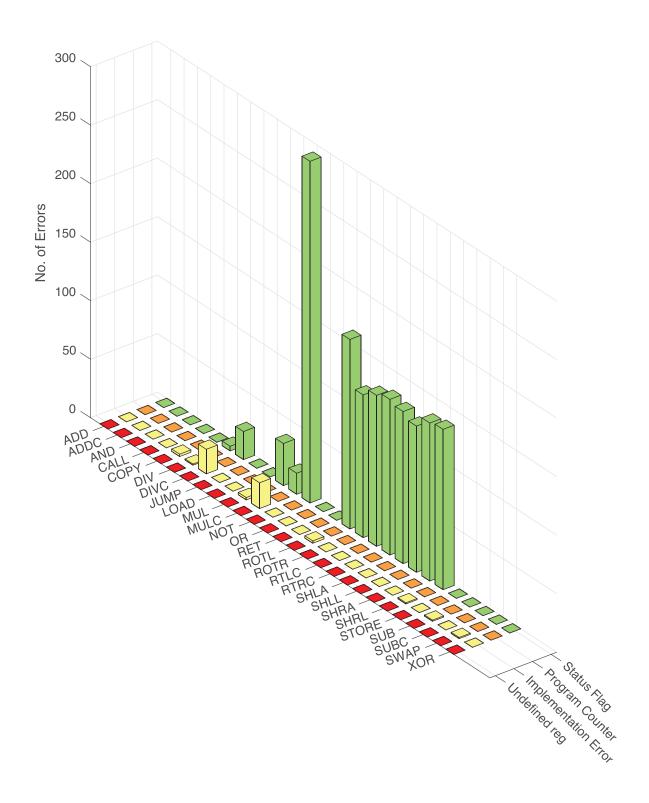

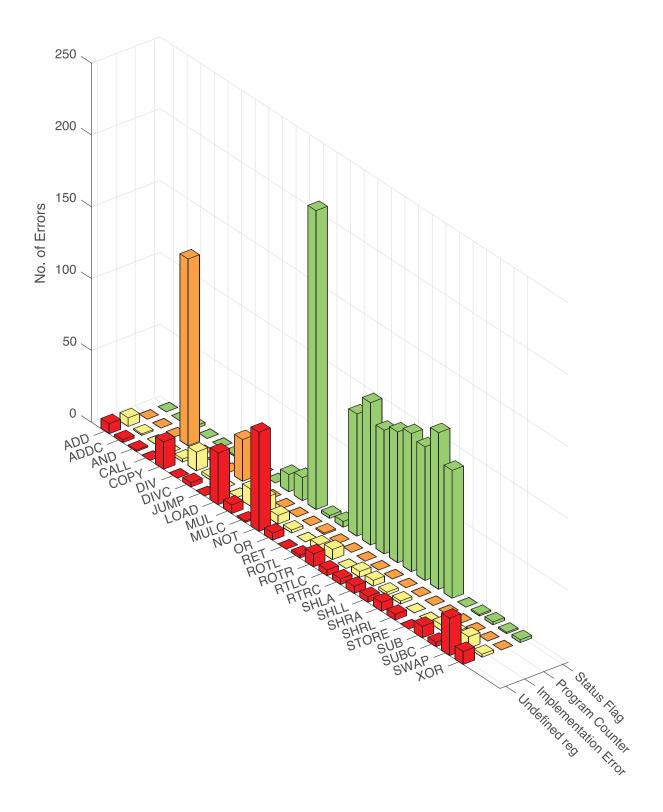

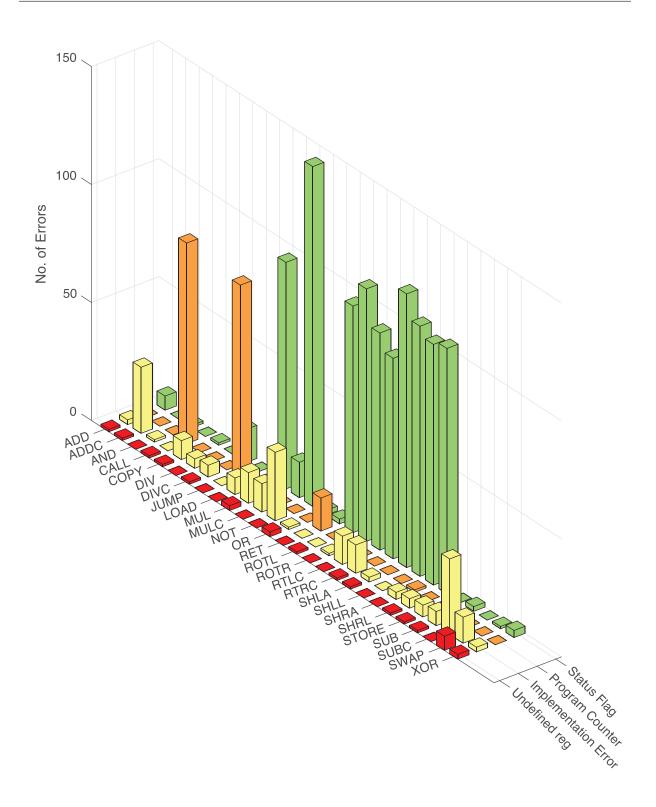

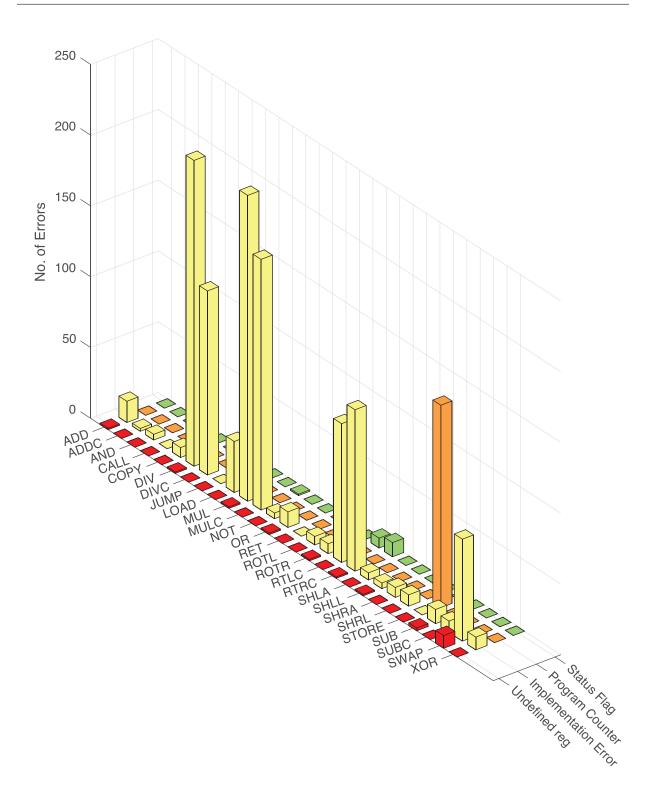

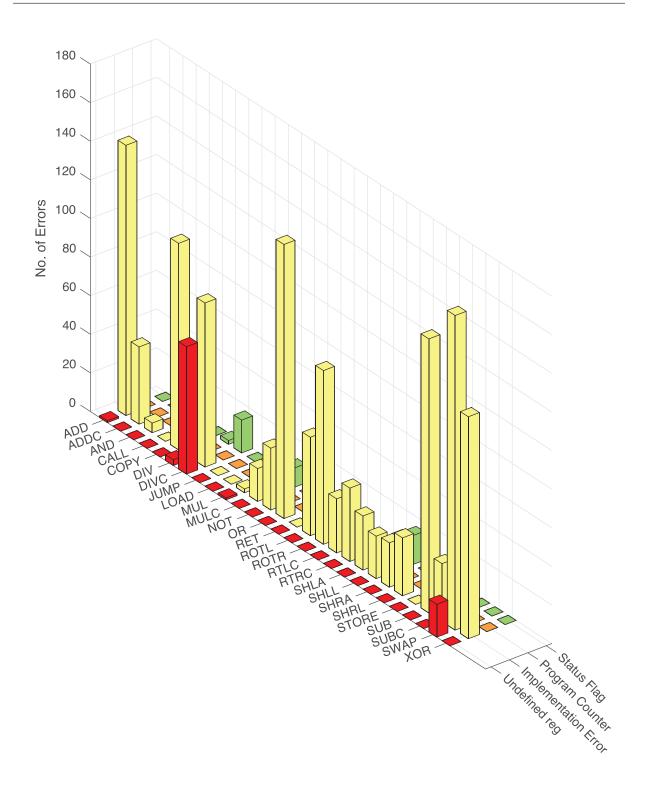

| 7.13 | Errors for Test T1 - mode 'md'                                               | 60  |

| 7.14 | Total error count for Test T1 - mode 'md'                                    | 61  |

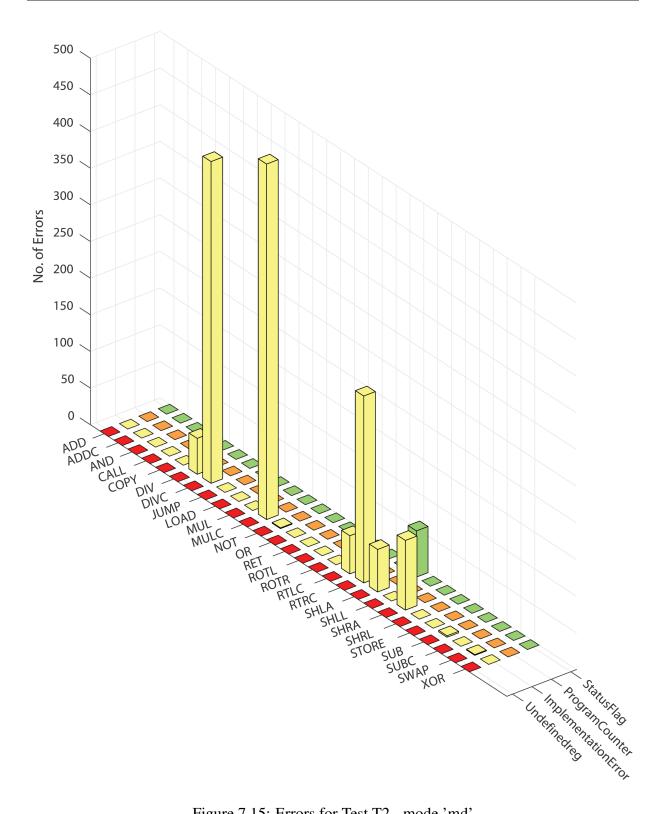

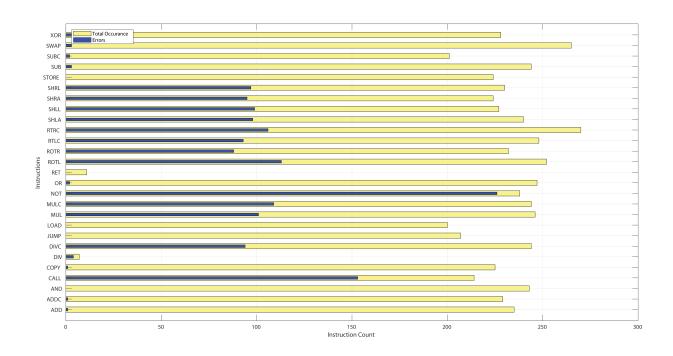

| 7.15 | Errors for Test T2 - mode 'md'                                               | 62  |

| 7.16 | Total error count for Test T2 - mode 'md'                                    | 63  |

| V.1  | Total Error count for test T1 (mode A) in processor axt                      | V-1 |

| V.2  | Errors found in processor <i>axt</i> while executing test <i>T1</i> (mode A) |     |

| V.3  | Total Error count for test T2 (mode A) in processor axt                      |     |

| V.4  | Errors found in processor <i>axt</i> while executing test <i>T2</i> (mode A) |     |

| V.5  | Total Error count for test <i>T1</i> (mode M) in processor <i>axt</i>        |     |

| V.6  | Errors found in processor <i>axt</i> while executing test <i>T1</i> (mode M) |     |

| V.7  | Total Error count for test <i>T2</i> (mode M) in processor <i>axt</i>        |     |

| V.8  | Errors found in processor <i>axt</i> while executing test <i>T2</i> (mode M) |     |

|      |                                                                              |     |

List of Figures xi

| V.9  | Total Error count for test $T1$ (mode MB) in processor $axt$                   | V-9          |

|------|--------------------------------------------------------------------------------|--------------|

| V.10 | Errors found in processor axt while executing test T1 (mode MB)                | V-10         |

| V.11 | Total Error count for test T2 (mode MB) in processor axt                       | <b>V</b> -11 |

| V.12 | Errors found in processor <i>axt</i> while executing test <i>T2</i> (mode MB)  | V-12         |

| V.13 | Total Error count for test T1 (mode MD) in processor axt                       | V-13         |

| V.14 | Errors found in processor axt while executing test T1 (mode MD)                | V-14         |

| V.15 | Total Error count for test T2 (mode MD) in processor axt                       | V-15         |

| V.16 | Errors found in processor axt while executing test T2 (mode MD)                | V-16         |

| V.17 | Total Error count for test $T1$ (mode A) in processor $dnm$                    | V-17         |

| V.18 | Errors found in processor $dnm$ while executing test $T1 \pmod{A} \dots \dots$ | V-18         |

| V.19 | Total Error count for test T2 (mode A) in processor dnm                        | V-19         |

| V.20 | Errors found in processor <i>dnm</i> while executing test <i>T2</i> (mode A)   | V-20         |

| V.21 | Total Error count for test T1 (mode M) in processor dnm                        | V-21         |

| V.22 | Errors found in processor $dnm$ while executing test $T1 \pmod{M} \dots \dots$ | V-22         |

| V.23 | Total Error count for test T2 (mode M) in processor dnm                        | V-23         |

| V.24 | Errors found in processor <i>dnm</i> while executing test <i>T2</i> (mode M)   | V-24         |

| V.25 | Total Error count for test $T1$ (mode MB) in processor $dnm$                   | V-25         |

| V.26 | Errors found in processor $dnm$ while executing test $T1$ (mode MB)            | V-26         |

| V.27 | Total Error count for test T2 (mode MB) in processor dnm                       | V-27         |

| V.28 | Errors found in processor <i>dnm</i> while executing test <i>T2</i> (mode MB)  | V-28         |

| V.29 | Total Error count for test $T1$ (mode MD) in processor $dnm$                   | V-29         |

| V.30 | Errors found in processor $dnm$ while executing test $T1$ (mode MD)            | V-30         |

| V.31 | Total Error count for test T2 (mode MD) in processor dnm                       | V-31         |

| V.32 | Errors found in processor <i>dnm</i> while executing test <i>T2</i> (mode MD)  | V-32         |

| V.33 | Total Error count for test $T1$ (mode A) in processor $nxp$                    | V-33         |

List of Figures xii

| V.34 Errors found in processor $nxp$ while executing test $TI$ (mode A) $V-32$          |

|-----------------------------------------------------------------------------------------|

| V.35 Total Error count for test T2 (mode A) in processor nxp                            |

| V.36 Errors found in processor <i>nxp</i> while executing test <i>T2</i> (mode A) V-36  |

| V.37 Total Error count for test <i>T1</i> (mode M) in processor <i>nxp</i>              |

| V.38 Errors found in processor <i>nxp</i> while executing test <i>T1</i> (mode M) V-38  |

| V.39 Total Error count for test $T2$ (mode M) in processor $nxp$                        |

| V.40 Errors found in processor <i>nxp</i> while executing test <i>T2</i> (mode M) V-40  |

| V.41 Total Error count for test <i>T1</i> (mode MB) in processor <i>nxp</i>             |

| V.42 Errors found in processor <i>nxp</i> while executing test <i>T1</i> (mode MB) V-42 |

| V.43 Total Error count for test $T2$ (mode MB) in processor $nxp$                       |

| V.44 Errors found in processor <i>nxp</i> while executing test <i>T2</i> (mode MB) V-44 |

| V.45 Total Error count for test <i>T1</i> (mode MD) in processor <i>nxp</i>             |

| V.46 Errors found in processor $nxp$ while executing test $T1$ (mode MD) V-46           |

| V.47 Total Error count for test $T2$ (mode MD) in processor $nxp$                       |

| V.48 Errors found in processor <i>nxp</i> while executing test <i>T2</i> (mode MD) V-48 |

| V.49 Total Error count for test <i>T1</i> (mode A) in processor <i>tfl</i>              |

| V.50 Errors found in processor <i>tfl</i> while executing test <i>T1</i> (mode A)       |

| V.51 Total Error count for test <i>T2</i> (mode A) in processor <i>tfl</i>              |

| V.52 Errors found in processor <i>tfl</i> while executing test <i>T2</i> (mode A)       |

| V.53 Total Error count for test <i>T1</i> (mode M) in processor <i>tfl</i>              |

| V.54 Errors found in processor <i>tfl</i> while executing test <i>T1</i> (mode M)       |

| V.55 Total Error count for test <i>T2</i> (mode M) in processor <i>tfl</i>              |

| V.56 Errors found in processor <i>tfl</i> while executing test <i>T2</i> (mode M)       |

| V.57 Total Error count for test <i>T1</i> (mode MB) in processor <i>tfl</i>             |

| V.58 Errors found in processor <i>tfl</i> while executing test <i>T1</i> (mode MB)      |

List of Figures xiii

| V.59 Total Error count for test T2 (mode MB) in processor tfl                           |

|-----------------------------------------------------------------------------------------|

| V.60 Errors found in processor <i>tfl</i> while executing test <i>T2</i> (mode MB) V-60 |

| V.61 Total Error count for test <i>T1</i> (mode MD) in processor <i>tfl</i>             |

| V.62 Errors found in processor <i>tfl</i> while executing test <i>T1</i> (mode MD) V-62 |

| V.63 Total Error count for test T2 (mode MD) in processor tfl                           |

| V.64 Errors found in processor <i>tfl</i> while executing test <i>T2</i> (mode MD) V-64 |

| V.65 Total Error count for test <i>T1</i> (mode A) in processor <i>sxs</i>              |

| V.66 Errors found in processor sxs while executing test T1 (mode A) V-66                |

| V.67 Total Error count for test T2 (mode A) in processor sxs                            |

| V.68 Errors found in processor sxs while executing test T2 (mode A) V-68                |

| V.69 Total Error count for test T1 (mode M) in processor sxs                            |

| V.70 Errors found in processor sxs while executing test T1 (mode M) V-70                |

| V.71 Total Error count for test T2 (mode M) in processor sxs                            |

| V.72 Errors found in processor sxs while executing test T2 (mode M)                     |

| V.73 Total Error count for test <i>T1</i> (mode MB) in processor <i>sxs</i>             |

| V.74 Errors found in processor sxs while executing test T1 (mode MB) V-74               |

| V.75 Total Error count for test T2 (mode MB) in processor sxs                           |

| V.76 Errors found in processor sxs while executing test T2 (mode MB) V-76               |

| V.77 Total Error count for test <i>T1</i> (mode MD) in processor <i>sxs</i>             |

| V.78 Errors found in processor sxs while executing test T1 (mode MD) V-78               |

| V.79 Total Error count for test T2 (mode MD) in processor sxs                           |

| V.80 Errors found in processor sxs while executing test T2 (mode MD) V-80               |

| V.81 Total Error count for test <i>T1</i> (mode A) in processor <i>vxk</i>              |

| V.82 Errors found in processor <i>vxk</i> while executing test <i>T1</i> (mode A) V-82  |

| V.83 Total Error count for test <i>T2</i> (mode A) in processor <i>vxk</i>              |

List of Figures xiv

| V.84 | Errors found in processor $vxk$ while executing test $T2$ (mode A)                 |

|------|------------------------------------------------------------------------------------|

| V.85 | Total Error count for test T1 (mode M) in processor vxk                            |

| V.86 | Errors found in processor <i>vxk</i> while executing test <i>T1</i> (mode M) V-86  |

| V.87 | Total Error count for test T2 (mode M) in processor vxk                            |

| V.88 | Errors found in processor <i>vxk</i> while executing test <i>T2</i> (mode M)       |

| V.89 | Total Error count for test T1 (mode MB) in processor vxk                           |

| V.90 | Errors found in processor $vxk$ while executing test $T1$ (mode MB) V-90           |

| V.91 | Total Error count for test T2 (mode MB) in processor vxk                           |

| V.92 | Errors found in processor <i>vxk</i> while executing test <i>T2</i> (mode MB) V-92 |

| V.93 | Total Error count for test $T1$ (mode MD) in processor $vxk$                       |

| V.94 | Errors found in processor $vxk$ while executing test $T1$ (mode MD) V-94           |

| V.95 | Total Error count for test T2 (mode MD) in processor vxk                           |

| V.96 | Errors found in processor vxk while executing test T2 (mode MD) V-96               |

# **List of Tables**

| 4.1 | Processor list                                                        | 15  |

|-----|-----------------------------------------------------------------------|-----|

| 6.1 | Modes for instruction generation                                      | 32  |

| 7.1 | Tabulation of Errors for test T1 (mode 'a') in processor kxmRISC621_v | 59  |

| I.1 | Manipulation Instructions[1, 2]                                       | I-1 |

| I.2 | Transfer Instructions[1, 2]                                           | I-6 |

| I.3 | Branch Instructions[1, 2]                                             | I-9 |

### **Forward**

The paper describes a configurable Random Instruction Generator developed as part of a larger Graduate Research project called **Project Heliosphere**. The overarching goal of Project Heliosphere is to develop a robust, configurable, verification and validation environment to further the study of various RISC processor architectures. The initial phase of this project was undertaken by Krunal Mange (Configurable Random Instruction Generator for RISC Processors), Namratha Pashupathy Manjula Devi (Configurable Verification of RISC Processors), and Thiago Pinheiro Felix da Silva e Lima (Reconfigurable Model for RISC Processors). Indeed I am proud, and humbled by the research work produced by this group of students.

Mark A. Indovina

Rochester, NY USA

17 December 2017

# Chapter 1

### Introduction

High quality verification by directed test-benches is a very difficult task to complete within limited time constraint. Directed test-benches with simulation will get the results quickly but may not cover areas outside the target, if a certain area is missed so are the bugs associated with it. Also directed test-benches do not accurately simulate the real world applications a processor might encounter. Random vector testing helps solve the problem faced by the directed test-benches as instructions are created at random which mimic real world application and if the verification is carried on long enough then it can be sufficiently said as verified. Another advantage of random vector testing is that bugs are found faster, because of the random nature even the bugs not thought of before can be found. The device under test (DUT) in this paper are either 12 or 14-bit in order execution processors which can be of Harvard or Von Neumann architecture. The goal is to build a flexible test-bench such that any of the configurations can be tested and can be scalable to even larger designs. The process is divided into 3 parts viz. random instruction generator, SystemVerilog test-bench and SystemC model. Random instruction generator will generate random instructions depending on the configuration specified in configuration file. Instructions, even though being random, should make sense in relation to spatially neighboring

1.1 Research Goals 2

instructions. Perl is chosen as the language to produce instruction because of its text processing abilities and other features like associative array, etc. Configuration file is also used by SystemC model to calculate expected output for the particular instruction. SystemVerilog is chosen for the test-bench because of its modularity and scalability. A change in test-bench will require only a change in a particular module of SystemVerilog test-bench rather than a complete overhaul.

#### 1.1 Research Goals

The goal of this work is to have a random instruction generator capable of generating instruction for variety of processor which are part of test set and have provisions for other designs. This objective is achieved as:

- Specify the basic requirements for the random instruction generator.

- Classify the processor design variations and come up with steps to create an instruction generator to span all the requirements.

- Incorporate user switches to generate specific category of instruction, which are stored in files compatible with processors and test-bench.

- Generate random instructions and verify two sample processor from set of eight processor, as proof of concept.

A script is also developed to collect data from all the test runs, tabulate the data and generate recommendations for debugging.

### 1.2 Contributions

The major contributions to the project Heliosphere are:

1.3 Organization 3

- 1. A fully functioning random instruction generator is built in Perl.

- 2. Error detection and correction for two processors (12 & 14-bits) is carried out by various tests to eliminate all the errors. These two processor samples are considered standard for the rest of the set.

- 3. Reused a part of instruction generator script to develop result database generator, which organizes and classify errors.

### 1.3 Organization

- Chapter 2: Research relating to the project outline and technology is presented in this chapter.

- Chapter 3: The test environment overview with brief introduction to each component is discussed in this chapter.

- Chapter 4: This chapter describes in detail processor architecture, instruction set and operation of the processors used in this work.

- Chapter 5: Configuration file structure along with description of each data field is explained.

- Chapter 6: Random Instruction Generator is described in detail in this chapter. This chapter

provides a brief overview of the design followed with explanation of design choices and

function descriptions.

- Chapter 7: This chapter describes the procedure to get results and gives explanation on how to interpret them. Explanation is supported by relevant data and graphs.

1.3 Organization 4

• Chapter 8: This chapter concludes the paper and discusses possible future work.

# Chapter 2

# **Bibliographical Research**

An important part of any research project is review current material related to the project specifications and the relevant search results used are discussed in this chapter. The tools needed for the development of intended work are one of the first material under research. The quest is to validate the feasibility of the tools meeting the requirement. After reviewing related work done with similar tools an affirmation is obtained and focus is shifted to the techniques/methods used to accomplish project in processor verification, model design and instruction generation. Languages such as SystemVerilog, SystemC and Perl are selected and used with verification tools by Cadence to accomplish the work.

Processor verification is an intensive task, especially given that increasingly complex designs can be designed and realized via state of the art manufacturing. In order to promote these designs, they must be verified for correctness. Writing test cases for such complex systems manually is quite challenging. If written to exhaustively check the system, this results in quite a large time overhead in realizing the necessary test cases [3, 4]. This is not suitable to market the product or use it in other project as the timeline is missed. This time penalty warrants automated test case generation, which form the basis of the work done in this paper. Various methods are used

to generate instructions/test-cases for processor verification viz. random instruction generation and randomizing a fixed set of test groups. The randomizing of the fixed set of test groups can yield better results if the design has medium complexity since writing all the individual cases will be increasing difficult. Directed manual tests have a short turn around time as they can be easily designed for a particular case. As discussed earlier this method is not suitable for exhaustive testing. Random Instruction testing is in stark contrast to manual testing in terms of setup time. A random instruction generator requires a greater amount of time as randomness in generation has to be constrained to bound tests within system design parameters and not generate meaningless cases while at the same time reaching corners. In order to have best of both worlds some methods researched use a novel way of randomizing part of a test case is done by making selection of opcodes from a table but making the operands randomized [5, 6]. This method gives a short setup time for the first test but will become time consuming as opcode table for all cases need to supplied.

Random instructions can reach all the possible states including the ones not thought by the test designer [7]. These tests when supplied with bias can give an acceptable coverage as against pure random tests [3]. Genetic algorithms are suggested and used in [8] to test a PowerPC architecture. This includes an execution trace buffer giving feed back to the bias generator, a better set of random instructions are generate which force corner cases. Paper [9, 10] discusses generating biases with respect to the instruction groups rather than each instruction to reduce complexity and get better coverage, which is similar to the work done in this paper. The user has capabilities of generating a group of instruction using mode selector discussed in 6.1 of this paper. A different way of generating random instruction is discussed in [11]; this method uses a Linear Feedback Shift Register (LFSR) to generate pseudo-random stream of bits which is given as input to the DUT after being verified as a legal instruction as it is possible to generate illegal instruction with this method. A work similar to [11] is described in [12] which uses graph theory

to estimate test length so that desired coverage is achieved without going overboard with test runs. Paper [13] carries the bias generation a step further with much more customization e.g. test length, instruction biases, memory maps, choice of directing tests to a particular processor element. All this customization helps target tests and also helps while debugging as only a particular area can be identified as a problem and thoroughly tested. The research affirmed the choice of using random instructions generator in this work, as it is versatile and can be automated to give superior testing time.

The test environment in this work is divided into three parts: generator, model and testbench. This structure is chosen as it is proven, and it can be argued that the generator and model can be combine together like in [14]. But combining the model and generator together introduces negative bias in both as they are dependent. Independently developing the model is more flexible and brings in robustness. The model is written in SystemC as it has the modularity and flexibility of software but can be used to model hardware, were as HDL (Hardware Definition Languages) can do a better job but sacrifice software features of classes, objects [15]. The model is considered as reference in verification and zero errors are expected from it. Various techniques to verify SystemC model are discussed in [16–18] viz. assertion based test, explicit state model test. The flow in verification is that the output of model is considered golden vector and compared to DUT's output, which depending on environment are generated and stored in a file or verified cycle by cycle. The final piece which ties all the parts together in test environment is the test-bench. The test-bench in this paper is developed in SystemVerilog. SystemVerilog is chosen for its versatile nature and re-usability and the test-bench developed in SystemVerilog is scalable as all the parts of the test-bench need not change to accommodate testing of new design [19, 20]. The structure of test-bench is divided as assertion, scoreboard, monitor, interface, driver [21]. Each part is a class and performs a job e.g. driver provides input vectors to the DUT, while scoreboard compare DUT values to golden vector [22]. The work discussed in the paper also tabulates results and produces graphs, an important observation made from research that presentation of result play equally important role as the testing work itself.

# **Chapter 3**

### **Test Environment**

The test environment houses all the components required for verification. Test environment is divided into three parts Random Instruction Generator (RIG), Model and Test-bench. Random Instruction Generator is written in Perl v5.20 and generates set of instructions in accordance to specifications of the device (processor) under test (DUT). Model is built in SystemC and its function is to generate reference outputs. Test bench is written in SystemVerilog and checks DUT output for errors. Figure 3.1 shows the block diagram of the system.

Testing/verification starts with the configuration file. The tester or owner of DUT populates the information fields in the file depending on the specs. Configuration file in itself is not a functional unit but provides information, viz. processor architecture, register size, number of registers, mnemonic-opcode pair, etc. useful for functioning of the three components. The configuration file is explained in Chapter 5. The RIG generates an instruction set which is read by both the model and test bench. The Model produces ideal outputs and the test bench compares DUT outputs to model's and reports errors if any.

The test environment has eight test samples which are mix of 12 or 14 bits, and Harvard or Von Neumann architecture. Two DUT samples are corrected to have no errors which assisted in

Figure 3.1: System Block Diagram

the building of test environment and is proof of concept. After all the simulations have run, the Report Database Generator (RDG) program cleans and arranges the report in final presentation format.

### 3.1 Random Instruction Generator

RIG is the first to run. It extracts information from configuration file and reports of any errors in file information. This error reporting helps so that syntax errors are avoided. Depending on information extracted viz. processor architecture, bits, etc, instructions are generated as one or two memory files. For Von Neumann architecture only one memory file is generated with memory size in accordance to configuration file specifications. Whereas for Harvard, two files, instruction & data memory file is created as shown in Figure 3.1. The number of instructions are controlled by the user, if no input is associated with instruction number then a 1000 instruction size is default. RIG also has features which protect against a number of instructions larger than possible to fit, limit number of branch instruction so that the stack doesn't overflow, exception prevention as the DUT's tested could not handle exceptions like divide by zero. Instructions generated can be a mix of all instruction types or any combination like data manipulation, branch - data manipulation, etc. This flexibility eases bug finding as efforts can be focused on a particular instruction type. Since RIG calculates the result of instructions generated to prevent exceptions and control other parameters it also generates files with registers values. The result files aid in environment building as one more checkpoint in testing as extra test vectors.

3.2 Model 12

### 3.2 Model

The model is built to emulate the processors under the test and is written in SystemC. The model configures itself with the data extracted from the configuration file. Model takes instruction file/s generated by instruction generator and calculates the results. Model writes out the register values in files for each register. Model also generates files with program counter values, which helps test-bench determine if the DUT's flow of execution long is correct, and status flag values. Model checks for exceptions as second safety check after RIG and other errors in instructions if any. Output files generated are input to test-bench as shown in Figure 3.1. The outputs generated by model are compared to the DUT outputs by test-bench [23].

### 3.3 Test-bench

The test-bench does the verification and reporting of error after simulation. test-bench is written in SystemVerilog due to its modular nature [24, 25]. test-bench is the only common interface between different parts of environment and DUT. The test-bench receives instruction files from the generator and provides stimulus viz. clock, instruction input. This is done by instantiating DUT in test-bench. The test-bench then monitors the output from the processor under test and compares it to the output produced by model and instruction generator as shown in Figure 3.1. Simulation is stopped as soon as an error is detected, a report with expected values for that instruction along with registers values for a set number of instructions is generated. The information about past results help in debugging if the error is in the current instruction or has it stemmed from previous instruction/s. After simulation the result are fed to RDG which complies results and produces tidied report along with 'csv' file with error density of each instruction and potential issues with that particular instruction. This helps in plotting graphs making it easier to interpret the results. test-bench is comprised of environment, test, test case, interface, driver.

DUT resides in the test module. Driver provides stimulus and interface provides data interface between modules. As discussed earlier, the modular nature helps as complete test-bench need not change with change in DUT, this makes it robust and easier to maintain [2, 24]. A Perl script was written to generate the test-bench depending on specs in the configuration file.

### 3.4 Report Database Generator

RDG is written in Perl v5.20. After required simulations have been ran, RIG creates various logs and reports listing error instruction and other relevant data useful in debugging. The report has opcodes and it is difficult to visually interpret the data. To resolve this RDG inserts in a comment stating mnemonics for the opcodes and makes other changes to make the report more visual. RDG also complies frequency of errors and possible cause from the test-bench report, this data is written to a CSV file making it easier to plot graphs and observe data. RDG is based on RIG as information extraction from configuration file is the same.

RIG is discussed in the paper. Model and test-bench are part of collaborative work to develop the configurable test environment for verification of RISC processors.

# **Chapter 4**

### **Processor Architecture**

The RISC processors used in the work are developed as part of course EEEE621 - Design of Computer Systems supervised by Dr. Patru at Electrical Department, Rochester Institute of Technology in Fall 2015. The specification were unique to each student according to number assigned. All the processors were originally developed in Altera's Quartus Prime using Verilog or VHDL.

### 4.1 Overview

The processor architecture overview is seen in Figure 4.1. It contains Memory Unit, Registers and Arithmetic & Logical Unit (ALU). Input/Output peripherals are memory mapped to the highest 16 locations. The processors are classified into two types viz. Harvard & Von Neumann architecture. Further sub classification is done on basis of the Instruction Word (IW) size which can be 12 bits or 14 bits wide. Table 4.1 lists all the processors used in the work with their major specifications.

4.1 Overview 15

Figure 4.1: Processor Architecture Overview

Table 4.1: Processor list

| Processor name   | Architecture type | Instruction word size | No. of registers | Status reg. size |

|------------------|-------------------|-----------------------|------------------|------------------|

| paRISC621pipe_v  | Harvard           | 14                    | 16               | 8                |

| kxmRISC621_v     | Von Neumann       | 12                    | 8                | 12               |

| vxkRISC621_v     | Von Neumann       | 14                    | 16               | 8                |

| axtRISC621       | Von Neumann       | 12                    | 8                | 12               |

| tflRISC621_v     | Harvard           | 12                    | 8                | 12               |

| dnm_RISC621_v    | Harvard           | 14                    | 16               | 8                |

| dxpRISC521pipe_v | Harvard           | 14                    | 16               | 8                |

| nxpRISC621pipe_v | Von Neumann       | 14                    | 16               | 8                |

4.2 Registers 16

### 4.2 Registers

Registers are used in various operations are performed and they also hold results. Depending on instruction word size, the number of registers is limited as bits required to access them are constrained. All data manipulation instructions have registers as operands and for write back/storage. A 12-bit processor has a 3-bit register field giving eight registers (R0 - R7) whereas a 14-bit processor has a 4-bit register field giving sixteen registers (R0 - R15). A design exception is made for the 12-bit design in flow-control instruction that register1 (operand1) size is limited to 2-bits making 4 registers usable. This is done in order to accommodate four flag bits while still having the same number of opcode bits.

### 4.3 Arithmetic & Logic Unit (ALU)

ALU is host to mathematical, logical operations, and functional unit. For most of the processors used, mathematical operations and logical operations like shift, rotate, OR, etc are written by the designer. Whereas multiplication and division operation are used as a unit which is generated using Quartus's IP wizard. The ALU in the processors used is not designed to handle exceptions e.g. divide by zero. Functional unit houses temporary registers for both input and output. Input operands are held in temporary registers TA and TB which can indicate register used or can hold constant depending on the instruction. Outputs after an operation are held in temporary registers TALUH and TALUL to hold upper half and lower half of the result respectively. Number and types of operations are same across all processors except that data size handled can be different.

4.4 Memory Unit

### 4.4 Memory Unit

The Memory Unit is monolithic for Von Neumann design as both program and data memory reside in same memory space. Harvard design on the other hand uses separate memory space for program and data memory. An advantage of Harvard design is that both program and data memory can be accessed simultaneously. This helps when the instructions are pipelined to increase throughput. Section 4.6.1 discusses pipeline in detail. The memory units used are generated using Quartus's IP wizard. In case of Von Neumann architecture design, initialized ram is used. Initializing ram is required because program and data memory share space and the program needs to be loaded before start of operations. The registers like Program Counter (PC), Stack Pointer (SP), MAeff (Effective memory register) are also a part of memory unit as seen in Figure 4.2. Program counter keeps track of instruction to be fetched and is incremented every cycle except for a stall in pipeline. MAeff is calculated as addition of MAB (Memory Address Base register) and MAX (Memory Address Index register). MAB holds the address offset and MAX holds index which depends on an addressing mode used in a particular instruction [1]. Stack pointer points to top of stack and is incremented or decremented depending on direction of growth. Stack in this work is defined as percentage of memory, it is made even in size by Random instruction generator as Flow control instruction occupy two location on stack. MAeff is register not available to user, it holds the address to the location in the memory from which data can be loaded or stored or jump location. The organization of stack is seen in Figure 4.3.

Input/Output (I/O) peripherals are memory mapped for both the architecture types. The highest 16 locations in memory (data-memory for Harvard) are assigned to I/O peripherals. The peripheral assignment in I/O memory is user defined. A generic memory structure is as shown in Figure 6.3 the table represents Von Neumann architecture but Harvard is also similar with an exception that it has separate program memory.

4.5 Instruction Set

Figure 4.2: Memory organization

### 4.5 Instruction Set

The size of opcode restricts the number of instructions possible. The processors tested in this work have a 6-bit opcode field giving a maximum of 64 instructions. The actual number of instructions implemented is smaller than 64. Addressing modes define how the data is fetched or stored. For the processor used in the work operand1 (Ri) signifies addressing mode. A value of '0' in the field of addressing mode indicates direct addressing mode that the offset address present in next instruction word is the address to either jump, load or store. A value of '1' indicates, the final address is addition of program counter value and offset address. The rest of the values possible for operand1 field represent register addressing mode. In register addressing mode the final address is calculated as addition of value present in register (pointed by value of operand1) and address offset. The instruction set is classified as follows.

4.5 Instruction Set

Figure 4.3: Stack Organization

4.5 Instruction Set

### **4.5.1** Manipulation Instructions

Manipulation instructions modify data in registers. They are used to perform mathematical and logical operations. They can be further divided in to types i.e. two operand instructions and one operand plus a constant type instruction. Instruction word format for manipulation instructions is as seen in Figure 4.4. As seen in Instruction Word format register Ri is operand1 and stores result as well, Rj is second operand which can be a register or a constant value.

Figure 4.4: Instruction word format for manipulation instructions (a) 12-bit and (b) 14-bit processor [1]

### 4.5.2 Data Transfer Instructions

Data Transfer Instructions transfer data to and fro between registers and memory. Since operations are register based they are likely to be loaded with value from the memory at start of program and when a value in memory is required. These instructions are also helpful when number of values being held are greater than number of registers, memory here provides temporary storage for the value. Instruction word format for data transfer instructions is as seen in Figure 4.5. The offset address is stored at next memory location and is denoted as IW1 where IW0 would represent the data transfer instruction. Depending on type of addressing mode, IW1 can be the address of location itself or has to be added to Rj register value to obtain final address.

4.5 Instruction Set

Figure 4.5: Instruction word format for data transfer instructions (a) 12-bit and (b) 14-bit processor [1]

#### 4.5.3 Branch Instructions

Branch instructions help skip or go to a different section of a program. 'JUMP' is a branch instruction which helps skip/jump over set number of instruction forward or backward depending on the condition. If the condition is met the jump is taken whilst if the condition is evaluated to be false, program continues sequentially. The conditions in 'JUMP' instruction are set using conditional flags. Carry (C), Negative (N), Overflow (V), Zero (Z) are four flags used as the conditions. With four one bit flag eight unique conditions plus an additional condition when all the flags are reset. When all four flags are reset then 'JUMP' is unconditional and is taken.

'CALL' and 'RET' (return) are grouped together and are unconditional branch instructions. Call instructions is used to execute a subroutine which is stored after program memory or other part of program memory. Subroutines make programs neat as a piece of code to be executed multiple time need not be replicated at the usage, instead call can be made to the piece of code. Another use possible is to call a exception handling routine. As exception can occur sporadically they cannot be incorporated in main program but stored else where in memory and be executed by call the routine. Branch instructions except 'RET' have IW1 like data transfer instructions. And the address to call routine or jump is calculated using IW1 and Rj register value depending

on addressing mode. 'RET' doesn't have IW1 or address offset as it functions to return flow of program back to caller i.e. to instruction before which call was made. 'RET' instruction restores the values of PC and flag values stored by CALL instruction on stack during its execution. Instruction word format for branch instructions is as seen in Figure 4.6 and 4.7.

Figure 4.6: Instruction word format for JUMP and CALL (a) 12-bit and (b) 14-bit processor [1]

Figure 4.7: Instruction word format for RET (a) 12-bit and (b) 14-bit processor [1]

All the instructions part of processor architecture are listed in appendix I and are grouped by instruction types.

# **4.6 Processor Operation**

Processor Operations are carried out in machine cycles. Machine cycle is a part of overall operation carried out as per instructions. An instruction operation is considered to be comprised of four parts: instruction fetch, decode, execute and write back in the processors part of the work. These four operations are called machine cycles. Instruction fetch is machine cycle 0 (MC0)

which fetches the first and next new instructions from memory pointed by program counter. Program counter has single increment after every fetch. All the fetches from the memory need not be instructions as depending on type of instruction second instruction word can be memory offset. Instruction decode is machine cycle 1 (MC1) in this cycle depending on instruction opcode (i.e. after identification of instruction) operands are loaded with values from register or constant values. It is in this step that the values loaded in operands can be forwarded from previous instruction to resolve dependencies. Detailed explanation of dependencies is in section 4.6.1 Pipeline Theory. Instruction execution is machine cycle 3 (MC2) where the result for the instruction is calculated. The calculated result is stored in an internal temporary register ready to be written back in next cycle or forwarded if required. Write back is machine cycle 4 (MC3) and is last machine cycle marking end of an instruction cycle. Here the calculated result is either stored in the memory or the register depending on the instruction.

Processor operation is divided into machine cycle to facilitate pipelining of instruction which is similar to a product assembly line. Pipelining increases throughput of processor by utilizing resources efficiently.

### **4.6.1** Pipeline Theory

Pipeline comes from assembly line used in automobile manufacturing. In manufacturing if a person does all the steps by himself, the steps are performed in sequence and steps ahead have to wait for previous ones to complete. Hence a job with 'm' distinct parts with each part taking 'n' amount of time will take a total of 'mn' time without pipeline. In the same example if we have 'm' people doing an individual task then for first whole job to complete it'll still take 'mn' amount of time. But after first complete job the next job will be completed in 'n' amount of time. This is because after completing first step first person can start working on second job's first part while second person is working on second part of first job. This goes so on and so forth such that

when nth person is working on nth part of first job, the first person is working on first part of nth job. In processors machine cycle replaces a person in completing job i.e. instruction execution. The time taken to fill the pipeline which in example meant first person doing first part of nth job is taken only once if the pipeline is not stalled. Here in processor, a stall can occur when the processor is waiting for an instruction to complete which uses memory and in consequence the memory cannot be accessed. This is a problem especially with Von Neumann architecture as there's a single memory unit and both read-write operation cannot happen at same time. This is an example of structural dependency where multiple instructions try to access same resources. Structural dependencies are solved by stalling the execution of next instruction until resources become available. If there is change in flow of program then the pipeline is reset i.e. flushed. Flushing means completing last instruction before branch instruction then continuing on from new address location where pipeline needs to be filled again. Hence a pipeline is useful when program don't have many branch instructions and such programs appear more often than ones with lots of branches which is why most modern processors use pipelining[26, 27].

A sample example of pipeline is as seen in Figure 4.8.

|   | Instruction   | Result          |  |  |

|---|---------------|-----------------|--|--|

| 1 | XOR R7, R7;   | R7=0;           |  |  |

| 2 | XOR R6, R6;   | R6=0;           |  |  |

| 3 | NOT R7;       | R7=0xFFFF;      |  |  |

| 4 | ADDC R6, 0x3; | R6=0x3;         |  |  |

| 5 | CPY R7, R6;   | R7=0x3;         |  |  |

| 6 | MUL R7, R6;   | R7=0x0; R6=0x9; |  |  |

Figure 4.8: Sample example for pipeline

The example contains six instructions and it takes nine cycles to complete execution. The number of cycles is nine because it takes three cycles to fill the pipeline, six cycles to execute and three trailing cycles to complete remaining instruction execution. Fetch cycle is performed at every clock event and hence not considered as a cycle on its own. Detailed machine cycle for entire execution is seen in Figure 4.9. As seen in sample program, first two instruction reset values in register six and seven. Instruction number three (NOT instruction) which begins at third machine cycle has decode and operand fetch at next cycle but the first XOR instruction has not yet written back the value to R7.

| MC    | 1      | 2       | 3       | 4       | 5        | 6        | 7       | 8       | 9      |

|-------|--------|---------|---------|---------|----------|----------|---------|---------|--------|

| P-IC  | XOR-IC | XOR-IC  | NOT-IC  | ADDC-IC | CPY-IC   | MUL-IC   | -       | -       | -      |

| P-MC0 | XOR-IF | XOR-IF  | NOT-IF  | ADDC-IF | CPY-IF   | MUL-IF   | -       | -       | -      |

| P-MC1 | -      | XOR-OPF | XOR-OPF | NOT-OPF | ADDC-OPF | CPY-OPF  | MUL-OPF | -       | -      |

| P-MC2 | -      | -       | XOR-EXE | XOR-EXE | NOT-EXE  | ADDC-EXE | CPY-EXE | MUL-EXE | -      |

| P-MC3 | -      | -       | -       | XOR-WB  | XOR-WB   | NOT-WB   | ADDC-WB | CPY-WB  | MUL-WB |

| D/H   | -      | -       | -       | RAW     | -        | RAW      | RAW     | -       | -      |

Figure 4.9: Pipeline stages

This creates a data dependency and it's of the type Read After Write (RAW) as NOT instruction can read the data only after XOR does write back. This can be resolved by a stall in pipeline, but elegant way of handling this is data forwarding. Data forwarding implies that required data is brought to the required register even before the previous instruction completes write back. With this pipeline continues without a stall. Other dependency example is of Copy instruction. During machine cycle six when 'copy' instruction is in decode cycle it requires data of R6 value for which is being calculated. So data is forwarded from ALU to the register before write back cycle even begins. Other types of data hazards are Write after read (WAR) which occur when instruction over-writes data which is need by one of the previous instruction which needs old data to complete it's execution and Write After Write (WAW). WAW occur when two instructions write data to same register, this happens when instruction are out of order in execution in reference to their issuance.

In the example with six instruction and four cycles each so the program would have taken twenty-four cycles to complete. But with pipeline and no branch it is completed in nine cycles. The speedup of program can be calculated as [total time taken without piepline] / [total execution time with pipeline] [1]. In the example taken the speedup is 24/9 which is 2.66.

Chapter 5

**Configuration File**

The configuration file is key to the test environment. It contains information to setup test bench,

generate test instructions and for model to do calculations. The configuration file is populated

from the specification sheet of DUT or by the supplier of the DUT. All the numeric values are

specified in the hexadecimal format except for the percentage value. The following information

is contained in the file:

**name\_folder:** This field gives directory name in which the files for a particular processor reside.

This is relative address to the directory test bench and resides one level below.

name: Name of the processor under test, helps locate the highest level file in directory. This

name is also used to generate instruction file, logs and reports under same name which

aids accessibility when testing multiple DUT's.

bits: Size of instruction word for the DUT and is also the size of the registers. In the tests done

this is also the size of data bus and has two variants 12 bits and 14 bits.

**registers:** The number denotes the number of registers available to be used in instructions.

- **architecture:** Two types of architecture viz. Von Neumann & Harvard are indicated as, '0' & '1' respectively. This helps generator decide whether to generate a single or separate program & data memory file.

- **opcode\_size:** Size of the field dictates number of maximum possible instruction mnemonics.

Also helps in generating instruction word and decoding in model.

- **operand1\_size & operand2\_size**: This denotes the operands max size. For register-register instructions it gives register number used, it also can denote constant value if second operand is constant. For the flow control instruction in processors used, Ri (operand 1) is calculated as: (Instruction-word size) (4 + opcode size).

- **dm\_size:** This field only applies to Harvard architecture as it has separate data space. The memory length is calculated as (2^dm\_size).

- **memory\_size:** Total memory size available is indicated by this filed and calculated as (2^memory\_size). For Von Neumann architecture this gives available size of program & data memory combined.

- **pc\_in\_pc\_relative:** This information is useful in operations using program-counter(PC) relative addressing mode. DUT design allows relative address to be calculated with respect to current or next instruction address. A '0' indicates current instruction's address is used while '1' indicates next instruction's address is used.

- **SP & Stack\_direction**: Top of stack is given by this value. Stack direction indicates the growth of stack i.e. where next element is stored. '0' indicates that the elements are stored from lower to higher address whereas '1' indicates elements stored from higher to lower memory address. The highest the stack can grow or started at is (total memory 16 highest

locations), this is due to the fact that 16 locations are reserved for Input/output Peripherals (I/O-Ps) which are memory mapped for processors tested.

**Stack\_size:** It is percentage of total memory available, in case of Harvard its w.r.t data memory size. The size is made even as usual push on stack is two words for the processors tested.

Mapping: Mapping of mnemonics is done before specifying opcode value for given mnemonic. Mapping is done between delimiters 'start\_mapping' & 'end\_mapping'. This allows the test environment to be DUT independent in naming the instruction mnemonic and be flexible in handling various designs. The mnemonics on the left are associated with DUT and the ones on the right are environment specific which are fixed for to be used by instruction generator.

**opcode:** Here the opcodes relative to the mnemonics are to be entered. Opcodes are divided into three categories data transfer, manipulation & branch instructions each has its delimiter so that the instruction generator can identify different instruction and generate tests with different combinations of instruction types.

clk\_st: This value suggests number of clock cycles taken to fill the pipeline or the clock at which first output is obtained. This is particularly useful for test bench to set reference to compare model's output to DUT's for testing purposes.

#### **DUT** files:

- name\_pm: This file gives the name of program memory used by DUT. This file is present

in both Harvard & Von Neumann architecture. For the latter its both program & data

memory.

- name\_dm: Data memory used by only Harvard type DUT.

**30**

• name\_div: Divider used by the DUT.

• name\_mul: Multiplier used by DUT.

• name\_cnt: Counter used by DUT.

• All these files are used by the processor under test to run and perform its operations suc-

cessfully. These are also required by the test bench to list in compilation file so that the

environment instantiate or brings in correct file for to run test.

del\_ld & del\_st: This field provides information about whether load & store instructions are

stalled. '1' indicates stall after the instruction and '0' indicates no stall. This is used by test

bench to make result comparison at correct time clock. In usual case only Von Neumann

architecture requires stalls as instruction and data are in same memory which introduces

one clock cycle latency. Design of Harvard architecture can also stall if designer chooses

to do so.

**EOF:** End of file delimiter.

Example configuration file is shown in Appendix II.

# Chapter 6

# **Random Instruction Generator**

RIG generates instructions used for verification and also writes the values of registers to the file. Instructions generated at random help find bugs quicker as the tester need not manually think of combinations. The ability to test with random instructions improves on the test case generation time, if done manually. Hence from early stages of verification bugs or errors in implementation can be found speeding up the turn around time. Random instructions can also test cases which were not thought of if done manually. Manually testing all cases is both labor and time intensive process. With multiple runs of verification, coverage close to 100 percent can be achieved with help of the random instruction generator. The general flow of random instruction generator is shown in Figure 6.2.

### **6.1 Random Instruction Generator Overview**

The RIG is written in Perl v5.20. Perl has powerful text manipulation capabilities while syntax is similar to C. Text processing helps in retrieving data from configuration file and in writing instruction data, register values to file. The text formatting in file is also easier. The instruction

perl gen\_vt.pl -config filename -mode mode\_type

Figure 6.1: Command to generate random instructions

Table 6.1: Modes for instruction generation

| Mode | Instructions                                                                           |  |  |  |

|------|----------------------------------------------------------------------------------------|--|--|--|

| a    | All three types of instruction are generated viz. manipulation, data transfer & branch |  |  |  |

| m    | Only manipulation instruction are generated                                            |  |  |  |

| mb   | Manipulation and branch instruction are generated                                      |  |  |  |

| md   | Manipulation and data transfer instruction are generated                               |  |  |  |

generator is made configurable so that as the input configuration changes, it adapts to it. To achieve this robustness the instruction generator is kept modular and the calculations are kept generic and depend on the input configuration file. The instruction generator also has built in error reporting. If the input configuration file has error in input data syntax or is missing data field then the user is notified of such error with prompts on how to fix the errors. The command to run the instruction generator is seen in 6.1:

The minimum input requirement is a configuration file 5, as it contains all the vital information to proceed with the instruction generation. The other input parameters are number of instruction and 'mode'. RIG can generate user defined number of instructions. The default value for number of instruction is 1000 in this work, to ensure that even without being supplied with number of instruction the RIG works. The input of 'mode' is to compare generating a certain type of instructions, table 6.1 describes 4 modes. The flow of RIG is seen in Figure 6.2. The process begins with extracting information from configuration file done by Extract function. The information extracted gives memory limits and information on segments inside memory like stack, I/O space. With the processor architecture known the next function, 'memory\_set', knows about memory being only data or with program memory as well. So the 'memory\_set' func-

Figure 6.2: Flowchart for instruction generator

6.2 'extract' Function 34

tion sets the memory limits for next functions to continue the operation. The 'filler' function fills the memory with zeros in locations which will contain data later on as the instructions are generated. It also fills memory locations with ones which are not written on by generator. The 'gen' function is responsible for generation of instructions. It does so by calling sub-functions viz. manipulation\_gen, data\_transfer, branch. Instructions generated are written to the file by the 'writeout' function. 'reg\_out' function does the task of writing out values of registers to file to be used by testbench. The functions shown in Figure 6.2 are discussed in detail in following sub-sections.

### 6.2 'extract' Function

The 'extract' function takes the configuration file as an input and extracts all the information about a particular processor. All the values inside the configuration files are hexadecimal, while calculation in RIG are in decimal. Hence all the values are converted into decimal. The values are extracted line by line from the configuration file. Any line beginning with '#' is considered a comment and is ignored. All the configuration file reside in the 'configuration' directory which is one directory level below the RIG. All the extraction of information is done via Regular Expressions (regex) [28]. The regex match and extract a part of a string depending on the criteria given. Mapping of instruction and opcode for mnemonics are written between delimiters e.g. for data transfer instructions 'start\_data\_transfer:' and 'end\_data\_transfer:' are the start and end limiters respectively. The delimiters helps in determining a section of data and hence the sections can be in any sequence in configuration file. Absence of either opening or closing delimiter causes an error so that errors in configuration file are avoided. 'EOF' marks the end of file and it is indicator to stop reading data.

# 6.3 'memory\_set' Function

The 'memory\_set' function sets up the memory. The function first calculates the maximum memory from the information in configuration file. The value of field 'bits' from the configuration file is taken as power to base 2 to calculate maximum memory possible from that bit size. Here in this work memory for a processor is calculated with its bit size. For Von Neumann architecture only one memory with the calculated size is created, whereas for Harvard architecture two memory with same size are created to serve as program and data memory. But the random instruction generator has provision to support user defined memory which can be smaller or greater than calculated memory size. This custom memory size can be supplied for both program and data memory, if present.

The stack is given as percentage of total memory size or data memory size for Harvard type processors. While calculating memory locations to be reserved for the stack care is taken that the value is even. An even value is chosen as instructions like CALL (branch instruction) use two stack locations one for storing flags and program counter value. To verify the supplied number of instructions can be generated reserved memory is calculated. If the space in memory after subtracting reserved space is greater than desired number of instruction only then RIG proceeds further. In case of instruction number exceeding the memory space available a warning is reported along with the memory space available and execution of generator is carried with maximum memory space possible. Reserved memory is calculated as addition of stack memory, I/O space if memory mapped, subroutine space, data space in case of Von Nuemann architecture and two additional memory locations. The subroutine space in this work is 40 memory locations but can be changed. Data space is reserved in case of Von Neumann type processors so as to allow instruction to write and read from memory location which would be impossible to do if instructions occupied all the space. This reservation is not required in Harvard architecture as

6.4 'filler' Function 36

there is separate data memory. Two memory location are reserved as those locations contain one's stored which serves as end of program for testbench at which simulation can be stopped and is completed. At the end of this function memory space is divided accordingly and instructions can be generated. A typical memory layout for Von Neumann type is shown in Figure 6.3.

### 6.4 'filler' Function

This function serves as building error checking in memory while generating instructions. It fills the arrays with character 'k' which hold data to be written to memory to both program memory and data memory or just to one memory in case of Von Neumann architecture design. The character is chosen at random and it is written as visual aid. Since no address value or opcode at the location will have character 'k' it helps catch error in generated instructions if any. Later on during write out to file this helps in filling memory space with ones where 'k' is found. The locations with ones as data, can be address offset if preceded by a associated valid instruction opcode. At other locations a string of ones mean that the location is not defined. Also this string of ones can help detect branch error when the instruction word reads a string of ones instead of a valid instruction.

### 6.5 'gen' Function

The 'gen' function is the largest function written. It is responsible for generation of instructions and also prevention of exceptions as the processors in this work exclude exception handling. The 'gen' function is also made modular so that the development and maintenance in future is relatively easier. The instructions are randomized in this function. The mnemonic and opcode of instruction is stored as hash table by 'extract' function. A random opcode from a set of hash

Figure 6.3: Memory Organization

keys is selected via 'shuffle' function which is part of Perl's 'Util' library which contain general purpose subroutines. The 'gen' function is also responsible for generation of a certain set of instructions depending on user input, with 'a', i.e. all instructions, being the default option. A set of only branch or data transfer instructions is not generated as branch instructions need some instructions to branch to. And just branching the flow of execution will not reveal any dependency error which are caused by other instructions when in a combination with branch instructions. Similarly data transfer alone will not yield much information about errors, as reading or writing garbage value cannot be verified if the same arbitrary value is written and read back again. Hence both branch and data transfer instructions are paired with manipulation instructions to provide data to read or write as well as good variation for dependency check when branching. The ability to generate instructions with only certain desired types help in debugging a desired part of the processor design as errors reported will be exclusively from the desired types of instructions. The function is also intelligent to detect if a branch is to an undefined location. In such event branch operation is skipped and replaced with one of the manipulation operations. The data transfer is not chosen in case of an invalid branch because even data transfer from that location will be undefined. After choosing a random instruction 'gen' calls sub-function to generate manipulation, data transfer or branch instructions.

### 6.5.1 'manipulation\_gen' Function

This function to generates manipulation instructions and calculates results for the generated instruction. This function then applies another layer of randomization by randomly selecting registers for the operation. In case of an instruction with constant as the second operand, the register number generated for operand2 still applies as the field size is same. After calculating result of instruction flags need to be set according to the result. The flag assignment is done by 'CNVZ' function, a function is chosen as its functionality is needed by all the instruction and hence it

prevents code duplication. Another function 'compactor' resizes the result to fit the width of instruction word of a particular processor. The resizing of the result is required for certain instructions as the entire result is not stored to destination, some information is contained in flags. An example of such result resizing is adding two 12-bit operands in a 12 bit processor yields a 13-bit result of which the most significant bit (MSB) is carry. Thus result is clipped to 12-bits while 'CNVZ' function already has carry information. The last function to be called to generate opcode for the instruction generated is 'iw1\_gen'. The 'iw1\_gen' function generates instruction word in format specified by configuration file for a processor. The opcode (instruction word) generated is stored in an array later to be written in memory. Other information stored is resultant register values.

### 6.5.2 'data\_transfer' Function

The 'data\_transfer' function also generates random values for the operands. In the case of data transfer instructions, i.e. LOAD & STORE, operand1 represents the addressing mode. Operand2 is the source or destination of data when the operation is STORE or LOAD respectively. The data transfer instructions are two instruction words wide for the processors under the test. The first instruction word which defines the instruction is followed by the address offset. The final address is obtained as an addition of the address offset and base register address (MAB). The base register address is defined by the addressing mode which is the value of operand1. A value of '0' represents direct addressing mode which implies that the final address is equal to the value of address offset. A value of '1' represents PC relative addressing mode and the final memory address is calculated as sum of PC value and address offset. The values from two onwards to the highest number specified by operand1 field (e.g for 12-bit processor it is 7) represents register addressing mode. The final address is equal to the value held by the register. To generate the offset address, RIG generates a random number in valid memory range as the final address. Then